Bergeron演示了一個臉部識別和視線跟蹤應用的幻燈片,其通過采用針對賽靈思全可編程器件的Xylo....

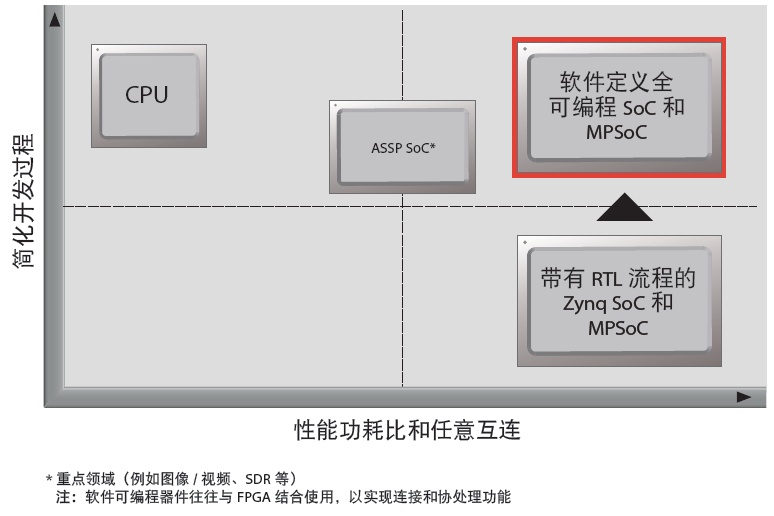

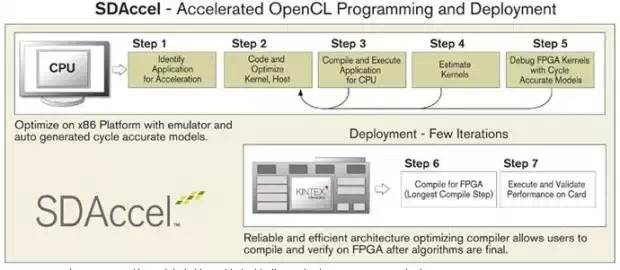

有這樣一個讓人糾結的問題。FPGA具有優越的性能和良好的功耗,但怎么樣讓那些不精通VHDL或者Ver....

找到目標后,可以利用max_fanout來限定其扇出值,讓工具在實現過程中復制驅動端寄存器來優化。如....

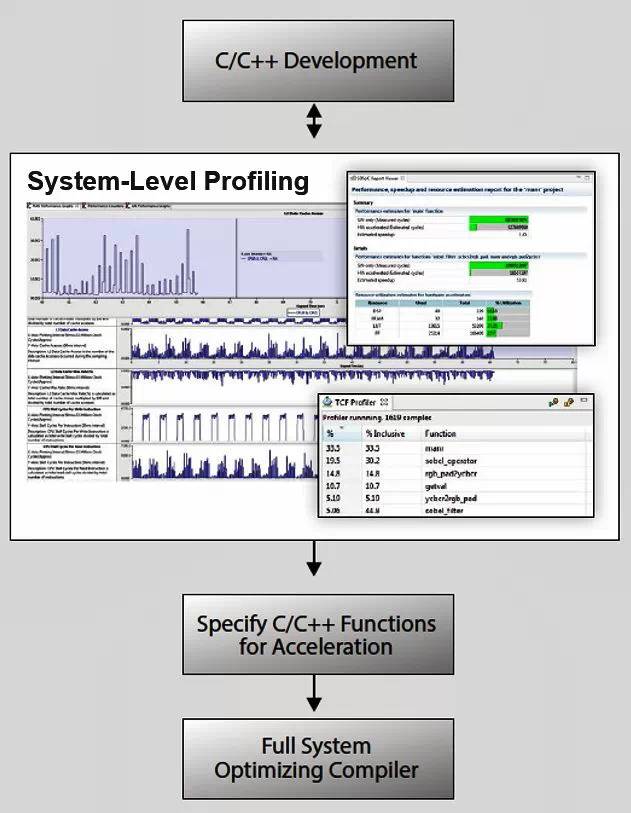

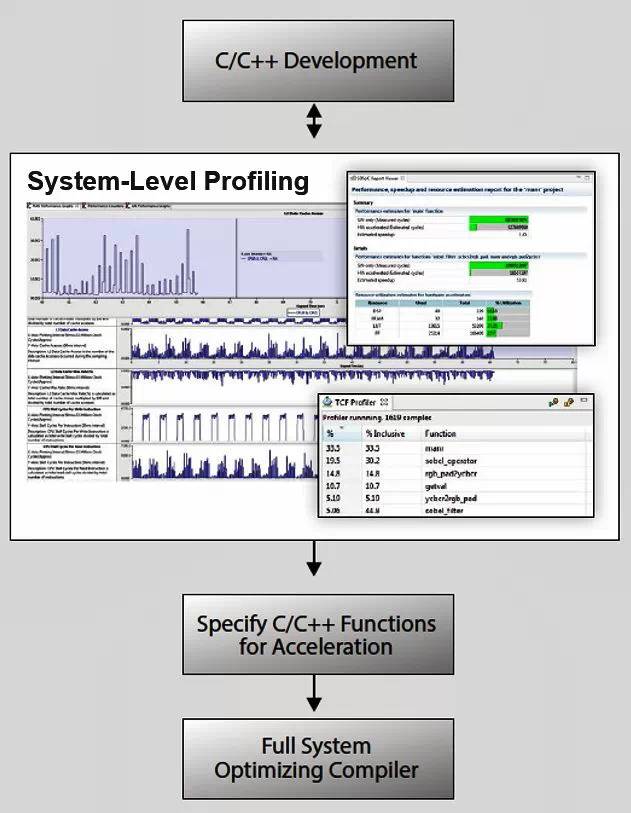

SDSoC開發環境可提供高度簡化、類似ASSP C/C++的編程體驗,包括簡便易用的Eclipse集....

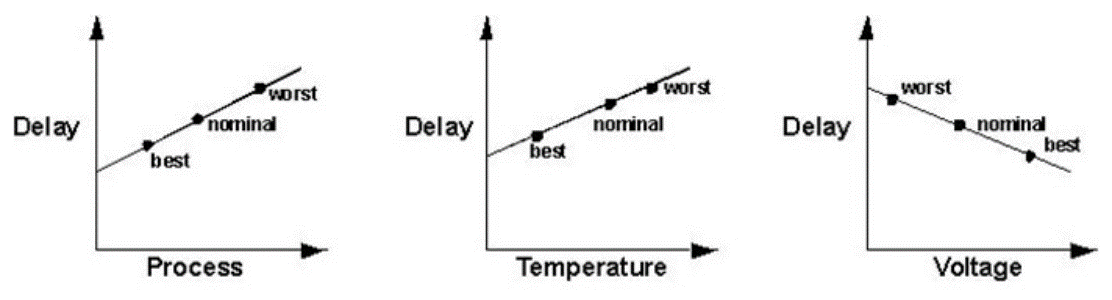

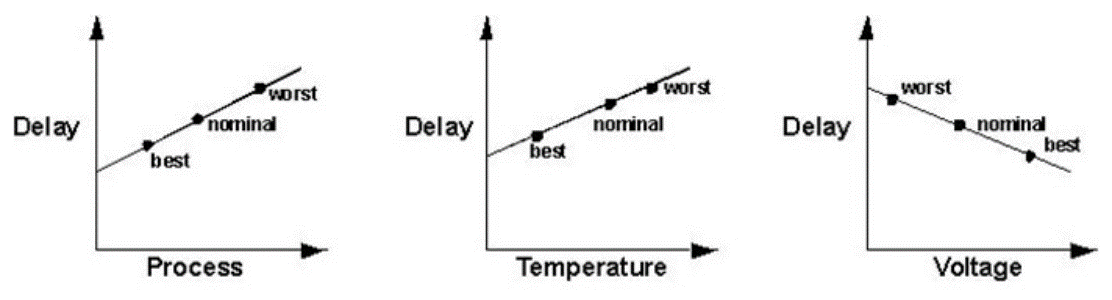

即便是同一種FF,在同一個芯片上不同操作條件下的延時都不盡相同,我們稱這種現象為OCV(on-chi....

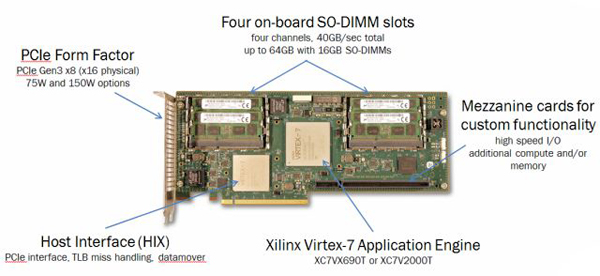

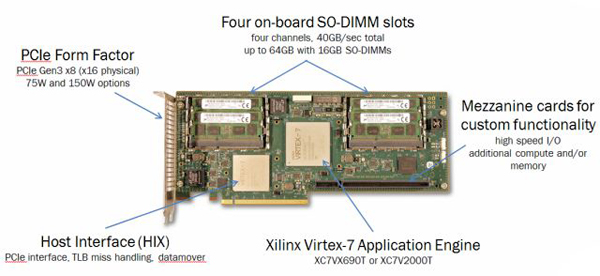

價格Price,功耗Power,性能Performance是工程優化的“3P標準”,假如一個基于PC....

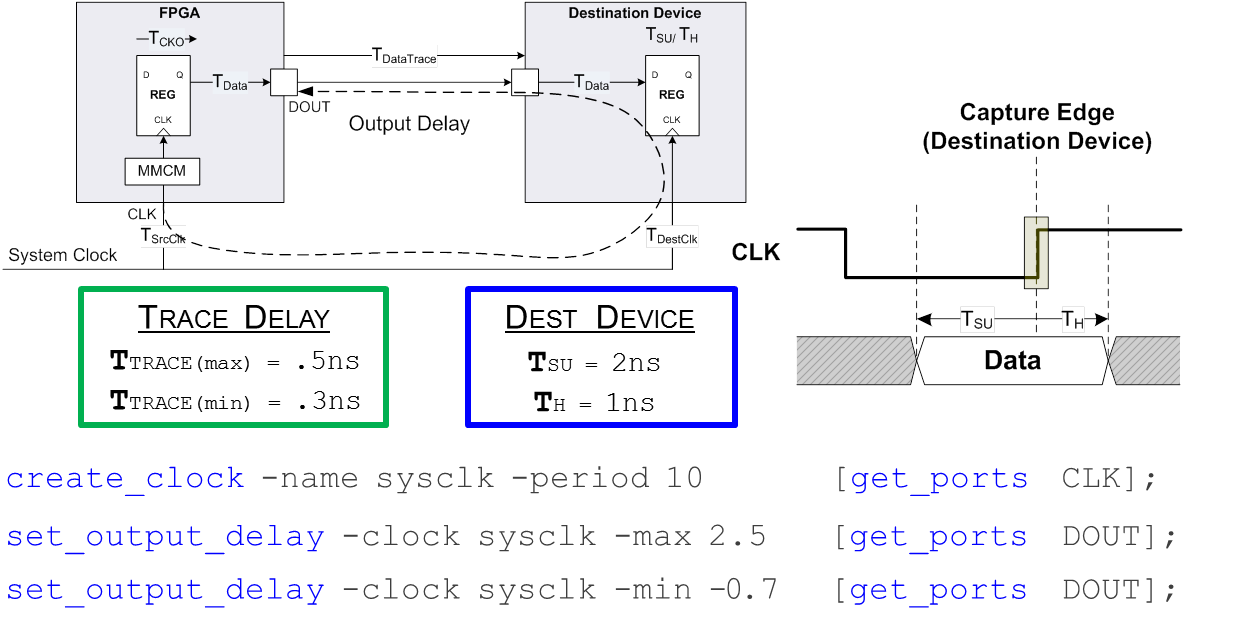

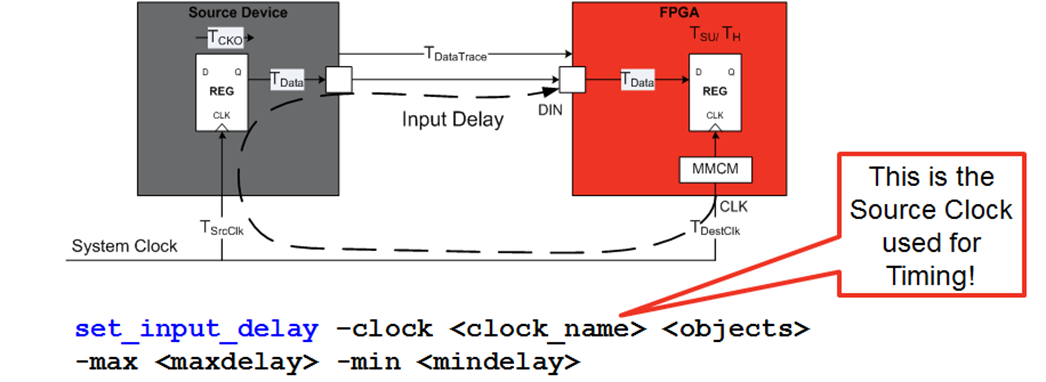

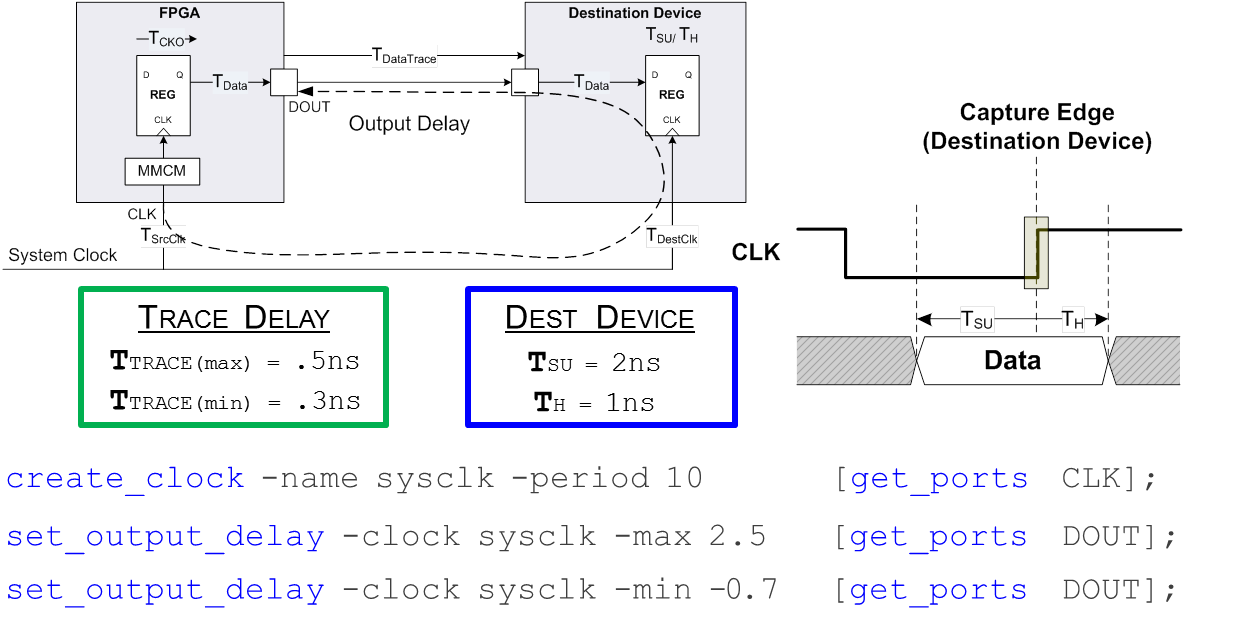

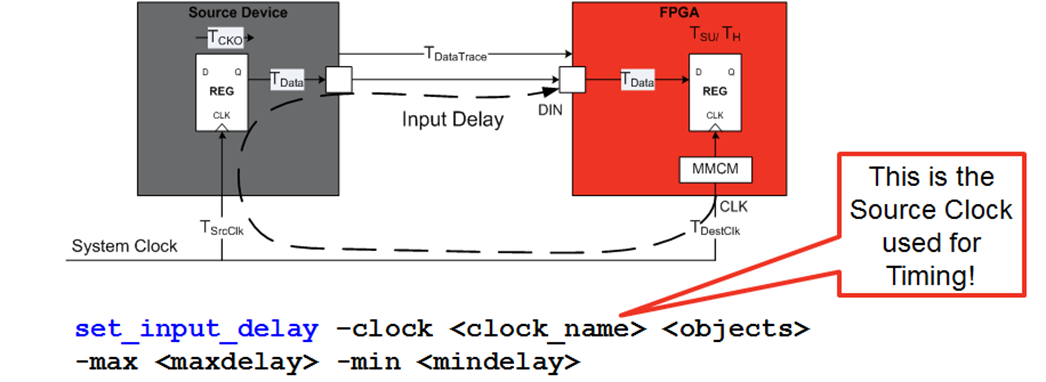

DDR接口的約束稍許復雜,需要將上升沿和下降沿分別考慮和約束,以下以源同步接口為例,分別就Setup....

可以這樣計算輸入接口約束:DDR方式下數據實際的采樣周期是時鐘周期的一半;上升沿采樣的數據(Rise....

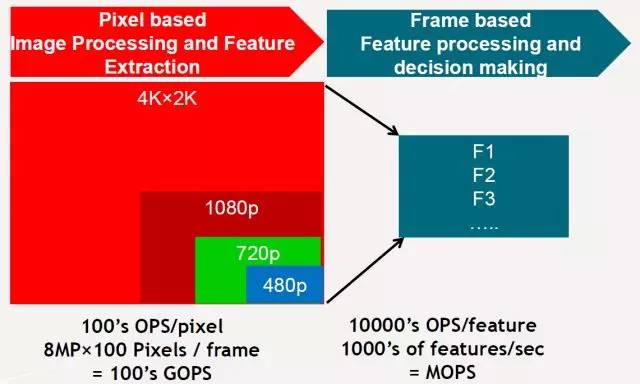

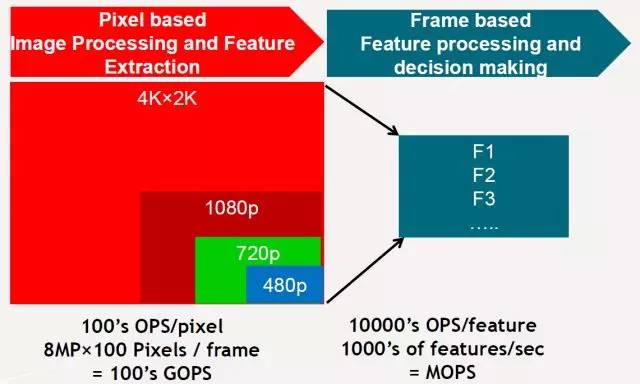

高度集成的All Programmable SoC通過將圖像/視頻處理、分析、傳感器接口和高速機器視....

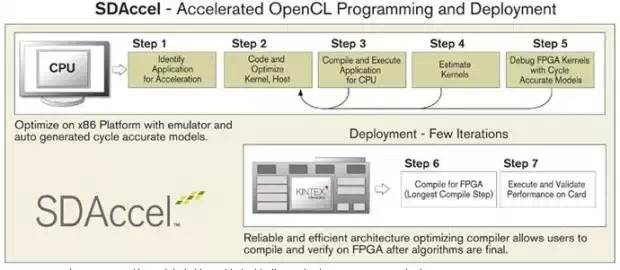

然后全系統優化的編譯器自動將系統編譯為一個完整的軟件或者硬件系統。同時也會生成可編程邏輯比特流文件和....

提供 10 x 10mm 的小型創新封裝選項,滿足小尺寸攝像機要求,無需 PCB 微過孔即可實現。

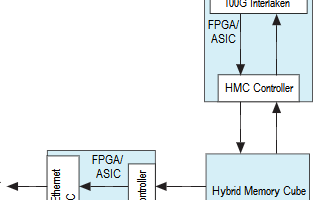

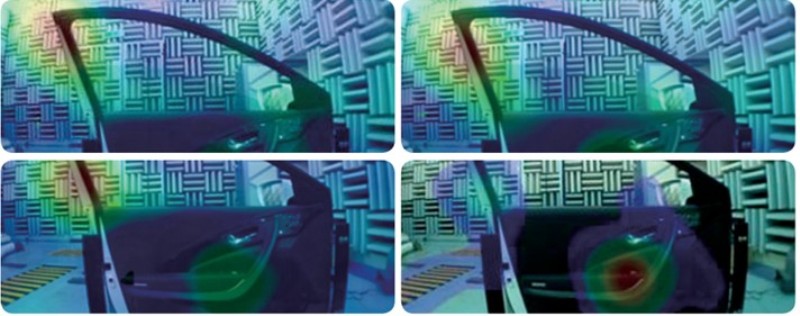

BEEcube公司董事長兼伯克利無線研究中心聯合創始人Bob Brodersen博士指出:“5G可將....

憑借該產品組合,賽靈思能滿足各種下一代應用需求,包括LTE Advanced 與早期5G無線、Tb ....

FPGA 設計包含越來越多的 IP 數量,如此前使用的內部 IP、Xilinx FPGA IP 或第....

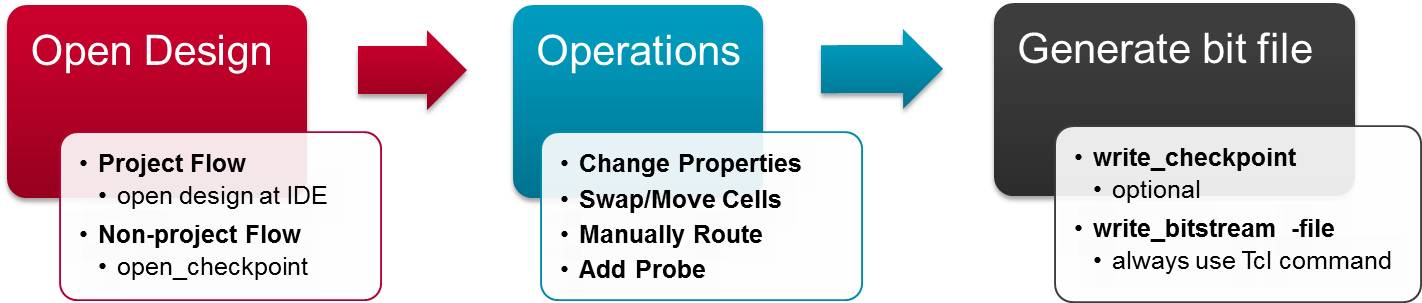

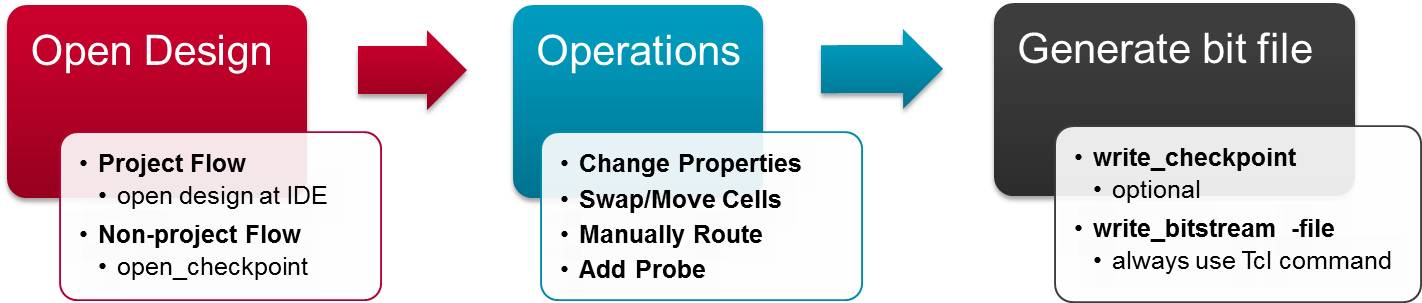

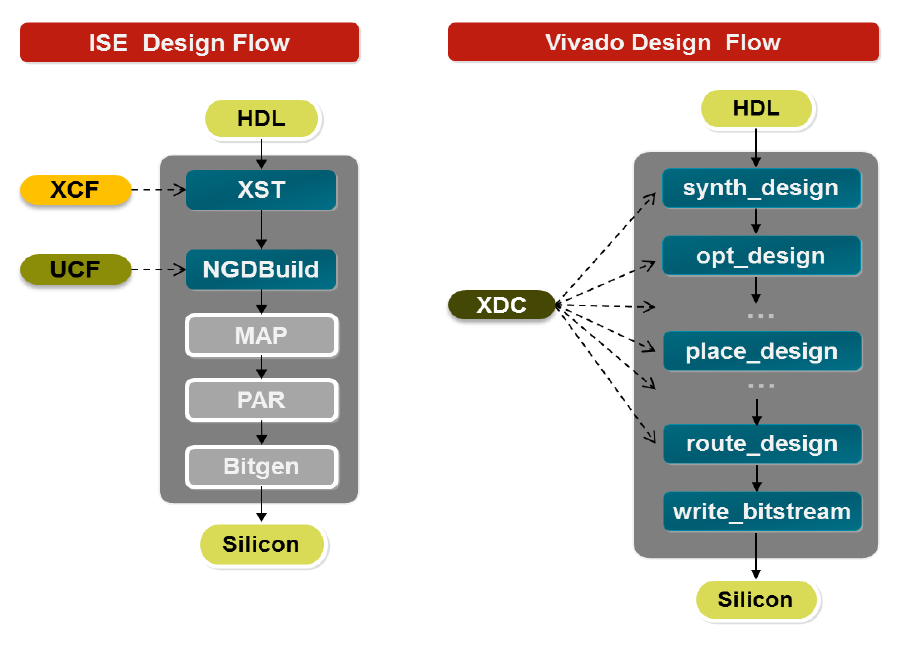

第一步所指的Design通常是完全布局布線后的設計,如果是在工程模式下,可以直接在IDE中打開實現后....

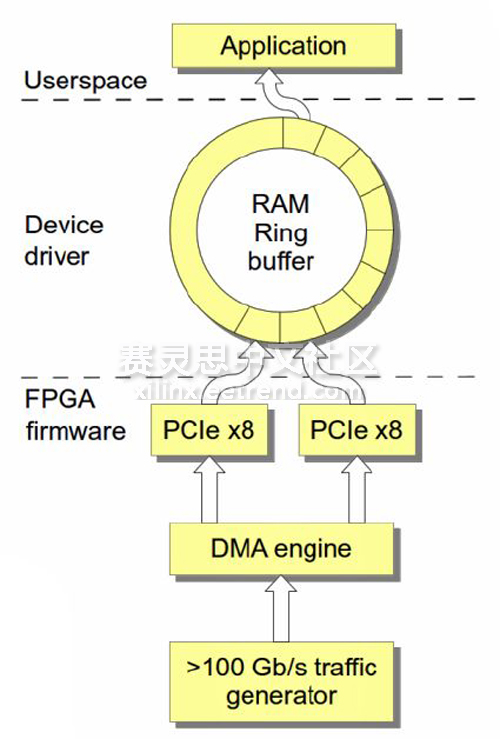

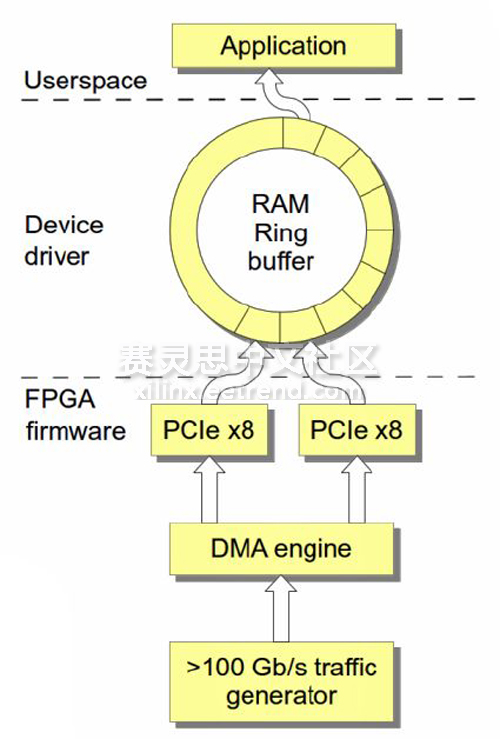

CESNET和INVEA-TECH進行了一系列實驗來展示PCIe分岔的好處。測試程序包括裝載一塊賽靈....

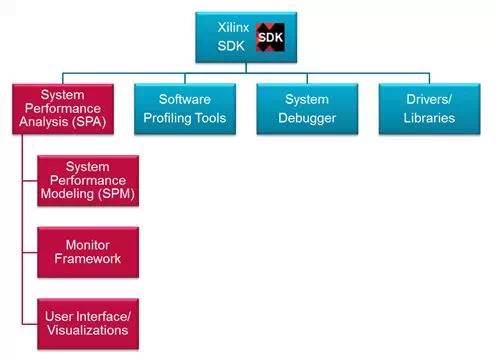

如果您要進行這種類型的分析,AXI流量生成器正是您需要的那種儀器。在您的團隊將系統硬件設計到Zynq....

賽靈思公司亞太區銷售與市場副總裁楊飛表示,賽靈思的SDx系列仍會持續發展。毫無疑問,這會幫助賽靈思面....

以前加速器應用設計主要使用硬件描述語言(HDL)例如Verilog來進行程序設計。這就需要專門的技能....

如果還按照篩選,我要在1ms內把一大堆數據放到一起篩選,一個方法就是在它的所謂的控制器里再加上過濾邏....

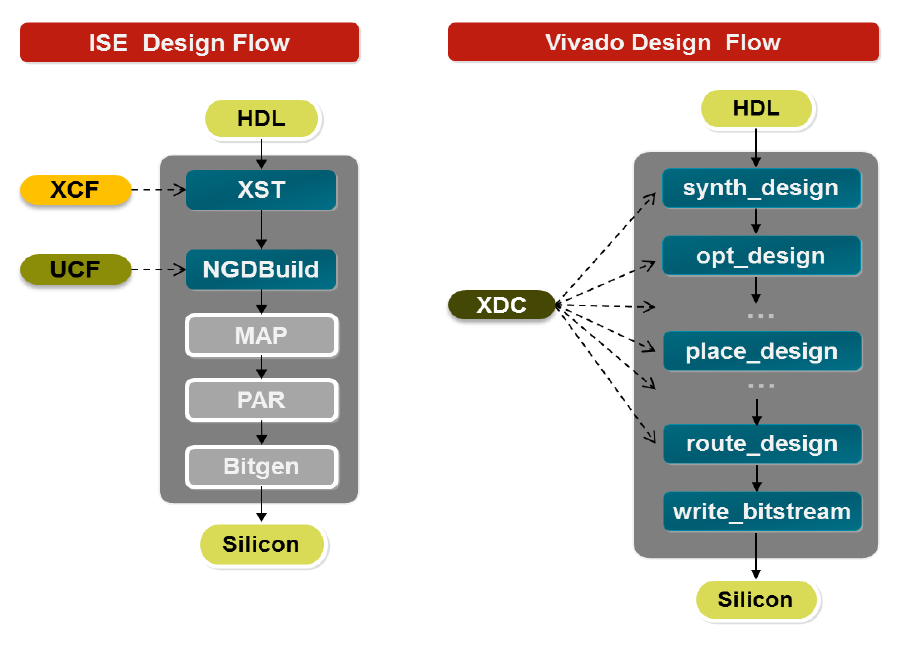

工程模式的關鍵優勢在于可以通過在Vivado 中創建工程的方式管理整個設計流程,包括工程文件的位置、....

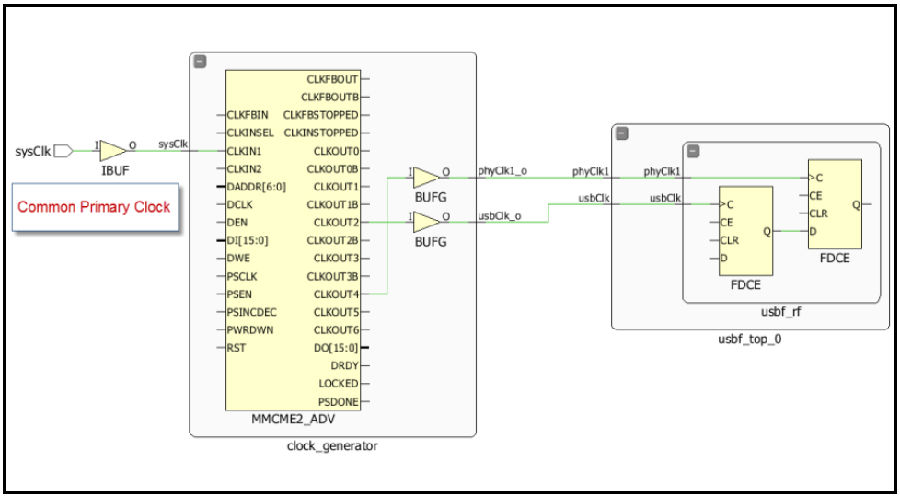

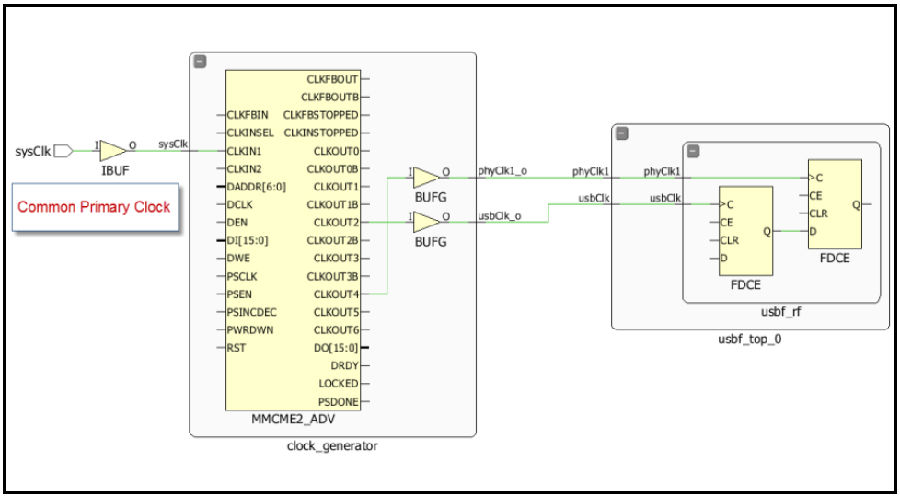

建議的做法是:首先,對“Common Primary Clock”排序(顯示為Yes 或No),這么....

其中,-include_generated_clocks 表示所有衍生鐘自動跟其主時鐘一組,從而與其....

云計算中,賽靈思所扮演的角色不僅僅是加速計算,還包括加速存儲和聯網,賽靈思估算其5年內目標市場容量可....

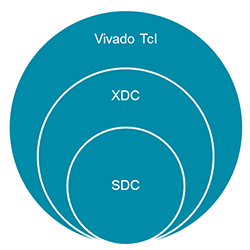

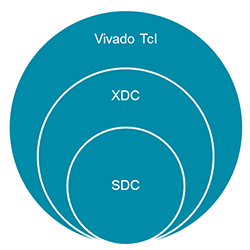

實際上Tcl的功能可以很強大,用其編寫的程序也可以很復雜,但要在Vivado或大部分其它EDA工具中....

上述結果可以通過通信鏈路以健康狀態的形式進行傳送,保存在非易失性存儲器之中,例如,flash或FRA....

二十世紀四十年代發現了超導體電熱平衡性及其測量入射電磁能量的功能,但是TES探測器直到二十世紀九十年....

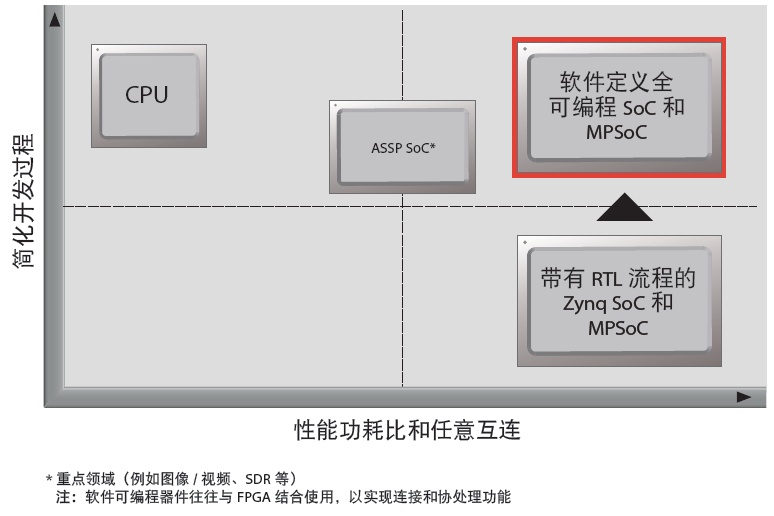

現在讓我們看一下平臺電子產品巨頭公司采取哪些措施來提高其盈利能力;Zynq SoC為何遠優于ASIC....

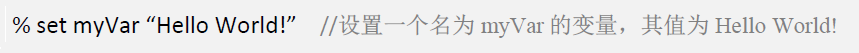

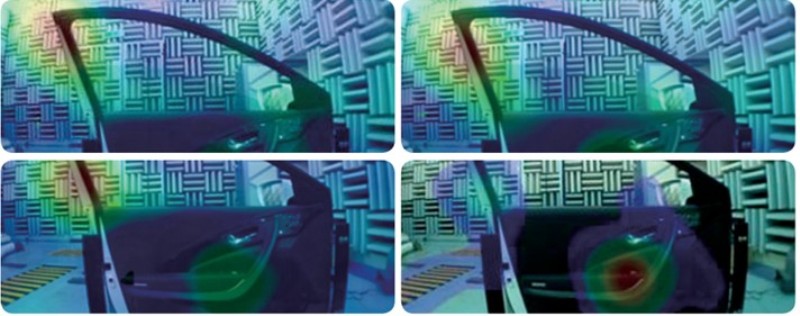

。第一,要想捕捉瞬變的噪聲,快速的響應時間是非常必須的,因為大部分噪聲的產生是不規律的,變化快速的。

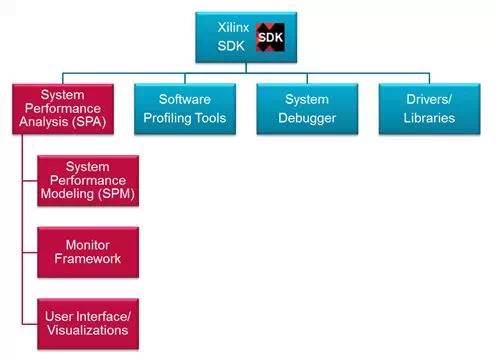

軟件優化是一個復雜的話題。Qin表示,要實現最佳硬件性能,必須同時使用所有這些技術,并在它們之間取得....