在半導體領域,“摩爾定律”可謂是無人不知、無人不曉。可以說在過去幾十年,半導體產業在摩爾定律的推動下高速發展。但是現在,隨著晶體管縮放尺寸逐漸逼近物理極限,半導體工藝制程的推進也越來越困難,“摩爾定律”已死的聲音也開始不絕于耳。不過,即便如此,科學界也依然希望通過一些新的技術來繼續推動摩爾定律的前進。

“摩爾定律”已死?

摩爾定律是由英特爾創始人之一的戈登·摩爾(Gordon Moore)于半個世紀前提出來的。其內容為,“當價格不變時,集成電路上可容納的晶體管的數目,約每隔18-24個月便會增加一倍。”

自摩爾定律提出之后的幾十年,整個半導體產業也確實按著摩爾定律在持續快速的前進,但是自28nm之后,摩爾定律便開始呈放緩態勢,其所帶來的經濟效益也開始降低。

雖然去年上半年臺積電的7nm工藝已經量產,而且5nm也已經在路上,接下來3nm甚至是1nm或許仍然還有路可以走,但是這毫無疑問將會更加的困難。

而更為令人悲觀的是,雖然隨著工藝的提升,晶體管密度還可以進一步增加,但是能夠帶來的性能提升或功耗的降低卻越來越少。比如從28nm到16nm,面積縮小了40%,速度提高了30%-40%,但是如果選擇提升速度,那么功耗就沒法降低多少。而在28nm之前,每一代制程工藝的升級,功耗都能夠降一半多,面積降一半多,速度提升一倍多。但現在,這樣的好事情已經一去不復返了。

除此之外,隨著工藝制程從10nm向7nm、5nm、3nm、1nm的繼續演進,所需要付出的代價也更具高昂。摩爾定律所帶來的經濟效益(即在價格不變的情況下,每兩年性能提升一倍甚至更多)也將會不復存在。

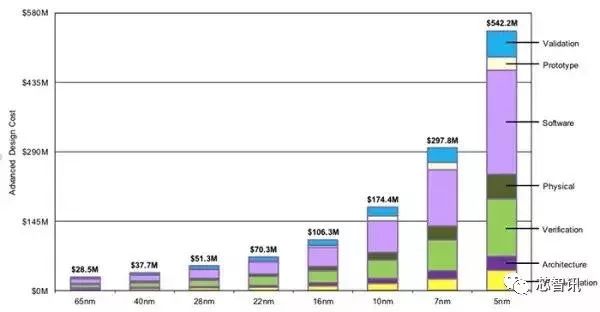

此前,國外Semiengingeering網站曾發布過一篇工藝和芯片開發費用的文章。文中指出28nm節點的芯片開發成本為5130萬美元;16nm節點則需要1億美元;7nm節點需要2.97億美元;5nm節點,開發芯片的費用將達到5.42億美元;由于3nm還處于最初期的開發階段,所以其開發成本至今還難以確定,3nm的開發費用有可能超過10億美元。

此外,先進的晶圓廠建設同樣需要大量的現金支持,以采用最新的設備來提升工藝制程,這將進一步拉高芯片的制造成本。比如7nm之后的5nm就必須要用到最新的EUV極紫外光刻技術,而目前全世界僅有ASML可以供應EUV***,而且一臺EUV***的售價就高達1億多美元。

顯然,隨著制程工藝的不斷逼近物理極限,不僅在技術實現上越來越困難,所需要的設備越來越復雜,而且芯片開發成本也急劇增長,如果芯片廠商沒有足夠的實力,芯片出貨沒有足夠的出貨量,將很難承擔高昂的成本。

全新的“自組裝”技術

在“摩爾定律”的推進越來越困難,甚至“摩爾定律”已死聲音越來越多的當下,包括英特爾在內的眾多半導體企業也紛紛寄希望于通過“內核架構創新”(比如采用非馮·諾伊曼系統架構)、芯片工藝由原來的2D轉向2.5D/3D堆疊、自旋電子、神經元計算、量子計算等方法來繼續推進“摩爾定律”的經濟效益。

對于以上的這些新技術可能大家或多或少都有了解和接觸過,而在去年在德國舉辦的TED演講當中,來自美國的研究人員Karl Skjonnemand為延續“摩爾定律”提出了一種全新的思路,即利用“分子工程和模擬自然的方法”來實現晶體管的“自組裝”(self-directed assembly),從而極大的降低半導體制造的成本。

▲根據資料顯示Karl Skjonnemand目前是美國的一家專注于未來的芯片制造開發所需先進的納米材料公司的技術總監,他擁有20年亞太、歐洲和美國項目管理經驗。

而在介紹“晶體管自組裝”技術之前,我們有必要先來了解下,傳統的半導體制造工藝流程。

那么相對于傳統的半導體制造工藝,所謂的晶體管的“自組裝”技術又有何優勢呢?

Karl Skjonnemand認為,在傳統的芯片當中,晶體管的微型結構特征有非常多都是重復的,是一種高度周期性的結構。因此,他想在替代技術中利用這種周期性,他想采用自組裝材料,自然的組建周期性結構,來構建晶體管,讓這些材料來完成精圖案的制作,而不是試圖在已經越來越困難的圖案投射技術上突破。

自組裝原理在大自然中隨處可見,比如我們的脂質膜到細胞結構,再到DNA能夠復制,并且一代代的遺傳下去,就是一種自然組裝技術。因此,Karl Skjonnemand認為,自組裝技術可以應用到芯片制造當中。

他介紹了一種名為“嵌段共聚物”(block copolymer)的自組裝材料(一種有機半導體)——由兩條長度只有幾十納米的聚合物鏈條,但是這些聚合物鏈彼此排斥。可以將它們強制組合在一起,在系統中創造一種“嵌入式窘組”。而一塊不大的材料,可包含幾十億這樣的聚合物鏈,相似的化合物粘結在一起,同時互斥的化合物則會相互分離。這些化合物四處移動,直到變成一個特定的形狀。

Karl Skjonnemand表示,天然的自組裝形狀是納米級的,有規律和周期性,還很長,這就是我們在晶體管排列中所需要的,重要的是,它們能夠提供比傳統晶體管蝕刻更為精細的細節。

所以我們可以利用分子工程來設計不同的尺寸和不同的形狀,以及不同周期性的不同形狀,比如說,我們選擇一種對稱分子,他的兩條聚合物鏈長度相似,則自然的自組裝結構就是長的曲線形,像指紋一樣,指紋線的寬度和間距,不僅取決于聚合物鏈的長度,還取決于系統內部窘組的級別。

我們還可以創造更復雜的結構,如果我們使用非對稱分子,其中一條聚合物鏈顯著短于另外一條。在這種情況下,短鏈就會在中間形成一個牢固的球,被包裹在更長的相互排斥的聚合物鏈當中,形成一個自然的圓柱體。這個圓柱體的尺寸,及圓柱體之間的距離和周期性,取決于我們選擇的聚合物鏈的長度以及內嵌窘組的水平。

換句話說,利用分子工程,可以獲得自組裝的納米結構。這些結構可以是線形的,圓柱形的,同時也符合我們設計的周期性。我們利用化學工程來制造晶體管所需的納米級特征,但是具備了自組裝這些結構的能力,只解決的一半的問題,因為還需要排列這些結構,使得晶體管可以形成電路。

對于這個問題,Karl Skjonnemand表示,可以使用寬導向結構來固定自組裝結構。將他們錨定到位,使得剩余的自組裝結構可以平行排列,從而與我們的導向結構保持一致。比如我們想做一個精細的40nm長的線形,對于傳統的投射技術是非常困難的。我們可以先制作一個120nm的導向結構,使用普通的投射技術,這個結構將會把3個40nm長的線形排列在一起。使得這些材料可以自動的進行最復雜的精細復寫。

不過,這其中依然有著其他的挑戰,比如,整個系統都需要完美的排列。因為結構中任何微小的缺陷都會導致晶體管的失效。所以需要利用化學清洗的方法來消除納米級別的最小失誤。

“自組裝”何時能走向商用?

其實,在Karl Skjonnemand之前,已經有很多的科研機構嘗試將自組裝技術應用于半導體芯片制造,并且近幾年也取得了一些突破。

早在2012年,比利時的微電子研究中心(IMEC)就在自己的工廠里安裝了世界上的首個自組裝生產線。在那里,科學家改進材料和設計,減少自組裝結構的誤差。

此外,紐約州立大學也在阿爾巴尼(Albany)的納米尺度工程中心(Center for Nanoscale Engineering)里運營著一條自組裝的生產線。

在2014年的Semicon West半導體行業會議上,IMEC的流程技術研發副總裁安·斯特更(An Steegen)就曾表示,自組裝技術看起來可以作為極紫外光刻法的替代方法,延長現有光刻法的壽命。IMEC現在可以用自組裝技術設計出和英特爾最新的芯片相似的結構,尺度可小至14納米。斯特更當時表示,自組裝技術有望替代EUV技術。

紐約州立大學納米尺度工程中心納米工程副教授克里斯托弗·波斯特(Christopher Borst)在Semicon Westl論壇上也曾表示,其生產線現在可以可靠地產生重復的線條和鰭狀結構,可以精細到18nm。“我們制造了一些讓人印象深刻的結構,”波斯特說。“這種方法在材料和制造能力上已經沒問題了。”

2016年初,美國國家標準與技術研究所(NIST)與IBM的研究人員開發了一種溝槽(trenching)技術,能被用以通過定向自組裝來打造半導體芯片。顯然,這種溝槽技術與前面Karl Skjonnemand介紹的用于打造自組裝半導體芯片所需的“導向結構”作用類似。

在2017年,來自麻省理工學院和芝加哥大學的一群研究人員就宣布聲稱已經找到了一種方法,可以開發出更窄的線寬,并可望能應用在標準的大規模經濟型生產設備中,而這種方法就是利用了“自組裝”技術。

麻省理工學院的副教務長兼化學工程教授Karen Gleason表示,現在,先進的芯片工藝通常需要非常昂貴的極紫外光(EUV)光學技術,或是通過掃描芯片表面的電子束或離子束建立逐行掃描影像,這些方法都過于緩慢且昂貴。

麻省理工學院的研究人員提出的方案是,首先使用目前已被大量采用的光刻技術,用于在芯片表面上產生線路圖案。而后使用“嵌段共聚物”的材料層,會自然地分離到交替的層或是其他通過旋涂溶液形成的可預測圖案。嵌段共聚物是由兩種不同高分子聚合物形成的鏈狀分子。

“兩個嵌段的尺寸可確定在沉積時將自行組裝的周期層尺寸或其他圖案。而后一個保護性的聚合物層會被放置在嵌段聚合物上,通過化學氣相沉積(chemical vapor deposition,CVD)的方式完成這一過程。這個過程是一大關鍵,它對嵌段聚合物的自組裝造成約束,迫使其形成垂直層而非水平層,底層的光刻圖案將引導這些層的定位,但共聚物會自然地導致其寬度要比基線的寬度更小。同時由于頂部聚合物層還能圖案化,因而該系統可用于建立更加復雜的圖案,如微芯片的互連。”

麻省理工研究人員表示,目前大多數芯片都使用現有的光刻技術,CVD本身很容易理解,因此實施新技術會更加簡單。不需要改動設備,使用的也都是熟悉的材料。

而在2018年,香港中文大學化學系繆謙教授研究團隊發明了具有獨特自組裝結構的有機半導體材料,設計合成了帶有不同功能基團的六苯并苝衍生物,并在其晶體結構中發現了一種罕見的分子堆積方式。這些六苯并苝衍生物具有扭曲的共軛骨架,在晶體中形成獨特的磚砌結構,保持基本相同的二維π-π堆積模式而不受各種功能基團的影響。同時,繆謙教授研究團隊還在此基礎上結合有機薄膜晶體管與微流管道成功制備了高選擇性、高靈敏度的化學和生物傳感器。

▲六苯并苝衍生物的堆積模式

通過上圖,我們可以看到該有機半導體的堆積模式具有高度一致的周期性結構,而每個結構的長寬均不到2nm。

當然,從目前來看,利用“自組裝”技術來打造半導體芯片仍處于實驗室或者試驗生產階段,要想走向大規模商用還需要解決一些問題,比如前面Karl Skjonnemand提到的需要解決“結構中任何微小的缺陷”,此外,還需要有一套對應的開發工具來便于芯片設計公司利用自組裝技術和材料來進行開發。

不過,相對于傳統的半導體制程技術來說,“自組裝”技術確實將有助于繼續推動芯片制造工藝的提升,同時極大的降低先進芯片制造的成本。

“通過自組裝材料,繼續擴展計算和數字革命。這可能是分子制造新時代的曙光。”KarlSkjonnemand說到。

-

芯片

+關注

關注

459文章

52119瀏覽量

435654 -

摩爾定律

+關注

關注

4文章

638瀏覽量

79663

原文標題:芯片制造行業的新方向:“自組裝”技術解析

文章出處:【微信號:icsmart,微信公眾號:芯智訊】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

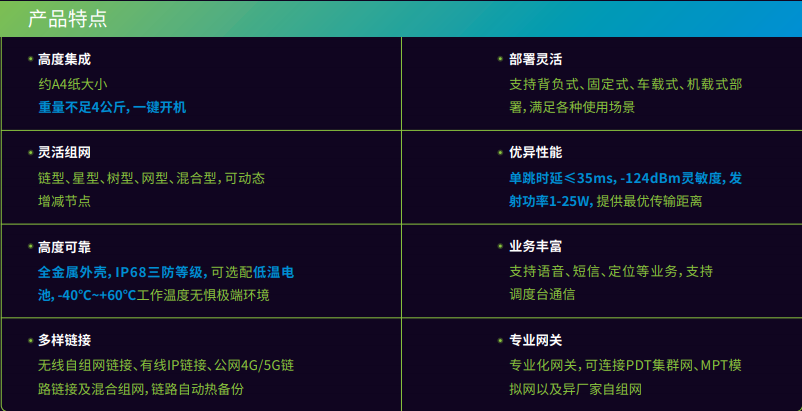

科普|無線自組網是什么?

應急通信新突破,云翎智能自組網應用守護生命安全

全面剖析倒裝芯片封裝技術的內在機制、特性優勢、面臨的挑戰及未來走向

DLPC410如何對SPI閃存進行編程?

億緯鋰能榮獲吉利遠程商用車兩項大獎

sMesh寬帶圖像自組網系統

SmartLink窄帶語音自組網系統

芯片“自組裝”何時能走向商用?

芯片“自組裝”何時能走向商用?

評論