我們將向您展示業(yè)界首款可編程器件上運行的56G 收發(fā)器的實際效果。PAM4 信令協(xié)議,這一前瞻性的技術(shù)通過在不增加每比特功耗和成本的前提下,擴(kuò)展 50G、100G、400G 以及端口密度等方式驅(qū)動下一波的以太網(wǎng)發(fā)展。

業(yè)界領(lǐng)先的收發(fā)器技術(shù)

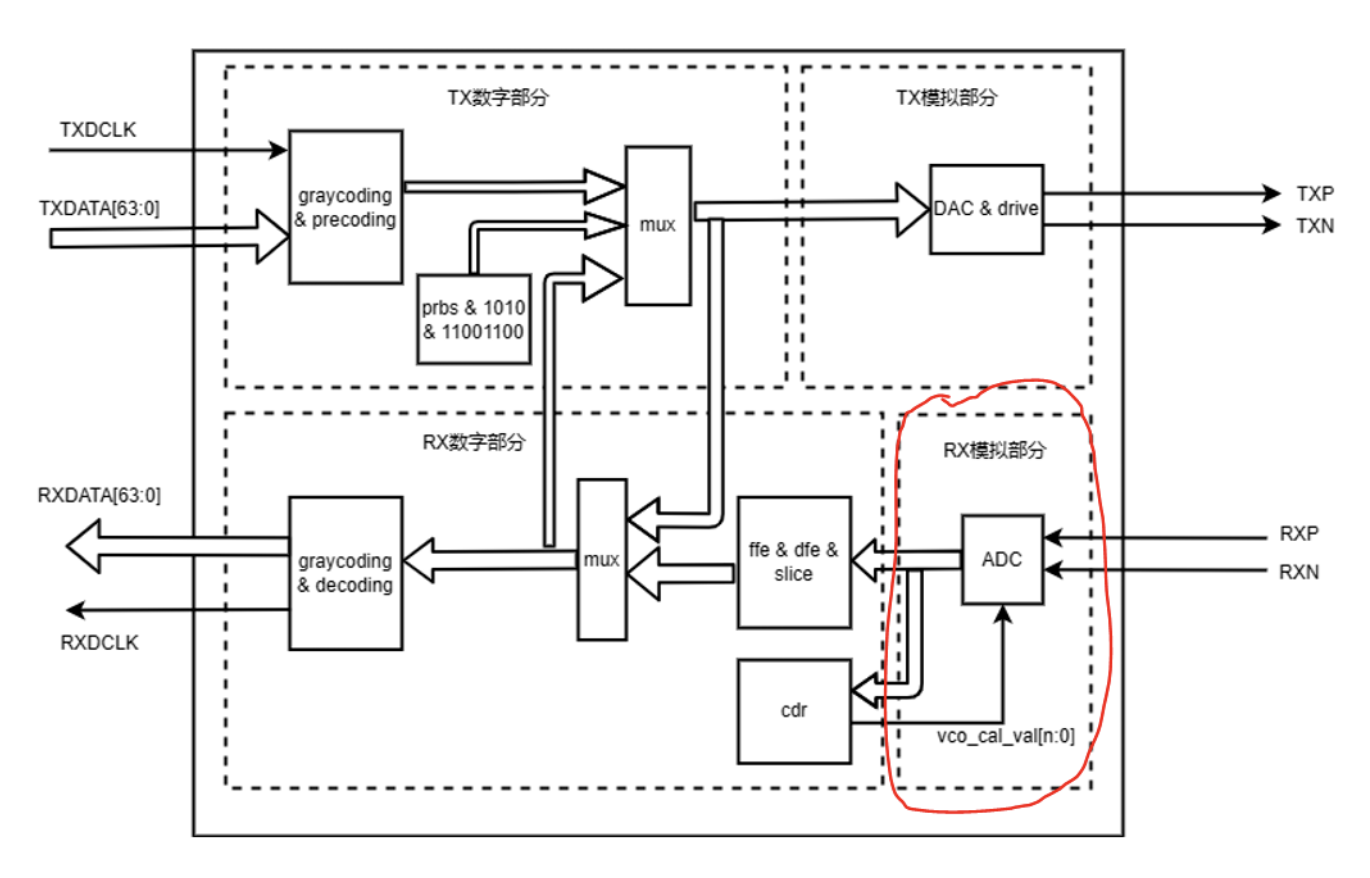

為幫助推進(jìn)新一輪以太網(wǎng)部署,Xilinx 已經(jīng)開發(fā)出基于 FinFET+ 的可編程器件運行 56Gb/s 收發(fā)器。全新架構(gòu):

以 50G+ 線路速率突破數(shù)據(jù)傳輸?shù)奈锢順O限

采用新一代均衡技術(shù),最大程度減少通道損耗

支持芯片間、模塊、直接附加線纜以及背板通信

PAM4 調(diào)制是前進(jìn)的道路

PAM4(或 4 級脈沖幅度調(diào)制)被公認(rèn)為是實現(xiàn)新一代線路速率的最高可擴(kuò)展性多級信號協(xié)議,而且 Xilinx 正在通過光學(xué)互聯(lián)網(wǎng)論壇 (OIF) 及電氣電子工程師協(xié)會 (IEEE) 幫助推動 56G PAM4 標(biāo)準(zhǔn)化工作的發(fā)展。

為實現(xiàn)新一代以太網(wǎng)鋪平了道路

云計算、工業(yè)物聯(lián)網(wǎng)以及軟件定義網(wǎng)絡(luò)應(yīng)用等都將繼續(xù)加速和推動對無限帶寬需求的發(fā)展。最新收發(fā)器架構(gòu)將幫助各大廠商:

在現(xiàn)有基礎(chǔ)架構(gòu)上讓帶寬翻番

擴(kuò)展 50G、100G、400G 端口以及太比特接口

評估用于開發(fā)其自己新一代解決方案的技術(shù)

新一代標(biāo)準(zhǔn)化線路速率是滿足這些不斷提高的帶寬需求的關(guān)鍵。

-

收發(fā)器

+關(guān)注

關(guān)注

10文章

3657瀏覽量

107393 -

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5585瀏覽量

174814 -

賽靈思

+關(guān)注

關(guān)注

33文章

1795瀏覽量

132128

發(fā)布評論請先 登錄

PCB仿真相同損耗下,28G NRZ的產(chǎn)品不能直接升級到56G PAM4?

56G高速背板PCB設(shè)計案例

展望未來英特爾FPGA設(shè)計,介紹新型224G PAM4收發(fā)器

Xilinx演示 56G PAM4 收發(fā)器技術(shù)迎接下一代以太網(wǎng)部署

Xilinx演示56G PAM4收發(fā)器技術(shù)迎接下一代以太網(wǎng)部署

可編程器件上運行的56G PAM4收發(fā)器技術(shù)演示

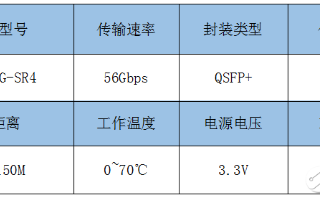

56G光模塊的特征是什么,它又有哪些應(yīng)用

56G QSFP+ AOC有源光纜的特征及應(yīng)用領(lǐng)域

光纖收發(fā)器的效果原理

56G QSFP+DAC無源高速線纜的詳細(xì)介紹

56G QSFP+AOC有源光纜的基礎(chǔ)知識

serdes串行發(fā)送和接收是怎么實現(xiàn)的?serdes就是用56G的ADC和DAC嗎?

了解高速56G PAM-4串行鏈路的時鐘需求

56G 收發(fā)器 的實際效果展示

56G 收發(fā)器 的實際效果展示

評論