現(xiàn)在,人們已經(jīng)離不開以電池供電的手持設備了(例如手機),所以低功耗設計成為了重中之重,摩爾定律很偉大,其他一些奇思妙想的創(chuàng)新也很偉大比如多時鐘和電源域,動態(tài)電平以及頻率縮放,功率控制以及多休眠狀態(tài)等。所有這些技術在數(shù)字設計上都非常有效,但對于模擬領域卻毫無用處。這真令人失望!

這個世界留下了和頑固的人類一樣頑固的模擬電路。有些設備如手機(含有大量的傳感器以及模擬輸出)在確保信號完整性以及低功耗的條件下處理模擬數(shù)據(jù)方面面臨巨大的挑戰(zhàn)。在模擬電路中要保持線性以及低噪聲通常要求設備是高增益且耗電大。功耗換取了速度(帶寬)、分辨率(線性度)、低噪聲(SNR)。不過,也有很多嵌入式開發(fā)人員可以采取的設計方法,可以實現(xiàn)低功耗的模擬設備,對那些做模擬的和混合信號設計的人來講世界還是有希望的。這里分享四個要點。

要點一、從一個公式入手

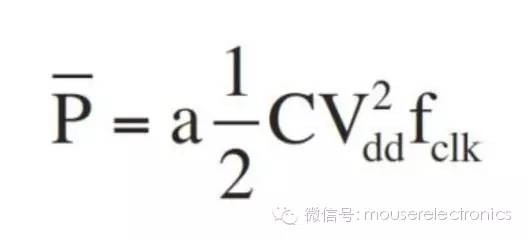

從下面這個動態(tài)功耗的計算公式中,我們可以找到幾個減少功耗的方法:

最大的降幅很明顯是來自降低電壓(VDD)。選擇一個運放(所有的事情都一樣),以最低的工作電壓和一個軌對軌的共模輸入范圍。然后電平盡早降到內(nèi)核低壓芯片的水平。再次對照這個公式,你也可以減少這個電路的有效性(a),通常通過一個門控時鐘來實現(xiàn);通過減少連接的電容和降低時鐘頻率(f)。很不幸的是,這些解決方案對數(shù)字電路比模擬電路更有用,因為這里靜態(tài)功耗是主要問題。

功耗、速率、和精度之間的關系需要權衡。最小化電源節(jié)省能量,簡化散熱裝置可以延長芯片的使用壽命。高速雖然對精度和濾波的要求放松,但是卻大大增加了功耗。通常你想要有足夠的速率來適應信號帶寬的要求;你需要足夠的精度來滿足系統(tǒng)動態(tài)范圍;過高的精度將使濾波放松,但是卻再次以功耗作為代價。你無法避免這種權衡,但是有方法來減少他們的影響。一種方法是數(shù)字協(xié)助模擬電路,能夠實現(xiàn)高精度,同時保持低功耗。例如數(shù)字校準電路可以分析他們的錯誤用逐漸逼近(SAR)的ADC并且在相應的情況下做出補償。它還可以補償溫度和電壓漂移敏感的模擬電路。

模擬輸出電路需要補償是由電路不匹配造成。在這里,DAC能夠起到一點電壓調節(jié)作用來調整這種不匹配。這樣的數(shù)字校準和補償技術將使模擬達到這樣的階段,就是不需要大的開環(huán)增益,但卻要求高電流。

要點二、關注模擬前端

只要符合系統(tǒng)的增益、帶寬、和轉換速率要求,最好使用單級模擬前端(AFE),用一個軌到軌共模AB級運放代替A級運放,可以有小的電流偏移,那樣可以消耗更少的靜態(tài)電流。

不過在這樣做的時候要小心,當你保留一個可接受的帶寬和轉換速率,你仍然可以提供足夠的增益和輸出功率,使增益最大化。

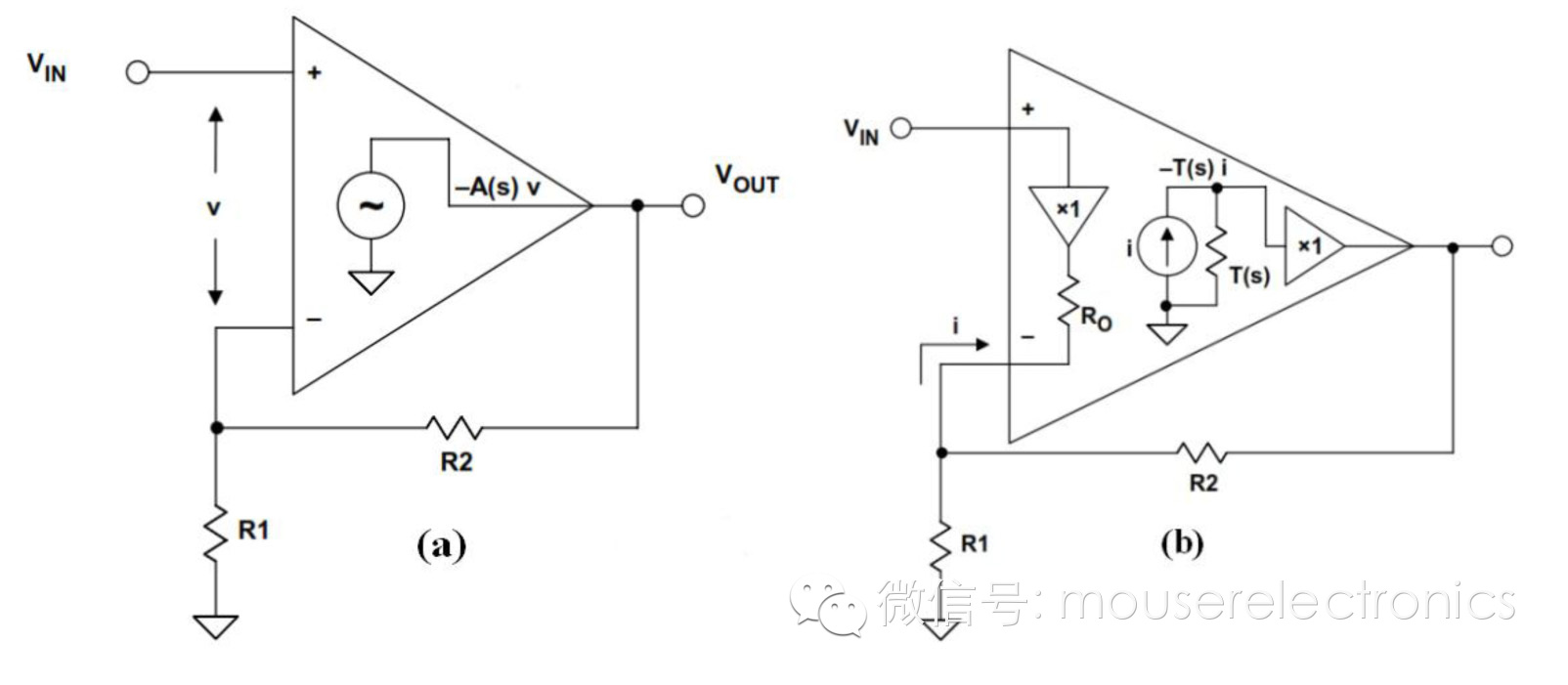

如果可以的話,設計一個電壓模式反饋電路圖a,對照圖b電流模式反饋電路。電壓模式驅動通常消耗了電流模式一半的功耗。在交流耦合系統(tǒng),如PCI Express,SATA,XAUI這一數(shù)字下降到25%。盡快的使信號數(shù)字化吧。你可以經(jīng)常使用數(shù)字濾波來補償微弱的模擬信號,它們離噪聲層太近了。

在數(shù)字電路中休眠模式非常有助于節(jié)省功耗,但是在模擬電路中必須謹慎使用。因為靜態(tài)漏電流特別是當線寬很小的情況下,在休眠模式下,電源開關用來為不同的電壓區(qū)控制電源的開和關。這在混合信號設計中將導致電平調擋的問題。為避免這樣,一個電源管理芯片(PMIC)可以將控制信號預設為IDDQ狀態(tài)來防止模擬電路的電流泄漏。

要點三、數(shù)據(jù)轉換器的選擇

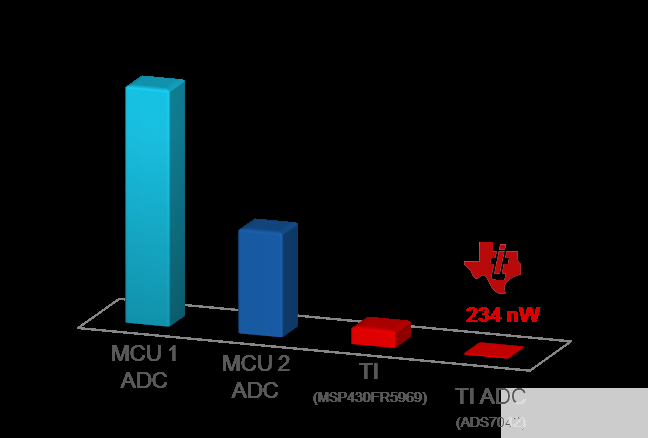

模擬前端放大器將底層的傳感器數(shù)據(jù)放大,然后將它提供給一個ADC。ADC的選擇對一個應用的功耗有很大影響。它還還影響前級運放的選擇。高精度的sigma-delta ADC在低頻應用中非常普遍。但是為了節(jié)省電力和晶圓尺寸,越簡單越好。在逐漸逼近(SDR)的ADC,不要求高增益高功耗的精密放大器。所以靜態(tài)功耗可以實現(xiàn)最小化。

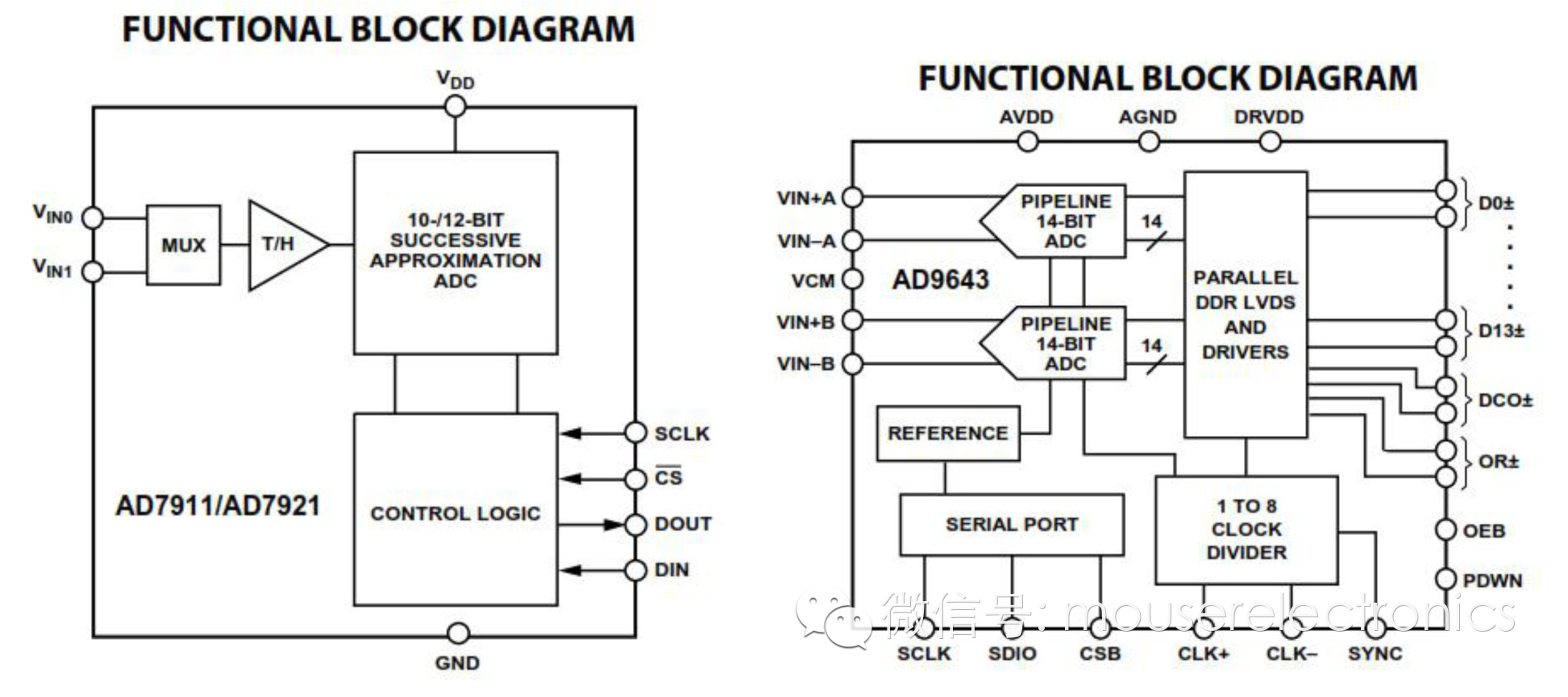

使用SAR ADC替換快速流水線ADC完成的結果是一樣的(雖然會慢很多),因為它只有一級比較器而后者有多級比較器。下面的圖2顯示了兩個模擬設備,2通道的ADC,一個是AD7911 SAR ADC,另一個是AD9643流水線ADC。流水線的那種在250MSPS時消耗了750mW.而SAR那種版本在250ksps時消耗了4mW.如果不需要高精度和高采樣率,那么就選擇一個SAR ADC。

圖2:左邊一個AD7911 SAR,右邊一個AD9643流水線ADC

要點四、深挖電源潛力

首先,混合信號電路必須有獨立的模擬地和數(shù)字地以防止噪聲從數(shù)字組件進入模擬系統(tǒng)。同理,所有的數(shù)字輸出布線時應該遠離模擬輸入。

地平面看似很簡單的概念,但是很多不同的電流通常在一個地平面流通。ADC需要一個模擬地,該模擬地不能和數(shù)字地共地,最好在PCB另起一個地層。兩個地平面只需要一個點連接在一起,如果可以,就在ADC的數(shù)字輸出的GND管腳上。所有的旁路電容、參考電容、和濾波電容以及ADC的地必須連到模擬地平面(盡可能的靠近),并且旁路電容接到電源管腳盡快的將AC電流到分流到地。

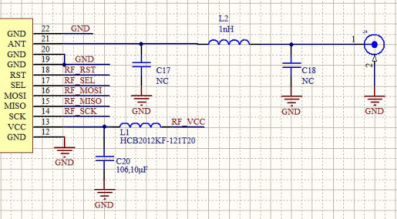

甚至電池供電的設備也可以要一個或多個開關控制器。這樣他們的輸出可以反饋到線性調節(jié)器,它們有時可以有時不能濾除所有殘余的紋波和峰峰值,就像是施了魔咒給模擬芯片,特別是工作在低壓的模擬芯片。好的布局以及大量使用旁路電容和鐵氧體磁體對解決這個問題大有幫助。

低功耗模擬是可以實現(xiàn)的

通過遵守一些簡單的設計原則以及一些并不簡單的數(shù)字方法,低功耗模擬設計是絕對是可以實現(xiàn)的。

半導體公司如Microchip、Freescale和Silicon Labs等通過在他們的的MCU中集成越來越多的模擬元件提升門檻,實現(xiàn)本文提及的數(shù)字輔助功能(所以可以叫做“智能模擬”“smart analog”)。由于越來越多涉及混合信號處理的新器件上市,嵌入式開發(fā)員如果能深入研究低功耗設計方法,將來一定會有豐厚的回報。

-

傳感器

+關注

關注

2564文章

52607瀏覽量

763853 -

放大器

+關注

關注

145文章

14103瀏覽量

216296 -

模擬設計

+關注

關注

1文章

55瀏覽量

18621 -

低功耗

+關注

關注

10文章

2734瀏覽量

104550

發(fā)布評論請先 登錄

傳感器設計的四大要點

晶圓制造流程簡要分析

電機驅動器所要求的四大要點你知道嗎?

低功耗MCU選型要點

LoRa天線電路設計四大要點

音頻功放失真的四大要點及改善方法

LoRa天線電路設計四大要點

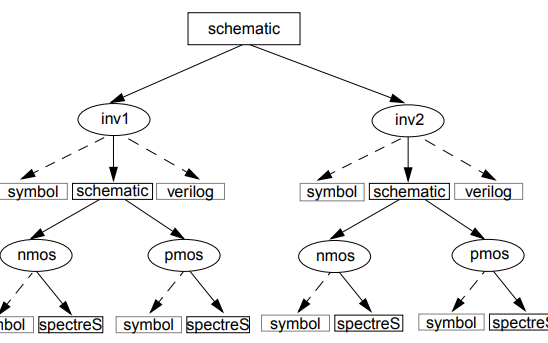

Cadence教程之如何使用VieloSo模擬設計環(huán)境進行設計

簡要介紹低功耗模擬設計四大要點分析

簡要介紹低功耗模擬設計四大要點分析

評論