同步動態(tài)隨機(jī)存取內(nèi)存(synchronous dynamic random-access memory,簡稱SDRAM)是有一個同步接口的動態(tài)隨機(jī)存取內(nèi)存(DRAM)。通常DRAM是有一個異步接口的,這樣它可以隨時響應(yīng)控制輸入的變化。而SDRAM有一個同步接口,在響應(yīng)控制輸入前會等待一個時鐘信號,這樣就能和計算機(jī)的系統(tǒng)總線同步。時鐘被用來驅(qū)動一個有限狀態(tài)機(jī),對進(jìn)入的指令進(jìn)行管線(Pipeline)操作。這使得SDRAM與沒有同步接口的異步DRAM(asynchronous DRAM)相比,可以有一個更復(fù)雜的操作模式。

-

SDRAM

+關(guān)注

關(guān)注

7文章

441瀏覽量

56033 -

計算機(jī)

+關(guān)注

關(guān)注

19文章

7630瀏覽量

90192 -

內(nèi)存

+關(guān)注

關(guān)注

8文章

3109瀏覽量

74994

發(fā)布評論請先 登錄

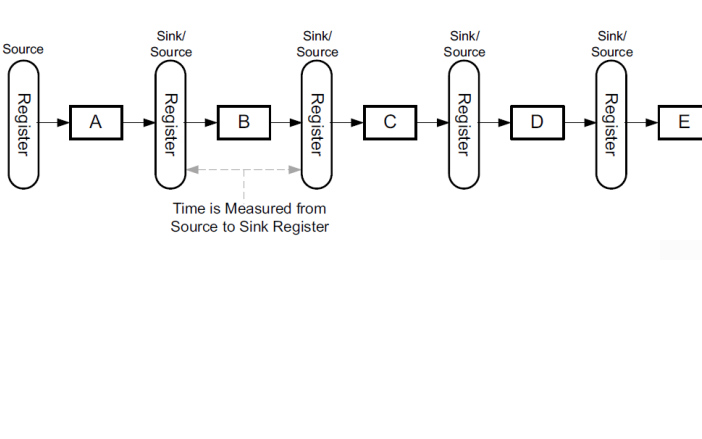

時序分析中的一些基本概念

FPGA零基礎(chǔ)學(xué)習(xí):SDR SDRAM驅(qū)動設(shè)計實用進(jìn)階

時序分析中的一些基本概念

關(guān)于SDRAM的基本概念講解

FPGA讀寫SDRAM的實例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計論文

FPGA學(xué)習(xí)教程之硬件設(shè)計基本概念

時序分析和時序約束的基本概念詳細(xì)說明

FPGA進(jìn)階教程:SDRAM的基本概念介紹

FPGA進(jìn)階教程:SDRAM的基本概念介紹

評論