本文介紹了在高速SI應用中對各種層壓材料進行介電常數(Dk)和介電損耗(Df)精確提取的方法。 TOD去嵌算法和優化算法用于該Dk / Df提取流程。 由此得到的頻變材料參數模型可以用于市場上的任何電磁場仿真工具。

1

簡介

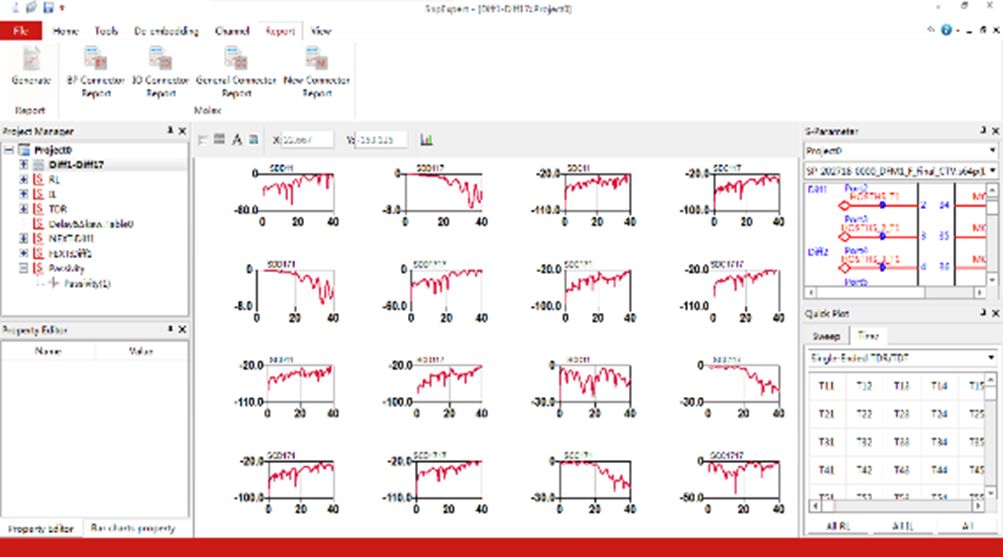

芯禾科技SnpExpert工具,提供了一種快速了解系統中無源互連器件電氣特性的方法,不僅可以查看S參數頻域特性,還可以查看時域反射結果(TDR)。該方案亮點包括:差分對和victim/aggressor設置的一鍵定義,以及內置的NEXT/FEXT/PSXT/ILD/ICR和ICN,允許用戶快速評估串擾;內置delay和skew計算器無需繁瑣的電路原理圖繪制;采用內置IEEE 802.3ap,802.3ba,802.3bj,SAS,PCIe,SATA,USB和OIF CEI 25G / 28G的合規性指標可快速顯示S參數合規性;內置模板自動執行從S參數繪圖到生成Word或PPT報告的流程;TOD方法幫助SI工程師通過去除夾具效應來快速獲得DUT結果;使用均衡和預加重技術進行精確的NRZ和PAM-4眼圖計算,幫助SI工程師獲得關于高速通道性能的直觀感受。

圖1 SnpExpert 用戶界面

2

Through-Only De-embedding(TOD)

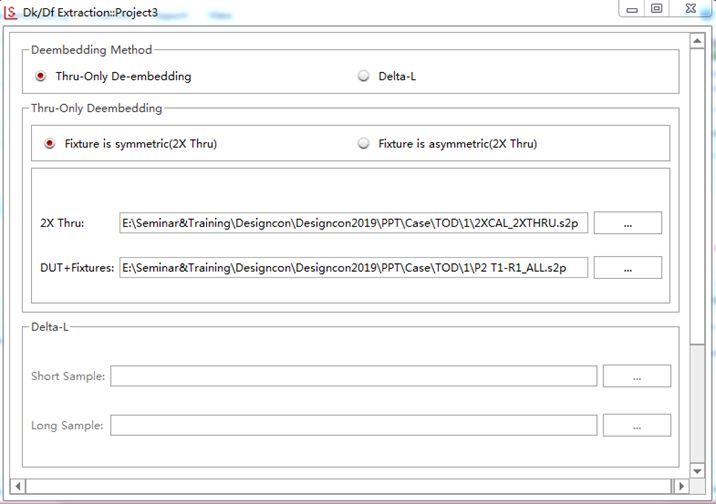

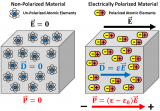

為了計算介電常數(Dk)和介電損耗(Df),需要制作常規的傳輸線結構,以探索PCB材料的射頻和微波參數。 SnpExpert為設計人員提供了一種簡單的方法,可以從復合測量中去嵌夾具,以提取DUT特性,這對于對稱和非對稱夾具結構的測試、測量和dk / df提取至關重要。

圖2 Through-Only De-embedding 流程

3

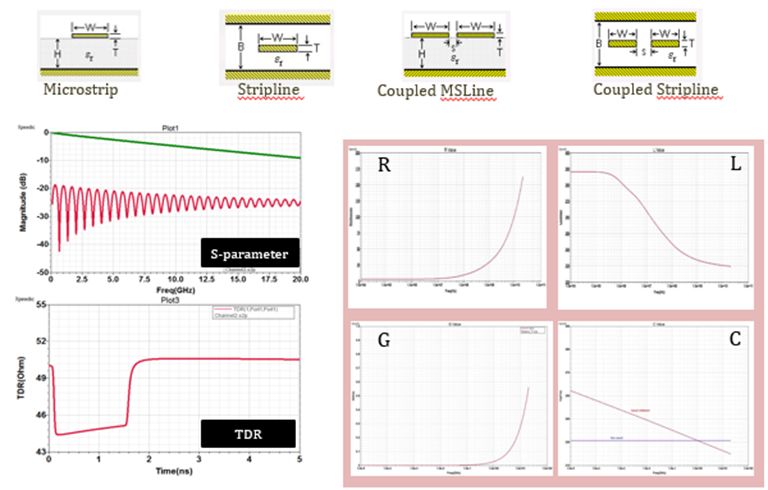

快速 2D RLGC 求解器

我們在Dk / Df提取流程中集成了具有因果介電模型和表面粗糙度模型的基于2D FEM的RLGC快速場求解器,這能顯著提高PCB材料特性的提取精度。 Dk / Df提取流程將重復調用RLGC求解器,直到插入損耗的幅度和相位滿足收斂誤差。

圖3 2D RLGC 求解器

4

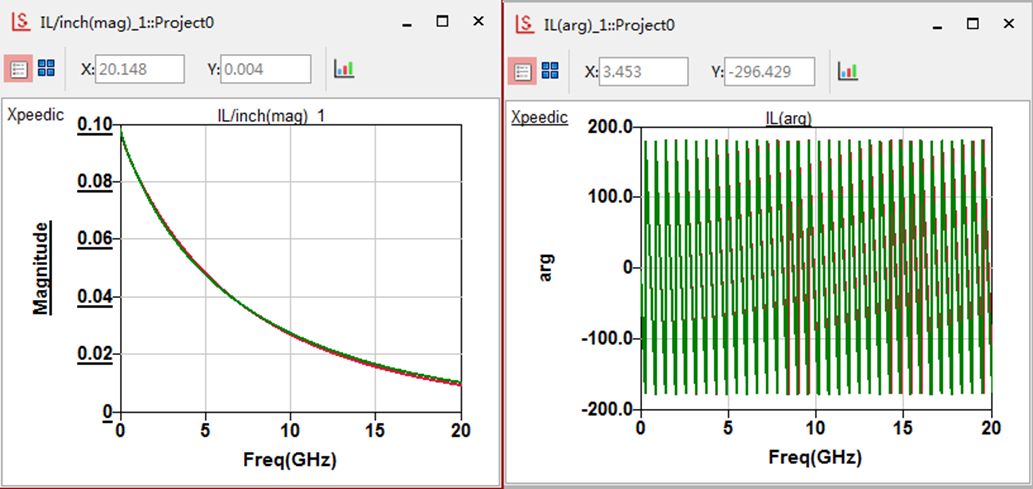

Dk/Df 提取流程中的遺傳算法

在Dk/Df和表面粗糙度的初始猜測之后,我們使用了基于自然選擇過程的改進遺傳算法(GA)優化來適配IL,這顯著減少了在Dk / Df提取中調用2D FEM RLGC求解器的迭代次數。

圖4 基于遺傳算法的 IL 匹配過程

5

總結

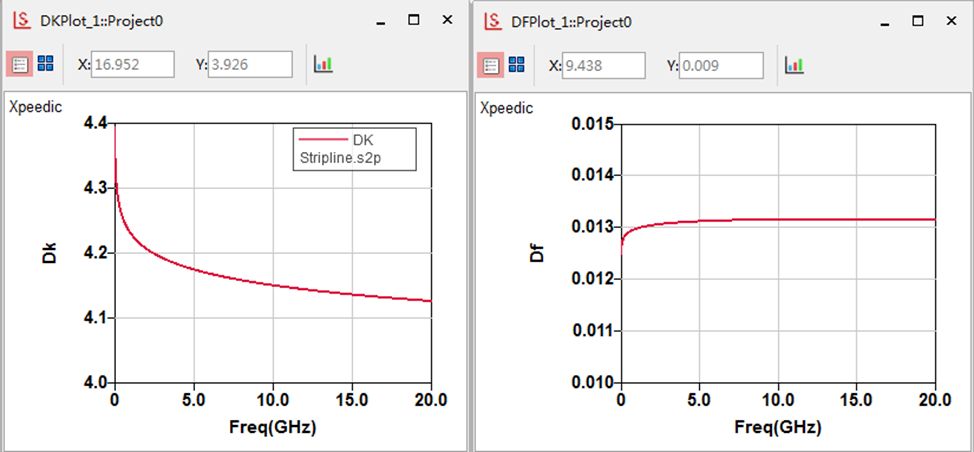

本文描述了基于TOD和GA優化算法的Dk / Df提取流程,適用于高速和寬帶應用。 該流程可以顯著簡化具因果性的電介質模型和表面粗糙度模型的提取。

圖5 dk 與 df 曲線

-

電路

+關注

關注

173文章

6022瀏覽量

174442 -

算法

+關注

關注

23文章

4699瀏覽量

94747 -

介電損耗

+關注

關注

0文章

4瀏覽量

7486

原文標題:高速SI應用中的精確Dk / Df提取

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

高頻PCB基材介電常數與介電損耗的特性與改性進展

介電常數怎么測試_介電常數測試方法

高速SI應用中對各種層壓材料進行介電常數和介電損耗精確提取的方法

高速SI應用中對各種層壓材料進行介電常數和介電損耗精確提取的方法

評論