電信設(shè)備,服務(wù)器和數(shù)據(jù)中心的最新FPGA具有多個(gè)電源軌,需要正確排序才能安全地為這些系統(tǒng)上下供電。高可靠性DC-DC穩(wěn)壓器和FPGA電源管理的設(shè)計(jì)人員需要一種簡單的方法來安全地放電大容量電容器,以避免損壞系統(tǒng)。

FPGA電源排序

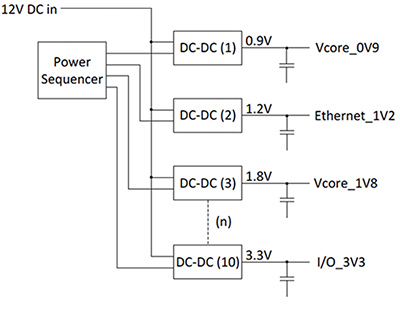

最新在生成片上系統(tǒng)FPGA的過程中,它們可以提供十個(gè)獨(dú)立的電源軌,為Vcore,存儲(chǔ)器總線電源,I/O控制器,以太網(wǎng)等提供電源。如圖1所示,每個(gè)電源軌由DC供電。直流轉(zhuǎn)換器可調(diào)節(jié)3.3 V,2.5 V,1.8 V,0.9 V等所需的電壓。為了給系統(tǒng)加電,遵循特定的順序以確保安全操作并避免損壞系統(tǒng)。同樣在系統(tǒng)關(guān)閉期間,電源序列的順序相反,確保在下一個(gè)電源軌關(guān)閉之前禁用每個(gè)電源軌。該指令通過電源序列發(fā)生器芯片控制,該芯片可啟用每個(gè)DC-DC穩(wěn)壓器,如圖1所示。

圖1:典型FPGA系統(tǒng)電源軌每個(gè)服務(wù)的供電。

考慮存儲(chǔ)在各種電源軌上的去耦電容中的電荷時(shí)會(huì)出現(xiàn)問題。例如,在0.9 V Vcore電源軌上,總?cè)ヱ铍娙菘梢栽?0到20 mF的數(shù)量級(jí),并且存儲(chǔ)在電容器組中的剩余電荷需要在斷電期間主動(dòng)放電,在下一次電源關(guān)閉之前序列被禁用。這樣可以避免違反掉電序列并保護(hù)FPGA系統(tǒng)。因此,建議在每個(gè)DC-DC穩(wěn)壓器輸出端使用有源放電電路。

有源電容放電開關(guān)

通過了解電容器組的大小,可以采用開放式方法對(duì)RC時(shí)間常數(shù)進(jìn)行放電。一旦電壓小于充電狀態(tài)的95%(在3×RC時(shí)間常數(shù)下發(fā)生),則假設(shè)電容器放電。

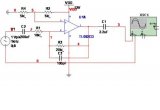

這樣做的一個(gè)簡單方法是通過一個(gè)具有已知接地電阻的開關(guān),當(dāng)需要放電時(shí)可以接通該開關(guān)。參考圖1,電源序列發(fā)生器啟用每個(gè)DC-DC穩(wěn)壓器的輸出。然后可以使用該相同的使能(EN)信號(hào)來饋送并聯(lián)連接到電容器組的開關(guān)。通過反轉(zhuǎn)使能信號(hào)來驅(qū)動(dòng)開關(guān),當(dāng)DC-DC穩(wěn)壓器的輸出被禁止時(shí),它將使電容器放電。對(duì)于開關(guān),首選N溝道功率MOSFET,因?yàn)樗苋菀讖囊缘貫閰⒖嫉倪壿嬓盘?hào)驅(qū)動(dòng)。所選電路如圖2所示,Q2為N溝道功率MOSFET,Q1為P溝道MOSFET,反轉(zhuǎn)電源序列發(fā)生器的EN邏輯信號(hào)。

圖2:有源放電電路。

有源電容放電電路操作

參見圖2 - 電源序列發(fā)生器的EN輸出為DC-DC穩(wěn)壓器上的使能引腳供電以及電容器放電電路。當(dāng)邏輯“0”發(fā)出關(guān)閉信號(hào)時(shí),P溝道MOSFET(Q1)將信號(hào)反相,然后接通N溝道MOSFET(Q2)以對(duì)電容器組放電。

放電電路假設(shè)一旦關(guān)閉信號(hào)施加,DC-DC穩(wěn)壓器就無法繼續(xù)產(chǎn)生輸出。如果在關(guān)閉命令激活后,DC-DC穩(wěn)壓器的輸出有電,則必須在放電電路激活之前引入延遲。這是為了確保放電MOSFET不會(huì)試圖吸收DC-DC穩(wěn)壓器的全部輸出電流能力。

為了從邏輯“0”信號(hào)增強(qiáng)N溝道功率MOSFET(Q2),P溝道MOSFET(Q1)將信號(hào)反相為5 V,以施加在Q2柵極源上。選擇P溝道MOSFET(Q1)不具有低柵極閾值電壓(VGS(th))。這是因?yàn)閂GS(th)相對(duì)于溫度下降并且Q1在邏輯“1”狀態(tài)期間需要處于OFF狀態(tài)以避免Q2的錯(cuò)誤接通。需要選擇適合5 V操作的最佳值以及Power Sequencer。

當(dāng)電源序列發(fā)生器輸出邏輯“1”時(shí),DC-DC穩(wěn)壓器在ON狀態(tài)下使能,Q2必須處于OFF狀態(tài)。采用邏輯“1”輸出,最小高電平輸出電壓為4.19 V(電源序列發(fā)生器的EN引腳輸出規(guī)格),則在環(huán)境工作溫度為60°C時(shí),Q1 VGS(th)需要大于0.9 V 。此外,Q2的柵極需要通過100kΩ的R1電阻下拉至源極電位,以避免誤導(dǎo)通。

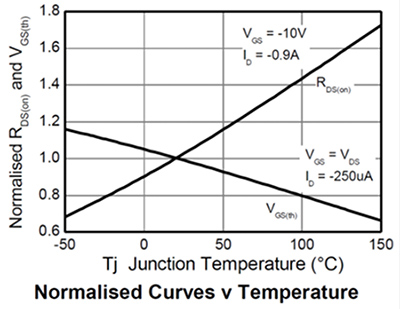

溫度的VGS(th)變化在典型的電氣曲線中找到。 MOSFET數(shù)據(jù)表。例如,圖3中給出了來自Diodes Incorporated的ZXMP6A13F的歸一化VGS(th)與溫度的關(guān)系.ZXMP6A13F是首選器件,因?yàn)楸WC最小VGS(th)在室溫下為1 V,在60℃時(shí)降至約0.9 V °C。

圖3:ZXMP6A13F的溫度標(biāo)準(zhǔn)化RDS(on)和VGS(th)曲線。

當(dāng)電源序列發(fā)生器使能輸出變?yōu)檫壿?#39;0'時(shí),則存在0.270 V的最大低電平輸出,Q1需要保證通過該5 V - 0.270 V信號(hào)增強(qiáng)通道,以確保Q2導(dǎo)通并放電電容器組。因此,Q1需要在VGS = -4.5 V時(shí)具有導(dǎo)通狀態(tài)。

為了對(duì)電容器組放電,選擇N溝道功率MOSFET(Q2)具有導(dǎo)通電阻(RDS(開) ))適合于在10 ms內(nèi)對(duì)最大電容組放電,以確保在不到100 ms的時(shí)間內(nèi)完成10個(gè)通道的完全關(guān)閉順序。必須提供輔助電源,以在關(guān)閉電源后至少100 ms驅(qū)動(dòng)關(guān)閉電路(電源序列發(fā)生器)。

放電計(jì)算的時(shí)間

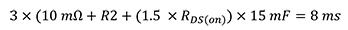

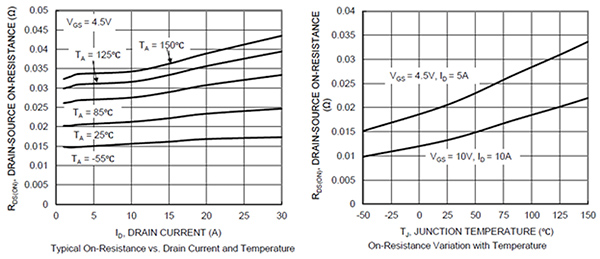

使用3 x RC時(shí)間常數(shù),其中R是電容器組的ESR的組合電阻(假設(shè)<5mΩ),寄生走線電阻(假設(shè)為為<5mΩ),串聯(lián)漏極電阻(R2)和功率MOSFET Q2 RDS(on)。還包括功率MOSFET導(dǎo)通電阻的溫度依賴性,可以高達(dá)Tamb =25?C時(shí)最大RDS(on)的1.5倍,同時(shí)假設(shè)結(jié)已達(dá)到絕對(duì)最大額定溫度(典型TJ(最大值) )= 150°C) - 參見圖5.

要在不到10 ms的時(shí)間內(nèi)對(duì)15 mF電容器組放電,需要3 x RC = 8 ms:

因此,功率MOSFET Q2在VGS = 4.5 V,Tamb =25?C時(shí)需要RDS(on)<80mΩ。假設(shè)一個(gè)50mΩ的串聯(lián)漏極電阻(在圖2中稱為R2)與MOSFET一起使用。

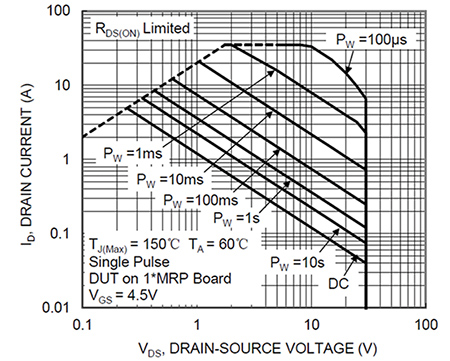

安全工作區(qū)和瞬態(tài)熱應(yīng)力

選擇功率MOSFET Q2的額定功率能夠處理放電電流的瞬態(tài)功耗。通過仿真計(jì)算峰值功率,并根據(jù)功率MOSFET數(shù)據(jù)表的瞬態(tài)功率容量圖檢查該值。由于功率MOSFET將隨時(shí)間消耗電容器的能量作為電流和電壓的函數(shù),因此需要檢查數(shù)據(jù)表中的安全工作區(qū)(SOA)曲線。這將提供功率MOSFET可以安全處理的最大單脈沖,同時(shí)確保結(jié)溫不超過絕對(duì)最大額定值,典型TJ(最大值)= 150°C。 SOA應(yīng)該基于應(yīng)用的環(huán)境工作溫度和所需的MOSFET柵極驅(qū)動(dòng),在這種情況下為4.5V。在放電0.9 V充電電容器組的情況下,然后檢查SOA曲線,以獲得1 V時(shí)的單脈沖峰值電流能力在1 ms和10 ms之間的脈沖寬度曲線。 SOA應(yīng)該針對(duì)典型的應(yīng)用環(huán)境溫度(假設(shè)為60°C),同時(shí)安裝在PCB上,散熱最小,也稱為最小推薦焊盤(MRP)布局。在這些條件下,請(qǐng)參考圖4了解DMN3027LFG的SOA。

圖4:DMN3027LFG的安全工作區(qū)(SOA)

需要在實(shí)際電路中測量電容器組的峰值浪涌電流,以確保足夠的電阻減慢響應(yīng)速度,以避免可能導(dǎo)致EMI問題的急劇上升電流峰值以及N通道上的瞬態(tài)熱應(yīng)力功率MOSFET和電容器組。在圖2中,將一個(gè)50mΩ串聯(lián)電阻添加到Q2的漏極,以確保固定的已知值(與溫度無關(guān))在放電路徑中的總電阻中占主導(dǎo)地位。

MOSFET導(dǎo)通電阻變化

請(qǐng)注意MOSFET的導(dǎo)通電阻隨溫度變化,如圖5所示,在4.5 V柵極驅(qū)動(dòng)的預(yù)期工作溫度范圍內(nèi)變化高達(dá)15mΩ。除此之外,您還將在零件到零件和批次之間進(jìn)行RDS(on)變化。典型的RDS(on)為22mΩ,在室溫下DMN3027LFG上4.5 V柵極驅(qū)動(dòng)的最大規(guī)格限制為26mΩ。

圖5:DMN3027LFG的導(dǎo)通電阻溫度響應(yīng)。

因此,為確保已知電阻在放電路徑中占主導(dǎo)地位,最佳做法是使用R2系列電阻,該電阻約為最大RDS(on)的兩倍在選定的門驅(qū)動(dòng)器上。當(dāng)R2為50mΩ且RDS(on)在15mΩ至40mΩ(典型值為22mΩ)之間變化時(shí),95%的放電時(shí)間為3.9至5.4 ms(3 x RC)。這是最差情況下電容器組大小為20 mF。

功耗

計(jì)算功率MOSFET Q2和串聯(lián)電阻R2的功耗取決于占空比和Q2導(dǎo)通的時(shí)間。

如果在Q2導(dǎo)通時(shí)DC-DC穩(wěn)壓器上的0.9 V輸出使能,那么Q2和R2之間可以達(dá)到11 W。假設(shè)結(jié)溫達(dá)到150°C,典型的RDS(on)穩(wěn)定在35mΩ,如圖5所示。不應(yīng)允許這種情況,因?yàn)樗`反了DMN3027LFG的最大功耗并導(dǎo)致結(jié)點(diǎn)溫度超過絕對(duì)最大額定值。因此,必須禁用DC-DC穩(wěn)壓器輸出,同時(shí)啟用Q2。

這意味著最壞的情況是由電容器短時(shí)間充電和放電引起的。假設(shè)電源序列發(fā)生器進(jìn)入連續(xù)循環(huán)啟用,然后每隔20 ms禁用DC-DC穩(wěn)壓器(10 ms啟用+ 10 ms禁用),那么這將導(dǎo)致Q2和R2上的功率約為0.5 W.這是通過知道存儲(chǔ)在電容器組中的總能量將每20 ms放電來計(jì)算的:

P = E/t =?CV2/20 ms = 500 mW,最大電容器組的C = 20 mF充電至1 V.

最壞情況下,RDS(on)為40mΩ,26mΩx1.5,VGS = 4.5 V,TJ(最大值)= 150°C(圖3)。因此,Q2和R2的功耗分別為222 mW和278 mW。 15mΩ的最低RDS(on)會(huì)使R2的功耗增加到385 mW;意味著需要0.5 W額定值的表面貼裝電阻。

在典型應(yīng)用中,環(huán)境溫度預(yù)計(jì)達(dá)到60°C,DMN3027LFG在最小推薦焊盤布局上的RθJA= 130°C/W,當(dāng)耗散222 mW時(shí),TJ達(dá)到90°C 。這為TJ(最大)= 150°C提供了充足的空間。

電容器組放電測量

使用DMN3027LFG和ZXMP6A13F組裝使用6 x 2,200 uF電解電容器(13.2 mF)的電容器組,如圖2所示.ZXMP6A13F用5 V手動(dòng)觸發(fā)信號(hào)。

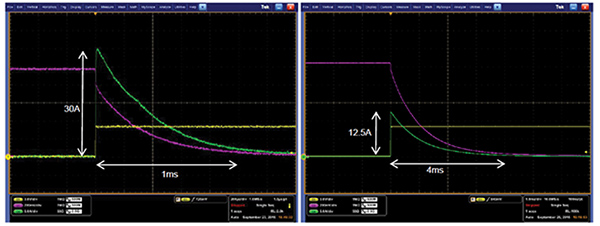

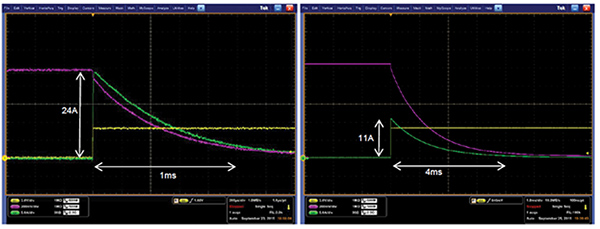

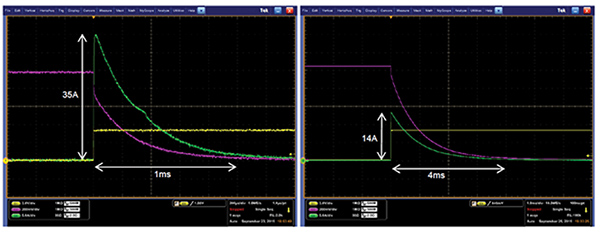

使用和不使用50mΩ串聯(lián)電阻進(jìn)行測量,然后在室溫,零下和高溫下進(jìn)行測量,以觀察峰值電流和放電時(shí)間的變化。僅通過DMN3027LFG通道RDS(on)電阻(不帶50mΩ)放電會(huì)產(chǎn)生觀察最大峰值電流的最壞情況。請(qǐng)注意以下曲線中的時(shí)間尺度不同 - 200μs/div和1 ms/div

通道1(C1)為黃色= DMN3027LFG柵極引腳上的電壓

通道3 (C3)為品紅色=電容器組上的電壓

通道4(C4)為綠色=來自DMN3027LFG源引腳的電流探頭

圖6:室溫測量(約Ta = 20°C)。左曲線= 30 A峰值電流僅通過DMN3027LFG通道電阻放電(200μs/div)右曲線= 12.5通過DMN3027LFG和50mΩ串聯(lián)電阻放電的峰值電流(1 ms/div)

參見圖6,圖7和圖8 - 僅通過DMN3027LFG對(duì)13.2 mF電容器組放電,產(chǎn)生的峰值電流從24 A變化到35 A,具體取決于MOSFET RDS(on)的溫度響應(yīng)。通過添加50mΩ串聯(lián)電阻,可將峰值電流限制在<15 A,溫度變化僅限于11 A至14 A.請(qǐng)注意,隨著溫度升高,峰值電流會(huì)相對(duì)于RDS(on)增加而下降。

即使溫度變化,放電時(shí)間至初始1 V充電狀態(tài)的95%也會(huì)在約3至4 ms內(nèi)發(fā)生。這與3 x RC時(shí)間常數(shù)的預(yù)期相同,SPICE建模此電路可以復(fù)制類似的結(jié)果。模擬一個(gè)13.2 mF電容器組在27°C(默認(rèn)),加入50mΩ串聯(lián)電阻,然后峰值電流約為13 A,并在3 ms內(nèi)放電至95%。

圖7:高溫測量(大約Ta = 70°C)。左曲線= 24僅通過DMN3027LFG通道電阻的峰值電流放電(200μs/div)右曲線= 11通過DMN3027LFG和50mΩ串聯(lián)電阻(1 ms/div)放電的峰值電流

圖8:零下溫度測量(約Ta = -20°C)。左曲線= 35僅通過DMN3027LFG通道電阻的峰值電流放電(200μs/div)右曲線= 14通過DMN3027LFG和50mΩ串聯(lián)電阻(1 ms/div)放電的峰值電流

結(jié)論

已經(jīng)證明了一種基于已知RC時(shí)間常數(shù)對(duì)大電容器組放電的安全且簡單的方法。這種開放式技術(shù)可以根據(jù)電容大小進(jìn)行縮放。選擇了以下器件:

Q1 = SOT23中的ZXMP6A13F P溝道MOSFET

Q2 = PowerDI3333-8中的DMN3027LFG N溝道MOSFET

R2 = 50mΩ表面貼裝電阻能夠耗散500 mW。

通過在放電路徑中添加50mΩ串聯(lián)電阻,可以限制峰值放電電流并穩(wěn)定溫度變化。測量結(jié)果和模擬結(jié)果均吻合良好;讓設(shè)計(jì)師有信心對(duì)不同的電容器組尺寸進(jìn)行建模。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21950瀏覽量

613742 -

電容器

+關(guān)注

關(guān)注

64文章

6518瀏覽量

101792 -

MOSEFT

+關(guān)注

關(guān)注

0文章

35瀏覽量

4592

發(fā)布評(píng)論請(qǐng)先 登錄

有源箝位中箝位管強(qiáng)制關(guān)斷電路

鉭電容電路設(shè)計(jì)注意事項(xiàng)

運(yùn)放電路中電容的常見身影

功放電路電源設(shè)計(jì)注意事項(xiàng)

如何選擇功放電路組件 功放電路的排列與連接

注意,使用不當(dāng),陶瓷電容也會(huì)著火

FPGA系統(tǒng)中有源電容放電電路設(shè)計(jì)需注意哪些問題

FPGA系統(tǒng)中有源電容放電電路設(shè)計(jì)需注意哪些問題

評(píng)論