隨著三星宣布7nm EUV工藝的量產,2018年EUV光刻工藝終于商業化了,這是EUV工藝研發三十年來的一個里程碑。不過EUV工藝要想大規模量產還有很多技術挑戰,目前的光源功率以及晶圓產能輸出還沒有達到理想狀態,EUV工藝還有很長的路要走。在現有的EUV之外,ASML與IMEC比利時微電子中心還達成了新的合作協議,雙方將共同研發新一代EUV光刻機,NA數值孔徑從現有的0.33提高到0.5,可以進一步提升光刻工藝的微縮水平,制造出更小的晶體管。

NA數值孔徑對光刻機有什么意義?,決定光刻機分辨率的公式如下:

光刻機分辨率=k1*λ/NA

k1是常數,不同的光刻機k1不同,λ指的是光源波長,NA是物鏡的數值孔徑,所以光刻機的分辨率就取決于光源波長及物鏡的數值孔徑,波長越短越好,NA越大越好,這樣光刻機分辨率就越高,制程工藝越先進。

現在的EUV光刻機使用的是波長13.5nm的極紫外光,而普通的DUV光刻機使用的是193nm的深紫外光,所以升級到EUV光刻機可以大幅提升半導體工藝水平,實現7nm及以下工藝。

但是改變波長之后再進一步提升EUV光刻機的分辨率就要從NA指標上下手了,目前的光刻機使用的還是NA=0.33的物鏡系統,下一代的目標就是NA=0.5及以上的光學系統了。

如今ASML與IMEC合作的就是高NA的EUV工藝了,雙方將成立一個聯合實驗室,在EXE:5000型光刻機上使用NA=0.55的光學系統,更高的NA有助于將EVU光源投射到更廣闊的晶圓上從而提高半導體工藝分辨率,減少晶體管尺寸。

如今這項研究才剛剛開始,所以新一代EUV光刻工藝問世時間還早,此前ASML投資20億美元入股蔡司公司,目標就是合作研發NA=0.5的物鏡系統,之前公布的量產時間是2024年,這個時間點上半導體公司的制程工藝應該可以到3nm節點了。

-

光刻

+關注

關注

8文章

337瀏覽量

30581 -

EUV

+關注

關注

8文章

609瀏覽量

86870

發布評論請先 登錄

【「芯片通識課:一本書讀懂芯片技術」閱讀體驗】了解芯片怎樣制造

納米壓印光刻技術旨在與極紫外光刻(EUV)競爭

晶圓表面光刻膠的涂覆與刮邊工藝的研究

日本首臺EUV光刻機就位

【「大話芯片制造」閱讀體驗】+芯片制造過程工藝面面觀

簡述光刻工藝的三個主要步驟

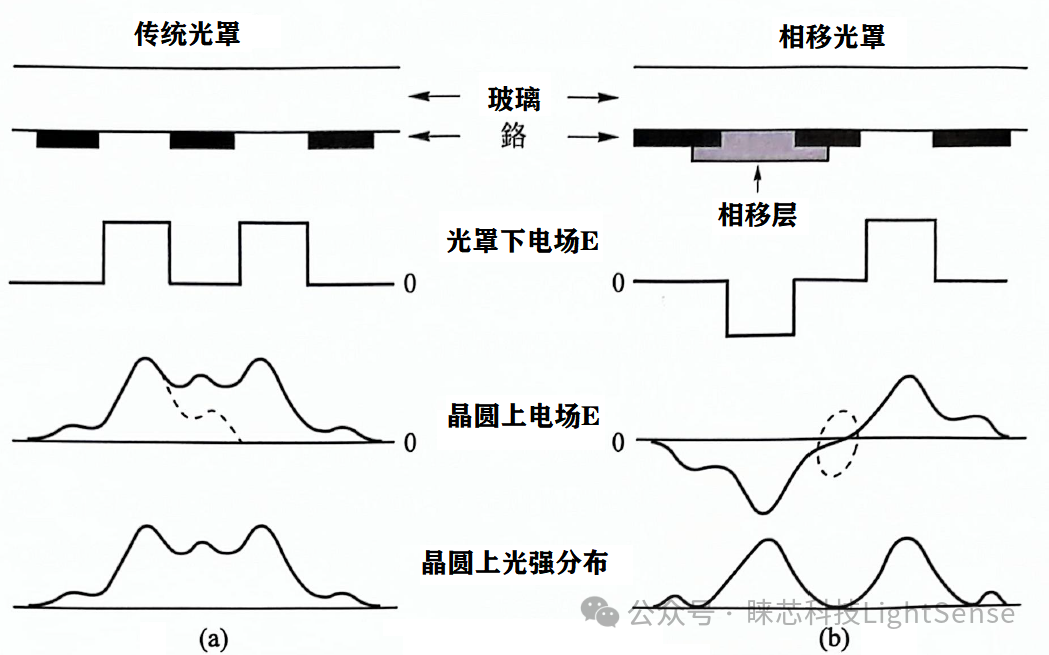

光刻工藝中分辨率增強技術詳解

光刻掩膜和光刻模具的關系

光刻工藝的基本知識

EUV光刻工藝終于商業化 新一代EUV光刻工藝正在籌備

EUV光刻工藝終于商業化 新一代EUV光刻工藝正在籌備

評論