1 、引言

CCD(Charge Coupled Devices——電荷耦合器件)具有尺寸小、精度高、功耗低、壽命長及電子自掃描等優點,在圖像傳感和非接觸測量領域得到廣泛的應用。由于CCD的轉換效率、信噪比等光電特性只有在合適的時序驅動下才能達到設計所規定的最佳值,輸出穩定可靠的信號,因此,驅動電路的設計也就成為其應用中的關鍵問題之一。不同廠家、不同型號CCD器件的驅動時序各不相同,使CCD的驅動電路很難規范化和產品化。筆者設計的基于FPGA的驅動電路是可再編程的,如果要改變驅動電路的時序,增加或減少某些功能,只需對器件重新編程,在不改變任何硬件的情況下可實現驅動電路的更新換代。

2 、CCD工作參數和時序分析

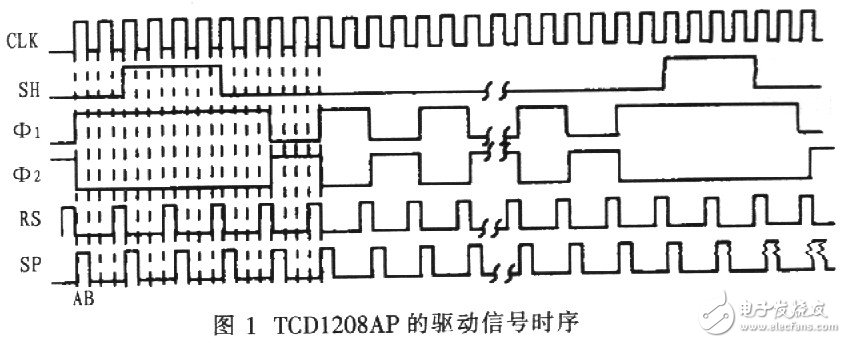

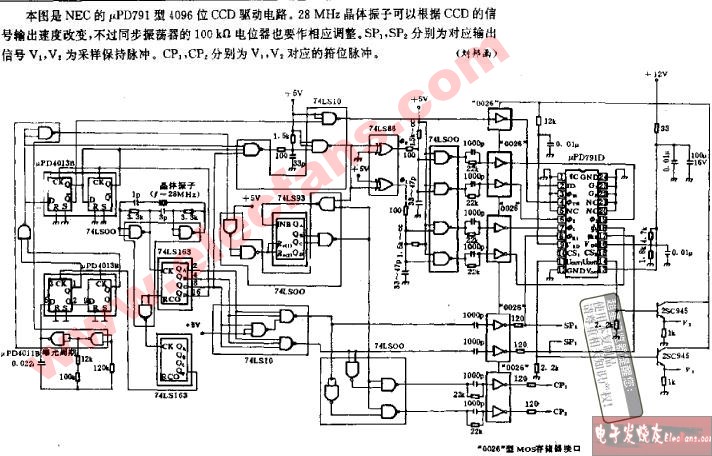

根據工程項目的技術要求,本系統選用日本TOSHIBA公司的TCDl208AP型電路作為傳感器。該器件具有優良的光電特性,有2 160個像元,其驅動信號的時序如圖l所示。

由TCDl208AP的時序圖可以看出,TCDl208AP采用二相驅動脈沖工作,時序脈沖驅動電路提供4路工作脈沖,即光積分脈沖SH,電荷轉移脈沖φ1、φ2,輸出復位脈沖RS。系統提供的主時鐘頻率CLK為4 MHz,設定數據輸出頻率為1 MHz。TCDl208AP的典型最佳工作頻率為l MHz,該器件具有2160位有效像元,正常工作時要有52個虛設單元輸出(DUMMY 0UTPUTS)信號(含暗電流信號)。因為該器件是二列并行傳輸,所以在一個周期內至少要有1 106(2 212/2=1 106)個φ1脈沖,即TSH》1106Tφ1。另外,由時序圖可以看出,當SH信號為高電平期間,CCD積累的信號電荷包通過轉移柵進入移位寄存器,移位脈沖φ1、φ2要求保持一個高和低的電平狀態。

3 、FPGA器件的選擇

根據設計要求和工程需要,本設計選用Altera公司Cyclone系列產品中的EPlCl2Q240C8型嵌入式可編程邏輯器件。EPlCl2Q240C8采用基于1.5 V、0.13μm及全層銅SRAM工藝,其密度增加至20 060個邏輯元件(LE),RAM增加至288 KB。它具有用于時鐘的鎖相環、DDR SDR和快速周期RAM(FCRAM)存儲器所需的專用雙數據率(DDR)接口,具有在系統可編程特性。其配置方式有被動型和主動型,被動型配置是在上電后由計算機通過編譯后產生sof文件利用專用的下載電纜配置電路。主動型配置是在上電后由專門的可編程配置電路(EPCS4)自動對EP1C12Q240C8電路進行配置。

4 、CCD驅動電路設計

驅動電路的功能是產生保證產生CCD器件正常工作的轉移時鐘、傳輸時鐘、采樣保持時鐘、復位時鐘、信號處理電路和A/D轉換電路所需要的同步脈沖、像元時鐘和箝位脈沖。只有驅動脈沖與CCD的良好配合才能充分發揮CCD的光電轉換特性,輸出穩定可靠的光電信號。

以前采用數字邏輯電路來設計線陣CCD驅動電路,由于采用多個計數器、觸發器和門電路,電路復雜,抗干擾能力差,而且時序較難配合,不易調試。如果采用FPGA驅動方法產生驅動信號,系統用同一時鐘對這4路驅動信號進行控制,以保證相互之間的確定時間關系,然后使用分頻器對時鐘脈沖分頻以產生各路驅動信號所需的波形,產生如圖1所示的驅動信號就方便得多。

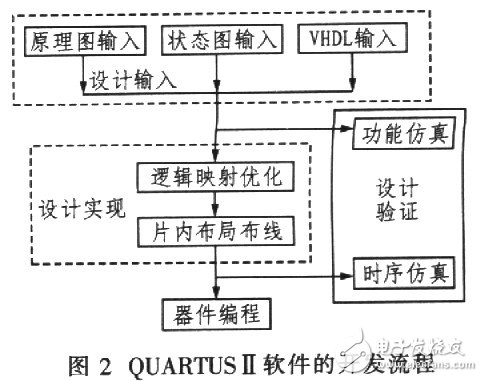

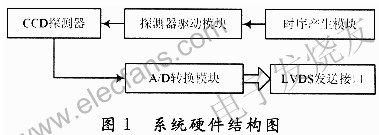

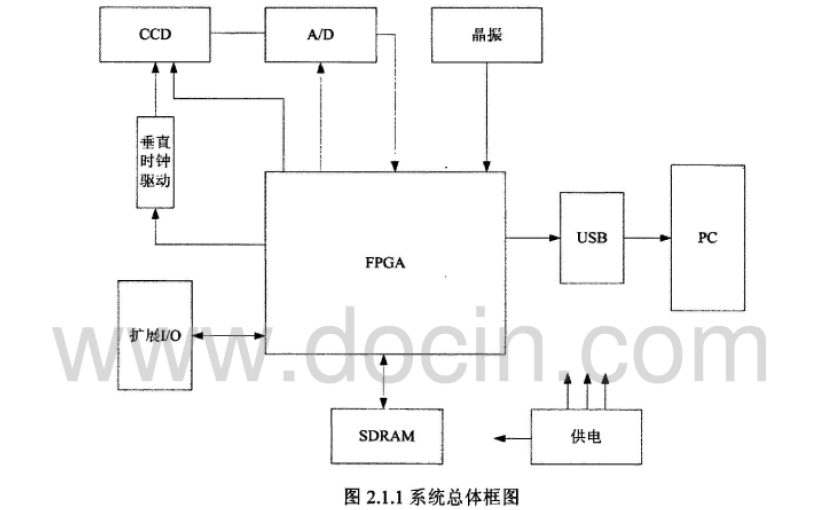

該系統的設計采用Altera公司的QUARTUSⅡ開發系統。QUARTUSⅡ開發系統是一種全集成化的可編程邏輯設計環境,它支持硬件描述語言(VHDL)、狀態圖和原理圖三種輸入方式,執行編譯、邏輯綜合、仿真以及編程等功能。設計過程包括4個階段:設計輸入、設計實現、設計驗證和器件編程,如圖2所示。整個流程是一個輸入、實現、驗證的遞歸過程,直到設計正確和完整。

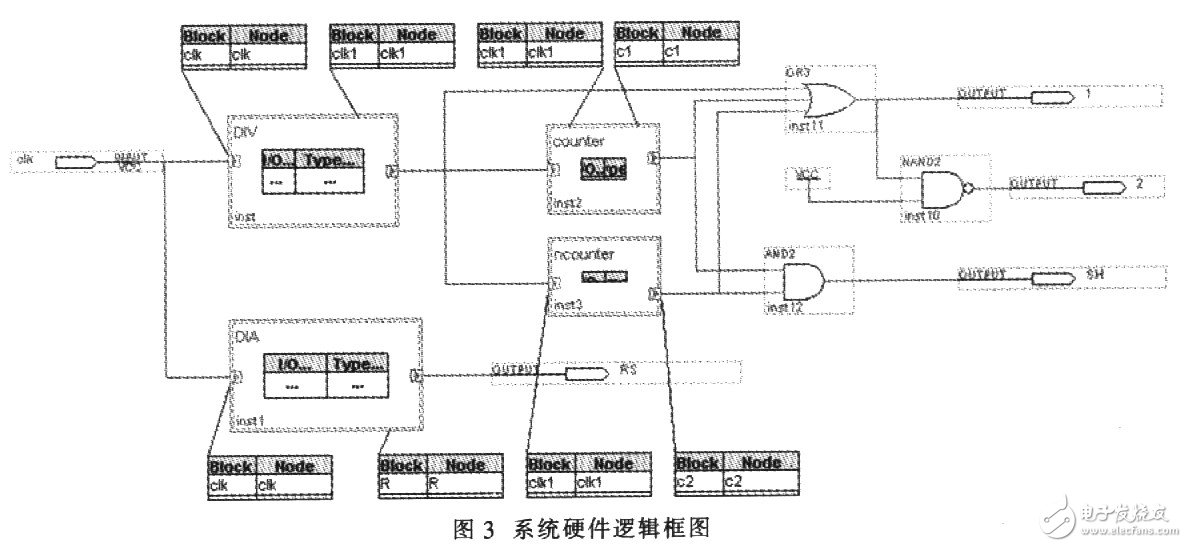

原理圖輸入方式簡單直觀,也是最常用的。如采用硬件描述語言的輸入方式如VHDL或Verilog,其可移植性和可讀性都好,但綜合形成的數據格式文件往往比原理圖輸入方式更占可編程器件的資源。為了提高芯片的利用率,同時采用原理圖輸入方式還可以生成新的特殊功能模塊,鑒于系統規模不大,因此采用原理圖輸入方式進行本系統的設計。由于TCDl208AP是二相驅動方式,根據TCDl208AP驅動信號的時序關系,可以確定φl=φ2=0.5 MHz,輸出復位脈沖RS=l MHz。

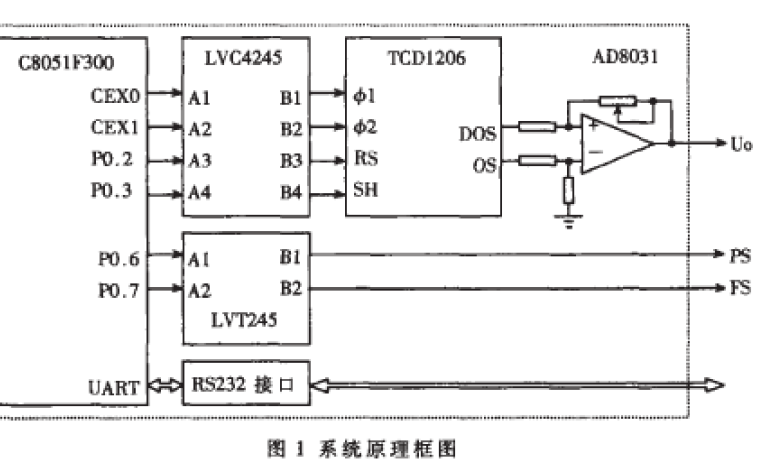

在確定了SH、φ1、φ2和RS的參數后,可以根據它們之間的時序關系設計硬件邏輯框圖。各路脈沖分別為RS=1 MHz,占空比為l:4,方波;φ1=φ2=0.5 MHz,占空比為1:l,方波,φ1、φ2在并行轉移時有一個大于SH=1的寬脈沖。其中的各個模塊采用VHDL語言進行設計,如圖3所示。

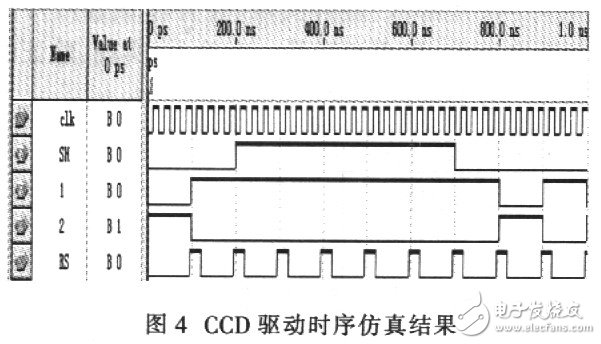

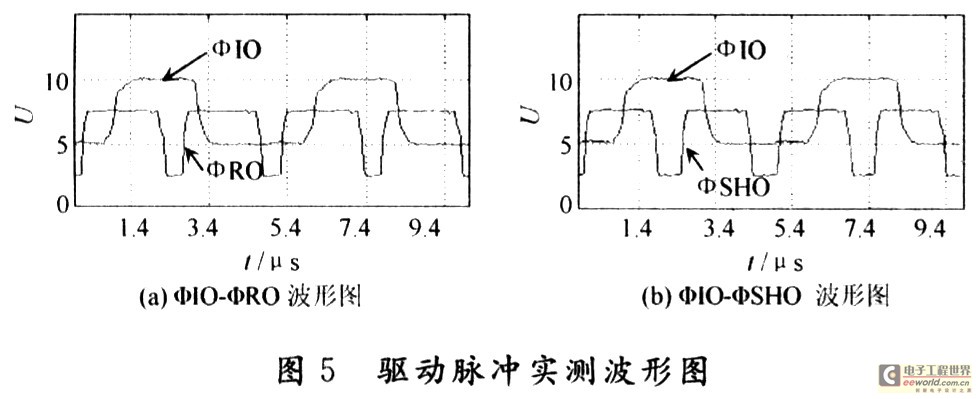

編譯后,最后得到仿真的波形結果如圖4所示。

5 、結束語

本設計采用QUARTUSⅡ開發系統實現編程,完成了電路功能的設計、時序綜合與分析及文本和圖形輸入,并根據工程需要將結果下載到Altera公司的Cyclone系列FPGA芯片EPlCl2Q240C8中產生CCD驅動時序,不但得到了良好的CCD輸出效果,而且大大簡化電路設計,提高可靠性,降低功耗,加快研發速度。

-

傳感器

+關注

關注

2565文章

53008瀏覽量

767483 -

FPGA

+關注

關注

1645文章

22050瀏覽量

618526 -

驅動電路

+關注

關注

155文章

1585瀏覽量

109956

發布評論請先 登錄

基于DSP和FPGA的CCD圖像采集系統設計與實現

采用FPGA的高速CCD相機的時鐘發生器

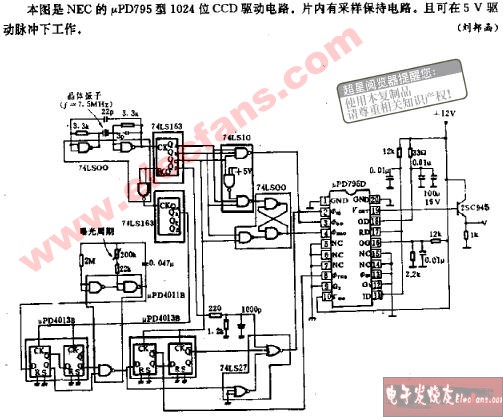

基于μPD795的CCD相機系統中驅動電路的設計

基于DSP和FPGA的CCD圖像采集系統設計與實現

CPLD實現線陣CCD驅動電路

使用FPGA實現線陣CCD驅動時序及模擬信號處理的設計說明

CCD驅動電路的4種常用方式介紹和使用單片機設計CCD驅動電路的說明

如何使用FPGA實現全幀CCD驅動的設計

采用QUARTUSⅡ開發系統實現CCD驅動電路的設計

采用QUARTUSⅡ開發系統實現CCD驅動電路的設計

評論