大部分FPGA采用基于SRAM(靜態(tài)隨機(jī)存儲(chǔ)器)的查找表邏輯形成結(jié)構(gòu),就是用SRAM構(gòu)成邏輯函數(shù)發(fā)生器。SRAM工藝的芯片在掉電后信息就會(huì)丟失,需要外加一片專用配置芯片。在上電時(shí),由這個(gè)專用配置芯片把數(shù)據(jù)加載到FPGA中,然后FPGA就可以正常工作。這就是在線可重配置ICR(In-Circuit Reconfigurability)方式。

Altera公司生產(chǎn)的具有ICR功能的APEX、FLEX10K、ACEX、FLEX6000等系列器件可以使用6種模式進(jìn)行配置,即使用專用EPC配置器件、被動(dòng)串行(PS)方式、被動(dòng)并行同步(PPS)方式、被動(dòng)并行異步(PPA)方式、被動(dòng)串行異步(PSA)方式及邊界掃描(JTAG)方式。這些模式由FPGA上的兩個(gè)模式選擇引腳MSEL1和MSEL0上的電平來決定。

EPC配置器件有一次性可編程和可擦寫編程型兩種。一次性可編程型芯片不適于調(diào)試、修改及產(chǎn)品升級(jí),利用率不高;可擦除編程型芯片價(jià)格昂貴,容量有限。使用PS、PPS、PPA方式配置時(shí),配置文件要以二進(jìn)制形式保存在系統(tǒng)ROM中,然后通過微處理器將配置數(shù)據(jù)送進(jìn)FPGA中。PS和PPS所用的配置時(shí)間幾乎相同,而PS的接口方式比較簡(jiǎn)單。PPA方式與PPS不一樣的地方是在進(jìn)行串行化處理時(shí)不需要配置外部時(shí)鐘的驅(qū)動(dòng),但接口更復(fù)雜。邊界掃描方式在現(xiàn)場(chǎng)采用較少,通常用在計(jì)算機(jī)通過JTAG口實(shí)現(xiàn)一次性編程數(shù)據(jù)加載的調(diào)試中。 以上6種模式中被動(dòng)串行(PS)方式下FPGA與配置電路的互連最簡(jiǎn)單,對(duì)配置時(shí)鐘的最低頻率也沒有限制,因此常采用PS模式。本文采用單片機(jī)P89C61X2以PS模式對(duì)Altera公司的FLEX10K系列芯片EPF10K20進(jìn)行配置,軟件采用MAX+PLUS II。

1 P89C61X2的功能特點(diǎn)

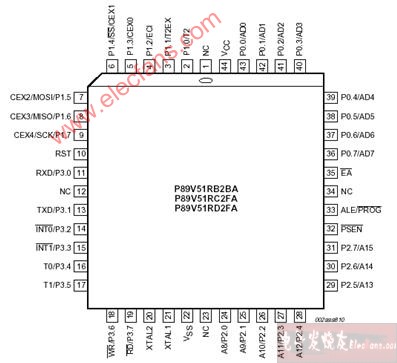

P89C61X2器件采用高性能的靜態(tài)80C51設(shè)計(jì),使用先進(jìn)的CMOS工藝制造,并包含非易失性Flash的程序存儲(chǔ)器,可通過并行編程或在系統(tǒng)編程(ISP)的方法進(jìn)行編程。支持6時(shí)鐘和12時(shí)鐘模式,相應(yīng)地有2種速度范圍:6時(shí)鐘模式時(shí),0~20 MHz;12時(shí)鐘模式時(shí),0~33 MHz。

P89C61X2包含64 KB的Flast程序存儲(chǔ)器、1 024字節(jié)RAM、32個(gè)I/O口、3個(gè)16位定時(shí)/計(jì)數(shù)器、6中斷源-4中斷優(yōu)先級(jí)-嵌套的中斷結(jié)構(gòu)、1個(gè)增強(qiáng)型UART、片內(nèi)振蕩器和時(shí)鐘電路等。此外,器件的靜態(tài)設(shè)計(jì)使其具有非常寬的頻率范圍,甚至可以降低至零。P89C61X2具有兩種軟件可選的節(jié)電模式--空閑模式和掉電模式。空閑模式時(shí)凍結(jié)CPU的運(yùn)行,但允許RAM、定時(shí)器串口和中斷系統(tǒng)繼續(xù)保持其功能;掉電模式時(shí)保持RAM的內(nèi)容,但凍結(jié)振蕩器,使其他片內(nèi)功能都停止工作。由于是靜態(tài)設(shè)計(jì),時(shí)鐘停止也不會(huì)使用戶數(shù)據(jù)丟失。操作可從時(shí)鐘停止點(diǎn)恢復(fù)運(yùn)行。

P89C61X2的Flash存儲(chǔ)器增加了EPROM所沒有的電可擦除和編程特性,可以進(jìn)行芯片擦除和塊擦除。芯片擦除操作是將整個(gè)程序存儲(chǔ)區(qū)都擦除;而塊擦除可實(shí)現(xiàn)對(duì)任意Flash塊進(jìn)行擦除。對(duì)P89C61X2進(jìn)行在系統(tǒng)編程和標(biāo)準(zhǔn)的并行編程都是可行的。片內(nèi)產(chǎn)生的擦除和寫入時(shí)序?yàn)橛脩籼峁┝肆己玫木幊探涌凇89C61X2的Flash存儲(chǔ)器甚至在經(jīng)過10 000次擦除和編程之后仍能可靠地保存存儲(chǔ)器內(nèi)容。使用+5 V的Vpp即可實(shí)現(xiàn)對(duì)其進(jìn)行擦除和編程。

2 配置原理和配置文件

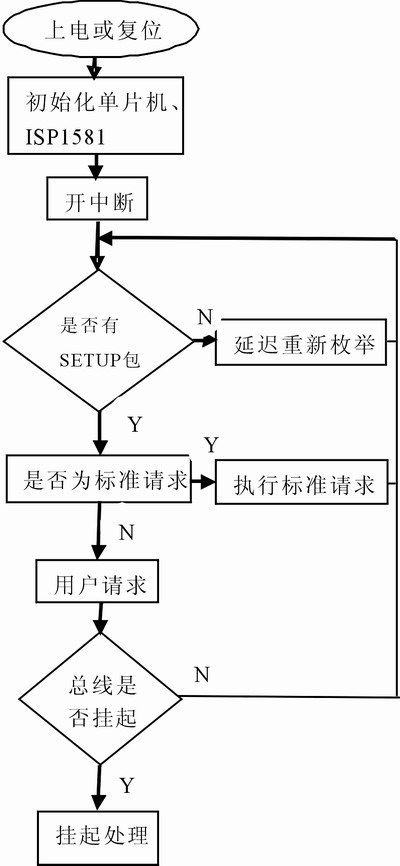

用單片機(jī)通過PS模式配置FPGA,可以使用單片機(jī)的普通輸入/輸出(I/O)口(如圖1(a)所示)或串行口(如圖1(b)所示)來實(shí)現(xiàn)。配置中使用了FPGA的nCONFIG(配置控制位輸入端)、nSTATUS(配置錯(cuò)誤指示位輸出端)、CONF_DONE(配置結(jié)束標(biāo)志位輸出端)、DCLK(配置時(shí)鐘輸入端)、DATA0(配置數(shù)據(jù)輸入端)引腳等。nCEO引腳用于多個(gè)FPGA器件采用PS模式配置時(shí),把第一片的nCEO連接到下一片的nCE引腳上。配置時(shí)若使用普通I/O口(如P1口),向FPGA發(fā)送1位數(shù)據(jù)至少需要4個(gè)指令周期:一個(gè)指令給DATA0賦值,兩個(gè)指令產(chǎn)生DCLK時(shí)鐘,一個(gè)指令移位取數(shù)據(jù)。如果晶振頻率為fosc,一個(gè)指令周期為12/fosc,那么它的下載速率為fosc/48。如果采用串行口方式0,其下載速率提高為fosc/12。P89C61X2支持6時(shí)鐘模式,速度可以提高一倍。

在配置過程中,nCONFIG低電位使EPF10K20復(fù)位,在由低到高的跳變過程中啟動(dòng)配置;加電后,EPF10K20驅(qū)動(dòng)nSTATUS引腳到低電位,然后釋放它(nSTATUS必須經(jīng)過1 kΩ電阻上拉到VCC,若配置期間出錯(cuò),EPF10K20將其拉低),每個(gè)數(shù)據(jù)由最低位(LSB)先送出給DATA0,數(shù)據(jù)時(shí)鐘DCLK同時(shí)送到器件,直到CONF_DONE變高。在所有數(shù)據(jù)傳輸完后,對(duì)于FLEX10K和FLEX6000器件,DCLK必須多送10個(gè)DCLK脈沖;APEX20K器件必須多送40個(gè)DCLK脈沖。EPF10K20的CONF_DONE變高顯示配置成功,開始初始化,最后進(jìn)入用戶模式,開始正常工作。由于PS模式中沒有握手信號(hào),因此配置時(shí)鐘的工作頻率必須低于10 MHz,如果想在配置中中止,可以掛斷DCLK。硬件描述語言生成的程序經(jīng)MAX+PLUS II編譯后會(huì)產(chǎn)生一個(gè)后綴為.sof的SRAM目標(biāo)文件。該文件除配置數(shù)據(jù)外還含有控制字符,不能直接寫人到PLD中去,需要利用MAX+PLUS II的編程文件轉(zhuǎn)換功能。例如有些編程器支持.rbf文件。.rbf文件為原始二進(jìn)制文件,該文件包括所有的配置數(shù)據(jù),配置文件的大小一般由它決定。1字節(jié)的.rbf文件有8位配置數(shù)據(jù),每一字節(jié)在配置時(shí)最低位最先被裝載。不同系列的目標(biāo)器件配置數(shù)據(jù)的大小也不同,如.rbf文件在FLEK系列中,EPF10K10為15 KB,EPF10K20為29 KB,EPF10K30為46 KB,EPF10K40為61 KB,EPF10K70為109 KB等。由于P89C61X2包含64 KB Flash程序存儲(chǔ)器,可以對(duì)除EPF10K70外的其他器件實(shí)現(xiàn)配置,而大干61 KB的FPGA器件可采用擴(kuò)展存儲(chǔ)器的方法來實(shí)現(xiàn)。

MAX+PLUS II不自動(dòng)生成.rbf文件,須按照下面的步驟生成:①在MAX十PLUS II編譯狀態(tài)下,選擇文件菜單的變換SRAM目標(biāo)文件命令;②在變換SRAM目標(biāo)文件對(duì)話框中指定要轉(zhuǎn)換的文件并且選擇輸出文件格式為.rbf,然后確定。

針對(duì)單片機(jī)P89C61X2,可以通過在系統(tǒng)編程(ISP)的方法實(shí)現(xiàn)。這里采用廣州致遠(yuǎn)電子有限公司開發(fā)的在線編程下載軟件ZLGICD。該軟件支持.hex文件。.hex文件為十六進(jìn)制文件,MAX+PLUS II編譯時(shí)會(huì)自動(dòng)生成該文件,如果沒有也可采用類似產(chǎn)生.rbf文件的方法生成。

用P89C61X2來配置FPGA,需將引導(dǎo)配置代碼(.hex文件)和FPGA的配置數(shù)據(jù)(.hex文件)一起通過編程器寫入P89C61X2。配置數(shù)據(jù)需要改變現(xiàn)有地址來讓引導(dǎo)程序調(diào)用,否則會(huì)造成沖突。可以自己編寫一個(gè)小程序來實(shí)現(xiàn)此功能。注意.hex文件的格式。由于引導(dǎo)配置代碼不長(zhǎng),通常小于1 KB,因此有足夠的空間來存放配置數(shù)據(jù)。

3 軟件設(shè)計(jì)

軟件編程時(shí),本系統(tǒng)只用到了串行口移位寄存器的輸出方式,串行數(shù)據(jù)通過RXD引腳輸出,移位時(shí)鐘由TXD引腳輸出。當(dāng)有一個(gè)字節(jié)數(shù)據(jù)寫入串行數(shù)據(jù)緩沖器SBUF時(shí),開始發(fā)送。而串行口輸出方式本身就滿足配置時(shí)最低位(LSB)先送出的要求。下面給出用C語言編寫的子程序:

uchar fpga_config(uint Address){

uchar reconfig=0;

uchar j;

init;

nconfig=0;

delay-ms(1);

nconfig= 1;

reconfig++;

while(1){

SBUF = CBYTE[Address++];

while(TI==0);

TI=0;

if(!nstatus){

delay_ms(10);

goto init;

if (reconfig 》0x05) return 0;

if (confdone){

for(j=0;j《5;j++){

SBUF = CBYTE[Address++];

while(TI==0);

TI=0;

}

return 1;

}

}

}

結(jié) 語

用P89C61X2單片機(jī)來配置FPGA,從價(jià)格上來看,要優(yōu)于EPC配置器件;從時(shí)間上來看,采用串行口方式0配置EPF10K20不到1秒鐘,而用單片機(jī)的普通輸入/輸出口方式要慢許多;從使用上來看,不擴(kuò)展存儲(chǔ)器使電路連線更加簡(jiǎn)單。另外,單片機(jī)與FPGA優(yōu)勢(shì)相結(jié)合也給產(chǎn)品開發(fā)提供了更多更優(yōu)的選擇方案。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22036瀏覽量

618088 -

單片機(jī)

+關(guān)注

關(guān)注

6067文章

44976瀏覽量

650202 -

發(fā)生器

+關(guān)注

關(guān)注

4文章

1404瀏覽量

62818

發(fā)布評(píng)論請(qǐng)先 登錄

基于單片機(jī)AT89C51的MP3播放系統(tǒng)的設(shè)計(jì)方案

采用控制芯片P89C61x2和接口芯片ISP1581實(shí)現(xiàn)USB接口電路設(shè)計(jì)

如何采用控制芯片P89C61x2和接口芯片ISP1581實(shí)現(xiàn)USB接口電路的設(shè)計(jì)?

P89C51X2/P89C51X2/P89C52X2/P89

P89C51Rx+/Rx2/66x系列單片機(jī)的在線編程

基于單片機(jī)AT89C51的MP3播放系統(tǒng)的設(shè)計(jì)方案

PHILIPS P89C5x單片機(jī)數(shù)據(jù)手冊(cè)

采用P89C61x2和ISP1581的USB接口電路的設(shè)計(jì)

基于P89V51RD2單片機(jī)LED點(diǎn)陣顯示屏的實(shí)現(xiàn)

基于單片機(jī)與FPGA可調(diào)延時(shí)模塊的設(shè)計(jì)

AT89C51單片機(jī)

基于AT89C51單片機(jī)的語音播報(bào)器的設(shè)計(jì)方案

利用P89C61X2單片機(jī)配置FPGA,提供更優(yōu)的設(shè)計(jì)方案

利用P89C61X2單片機(jī)配置FPGA,提供更優(yōu)的設(shè)計(jì)方案

評(píng)論