引 言

隨著消費類電子,如MP3、3G手機、視頻終端以及寬帶無線網絡的普及,對大容量存儲設備的需求越來越強烈。傳統的SRAM、SDRAM以及DDR SDRAM等存儲設備的價格與容量比,遠遠比硬盤高;光存儲設備雖然更加廉價,但是在便攜性上卻遠遜于硬盤解決方案。現在硬盤廠商提供了各種適用于不同用途的廉價海量存儲設備,如1 in(英寸)的微硬盤可以應用于各種小巧的便攜設備中,2.5in硬盤可以應用于筆記本和移動存儲中,3.5in硬盤可以應用于個人PC和工業自動化中等等。

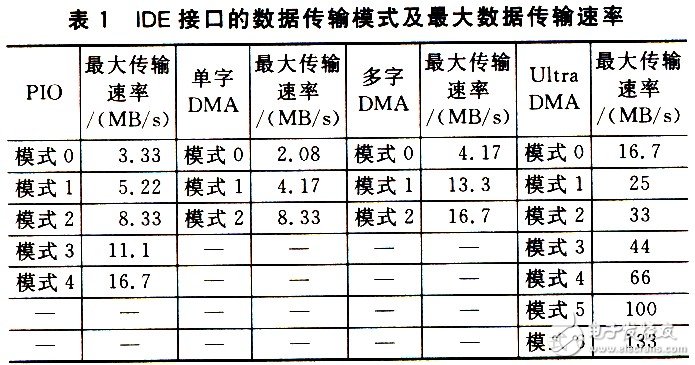

目前,硬盤支持的最為廣泛的IDE接口協議中,規定了PIO、DMA以及Ultra DMA三種數據傳輸模式,其傳輸速率PIO《多字DMA《Ultra DMA,如表1所列。隨著各種多媒體應用的廣泛普及,各種設備不但要求擁有海量存儲能力,在完成各種實時業務時對數據的傳輸速率也提出了嚴格的要求。

現階段的設計研究主要集中于單邊沿鎖存數據的PIO和DMA傳輸模式。大多數設計主要用PIO模式完成控制命令的寫入和讀取操作,采用DMA數據傳輸模式進行直接內存讀取操作,提高數據傳輸的速率。如果在相同系統中使用Ultra DMA數據傳輸模式,則可以在不提高系統時鐘頻率的基礎上,將系統數據傳輸速率提高l倍,極大地改善了系統性能,而不需要付出更多的硬件資源。因而硬盤的Ultra DMA數據傳輸方式在工業自動化、Internet網絡、消費類電子和各種嵌入式系統中的需求會不斷增加,有著很好的商業前景。

1 Nios系統介紹

該設計是在Altera公司推出的Nios嵌入式系統的平臺上,設計可以通過Ultra DMA數據傳輸方式進行高速硬盤讀寫的接口模塊,并開發出相應的IP核。

1.1 Nios系統結構

Nios嵌入式處理器系統通常由N1os處理器、Avalon交換結構總線和各種外圍設備(存儲、接口及功能模塊)的IP核三部分構成。Altera的SOPC Builder系統開發工具可以自動生成這些組件以及連接它們的總線。

Nios處理器是32位結構可配置并包含五級流水線的通用RISC微處理器,采用改進的哈佛存儲器結構;處理器帶有分離的數據和程序存儲器總線控制,具備高速緩存、中斷處理功能。與傳統處理器相比,Nios指令系統可通過自定義指令和標準處理器選項,利用硬件來明顯提高系統性能。

Avalon交換結構總線是Altera開發的用于Nios嵌入式處理器的參數化接口總線,由l組預定義的信號組成,用這些信號可以連接1個或多個IP模塊。Altera的S0PC Builder系統開發工具自動地產生Avalon交換結構總線邏輯,其實現只需要極少的FPGA資源,提供完全同步的操作。

Nios嵌入式處理器系統中的各種存儲模塊、接口模塊和功能模塊等都在Altera的標準外圍設備庫中以IP核的方式提供使用,或是由用戶自行設計添加到庫中,以IP模塊的方式在系統中復用。

實現硬盤高速訪問功能模塊的設計,實際上是在設計一個完整的IP模塊,再在Altera提供的SOPC Builder開發環境的設備庫中集成該IP核,以達到設計的目的。

1.2采用Nlos軟核處理器構建系統的原因

①與其他的實現方式相比有著更好的性能價格比。最常見的硬盤讀取控制和數據傳輸方式是通過單片機或是DSP來實現的,使用單片機或DSP中的PIO接口可以很方便地完成單邊沿鎖存數據的硬盤PIO和DMA數據傳輸方式,但在實現雙邊沿鎖存數據的Ultra DMA傳輸方式時,必須在單片機和DSP芯片外添加額外的FPGA芯片,完成Ultra DMA雙邊沿鎖存數據到單邊沿鎖存數據的轉換,增加了系統設計的成本和復雜性。而采用Nios軟核處理器完成與硬盤的Ultra DMA傳輸方式時,不需要添加任何額外的芯片,僅使用FPGA內的其他資源就可以方便地實現雙邊沿到單邊沿的轉換工作。

②與傳統的單片機或DSP實現方式相比,Nios嵌入式系統的設計與實現更加簡單。從性能上來說,Nios軟核處理器與ARM、Intel等的CPU處于同一級別,都能夠滿足設計的需要,即使是復雜邏輯系統的設計也可以在一片Cyclone或是StratiX芯片上實現全部功能。而且通過使用Altera公司提供的SOPC Builder開發工具,在IP復用的基礎上可以快速開發出完整的系統解決方案。

③與傳統的單片機或DSP實現方式相比,Nios嵌入式系統的可擴展性更好。單片機或DSP內的資源是硬件廠商固化在芯片內的,用戶不可能自行添加或刪減,在設計時的靈活性受到器件本身的限制;而Nios軟核處理器的所有資源都可以任意地添加或刪減,只需最終通過電纜下載到FPGA芯片內就可定制出整個系統的功能。因而在基于Nios的系統設計中,通過對設計文件的修改就可以很方便地進行系統功能的擴展。

2 系統的硬件實現

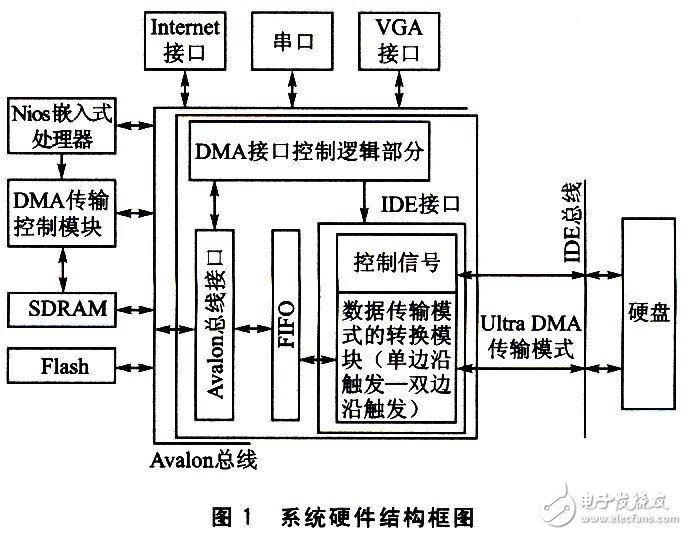

硬件部分由Nios嵌入式系統、Nios與硬盤的接口模塊和其他外圍接口電路三部分組成,如圖1所示。其中設計的核心部分是Nios系統與硬盤接口模塊的IP核設計,主要完成數據傳輸模式的轉換,以及對硬盤的控制與操作兩部分任務。Nios嵌入式處理器系統的任務是進行整體控制與協調,并對數據進行處理和暫存;外圍接口電路主要用來擴充系統的功能,擴大系統的適用范圍。

Nios嵌入式處理器系統由Nios嵌入式處理器、DMA控制器、數據存儲區SDRAM、程序存儲區F1ash和Avalon總線構成。其中DMA控制器用于實現兩個存儲器之間,或者存儲器和外設之間,或者是兩個外設之間的直接數據傳輸。DMA模塊用于連接支持流模式傳輸的外設,并允許定長或變長的數據傳輸,而不需要CPU的干涉。在Ultra DMA數據傳輸的過程中,可以一次性傳輸最多256個扇區的數據,所以在系統中使用DMA控制器可以方便地在硬盤與系統中各種支持流傳輸模式的設備之間建立直通連接,提高系統的數據傳輸效率。

外圍接口電路主要用于系統功能的擴充,如Internet接口可以使系統方便地接人到網絡中提供諸如音樂或視頻下載、信息共享等服務;串口用于與計算機或其他設備的互連;VGA接口用于視頻信號的輸出,在系統外部顯示圖像等等。

硬盤接口部分主要由接口控制邏輯、Avalon總線接口、FIFO和硬盤IDE接口4部分組成。其中接口控制邏輯部分用于對Nios處理器的指令進行譯碼并執行相應的操作,控制Ultra DMA傳輸時的握手和控制信號的產生,協調數據傳輸過程中IDE接口的硬盤數據速率同Avalon總線接口速率的匹配。

FIFO用于數據的緩沖,解決Avalon總線和IDE接口之間的數據速率不匹配問題。在設計中需要對硬盤UltraDMA的六種數據傳輸模式同時提供支持,而其傳輸速率卻完全不同,必須添加緩沖區用于數據的暫存。

Avalon總線接口用于與Nios處理器系統相連,傳輸Nios處理器的指令給控制邏輯部分,以及與系統中的其他部分在DMA控制器的協調下完成數據的傳輸。

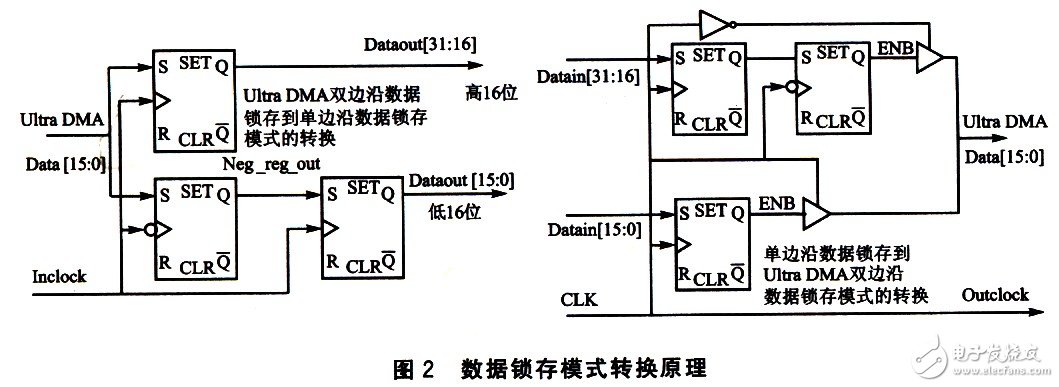

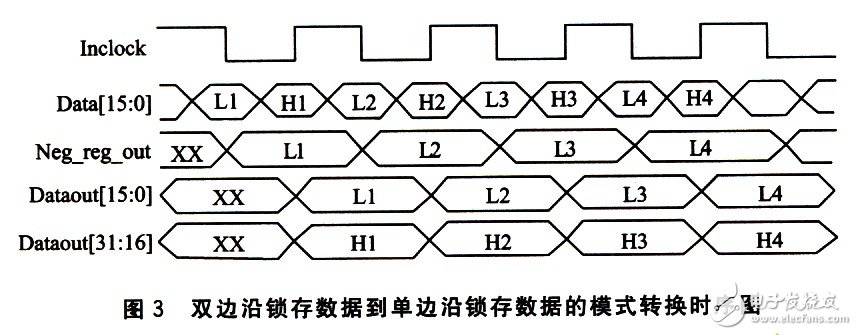

硬盤IDE接口部分除輸出控制信號并對硬盤返回的信號做出響應外,還要完成單邊沿數據鎖存模式與雙邊沿數據鎖存模式相互轉換的任務,如圖2、圖3所示。

由于Nios系統內部數據傳輸時,都使用時鐘上升沿來鎖存數據;而IDE總線上傳輸的Ultra DMA數據,在Clock信號的上升沿和下降沿都有數據需要鎖存。因而硬盤接口部分兩側的數據,在傳輸時工作模式各不相同,需要進行必要的緩沖和模式轉換。

數據鎖存模式轉換模塊,用于在IDE總線上雙邊沿鎖存數據和系統內部單邊沿鎖存數據之間進行鎖存模式的轉換,這是系統設計的核心問題之一。具體來說,就是在讀取硬盤數據時需要將IDE總線上傳輸的雙邊沿鎖存數據轉換為系統內部使用的單邊沿鎖存數據;在寫硬盤操作時完成相反的任務。在設計時采用兩組寄存器對不同時鐘沿的信號進行鎖存,在時鐘頻率不變的基礎上,通過數據帶寬的擴展,完成雙邊沿到單邊沿的轉換功能;在單邊沿數據到雙邊沿數據的轉換過程中,采用相反的構架。

3 系統工作流程

系統在完成基于Ultra DMA的數據傳輸模式的硬盤訪問功能時,需要實現對硬盤數據通過Ultra I)MA模式進行的讀操作和寫操作。其具體的工作流程各不相同,主要區別在于:

①Nios系統內部的協調過程。作為系統處理核心的Nios處理器,必須向硬盤接口邏輯和DMA控制器中發送指令,使其按照設計要求執行相應的操作。向硬盤接口邏輯部分發送讀寫硬盤的指令時,需要首先命令讀操作時使用FIFO對硬盤數據進行緩沖,在寫操作時將FIFO中的緩沖數據發送到硬盤中完成寫入操作;向DMA控制器部分發送指令,協調接口緩沖區FIFo和系統內存SDRAM中數據的交互過程,以完成對硬盤的讀寫操作。

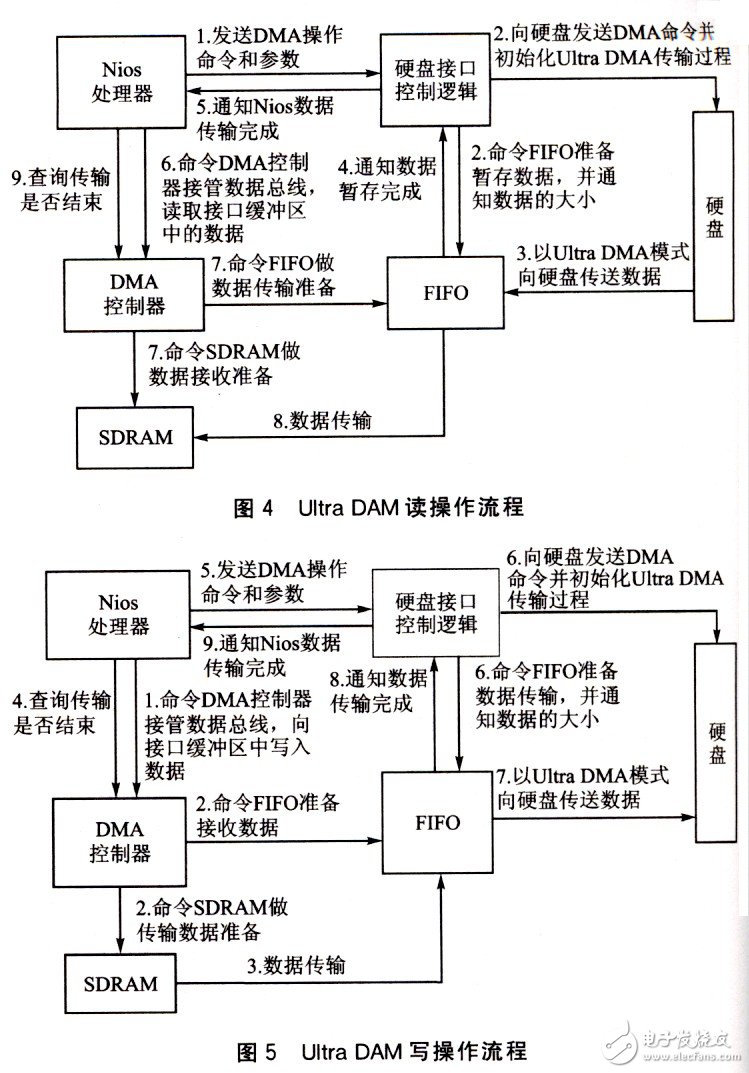

②對硬盤的讀寫訪問操作。在對硬盤進行讀寫操作時,必須向硬盤的接口寄存器中發送DMA讀指令或寫指令,其指令碼和操作順序也不盡相同,如圖4、圖5所示。

4 系統的軟件實現

在Nios SDK Shell環境下,使用帶Monitor的bootloader程序,可以在程序Debug的同時監控內部存儲器的變化,便于硬件設計的檢查和程序的調試。軟件的編寫主要采用C語言,部分嵌入了匯編語言。整個系統軟件設計中的重點是以下兩部分。

(1)Nios系統內DMA控制器的編程

在DMA傳輸過程中需要完成的操作有:①配置DMA控制器;②軟件啟動DMA外設,開始DMA傳輸;③DMA控制器的主設備讀端口從目標地址讀取數據,主設備寫端口向目標地址寫入數據;④DMA傳輸結束。

這一過程中,需要向DMA控制器的寄存器中寫入控制指令來開啟一次數據傳輸過程。要求初始化的寄存器有:status、readaddress、wi rte£Jddress、length和contiol。之后調用系統提供的DMA子程序開啟一次DMA操作,使用的DMA子程序有:nr_dma_opy_1_tO_rarlge(在原地址和目標地址之間,傳輸length長度的數據,原地址固定,而目標地址在每次傳輸后增加),用于完成數據讀取操作時,從FIFO緩沖區中向SDRAM里傳輸數據;nr_dma_copy_range_to_l(在原地址和目標地址之間,傳輸lengt長度的數據,目標地址固定,而原地址在每次傳輸后增加),用于完成數據寫操作時,從SDRAM里向FIFO中緩沖數據。

(2)硬盤的DMA讀寫命令

在對硬盤進行讀寫操作時須向硬盤的寄存器內寫入DMA讀指令(或寫指令)和相應參數后才可對硬盤中的數據進行訪問。在ATAPI 協議中規定了READ DMA指令和WRITE DMA指令的命令格式,需要向SectorCbunt、SectorNulmber、CyclindeLow、CyblindelrHigh、Device/Head、Command寄存器中寫入參數和命令代碼。其中讀指令的代碼是C8h、寫指令的代碼是CAh。在寫入命令后就可以對硬盤中的數據進行讀寫操作。

結 語

本系統使用Nios嵌入式系統在單芯片內實現了數據處理、存儲訪問、數據模式轉換等多個功能。采用Altera公司提供的Quartus II 和 SOPC Builder開發工具可以在完成接口功能設計后,快速進行系統的集成設計和系統仿真,最終可以在Altera提供的Cyclone系列芯片上實現整個系統設計。對Nios處理器重新編程可以在不改變系統硬件框架的基礎上,方便地增加系統的功能和處理效率,對系統的升級和再開發有很大的便利。

責任編輯:gt

-

芯片

+關注

關注

459文章

52386瀏覽量

439128 -

嵌入式

+關注

關注

5147文章

19616瀏覽量

316462 -

無線網絡

+關注

關注

6文章

1466瀏覽量

66929

發布評論請先 登錄

基于 DSP-dMAX 的嵌入式 FIFO 數據傳輸系統設計

基于單片機和GPRS模塊的嵌入式無線數據傳輸終端的實現方案

DMA進行數據傳輸和CPU進行數據傳輸的疑問

數據傳輸的通信系統設計

基于嵌入式TCP IP的實時數據傳輸

嵌入式GPRS數據傳輸終端設計

DMA數據傳輸(源代碼分享)

DMA數據傳輸在SPEAR300實現高速串口驅動設計

使用Nios嵌入式系統在單芯片上完成Ultra DMA數據傳輸模式的訪問

使用Nios嵌入式系統在單芯片上完成Ultra DMA數據傳輸模式的訪問

評論