大家在對一些數(shù)據(jù)總線處理等長的時候,都知道要同組同層,除了免去過孔帶來的傳輸延時之外,微帶線和帶狀線由于信號傳輸速度的不同,同樣長度的走線延時也是有差別。我們繞等長的最終目的是為了滿足時間上的等長而不是單純走線長度上的物理等長。到底微帶線和帶狀線延時上的差別有多大,繞等長的時候過孔的長度要不要算進(jìn)去,可能有個具體的數(shù)據(jù)會更直觀點(diǎn)。下面我們來將這些數(shù)據(jù)進(jìn)行估算和量化。

1.微帶線和帶狀線傳輸時延

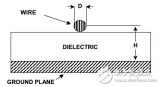

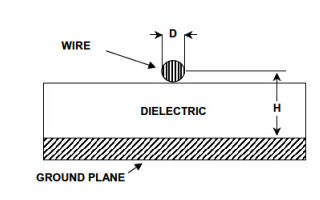

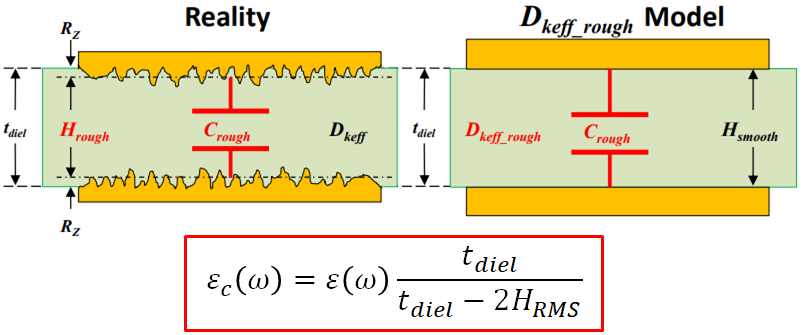

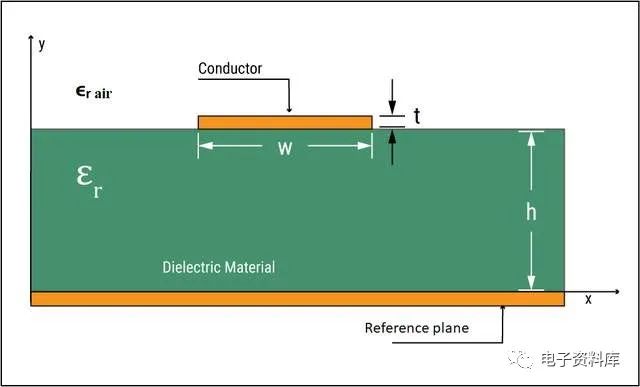

PCB中微帶線是指走線只有一個參考面,帶狀線是指走線有兩個參考面。帶狀線由于電磁場都被束縛在兩個參考面之間的板材中,所以走線的有效介電常數(shù)為板材的介電常數(shù)。微帶線會導(dǎo)致部分電磁場暴露在空氣中,空氣的相對介電常數(shù)約為1.0006,板材如常規(guī)FR4的介電常數(shù)為4.2,那么微帶線的有效介電常數(shù)在1和4.2之間。

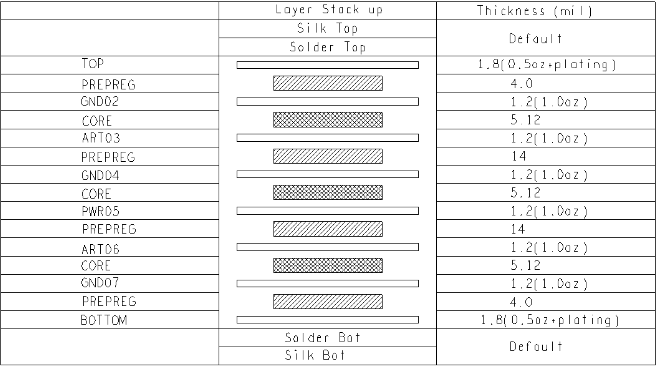

現(xiàn)在以特定的FR4板材和層疊結(jié)構(gòu)來量化微帶線和帶狀線的傳輸延時。

1.微帶線層疊和時延

2.帶狀線層疊和時延

注意一下,時延的單位為ps/in。從上面兩個圖中可以看到1000mil的走線,微帶線的時延為149.668ps,帶狀線的時延為173.635ps。1000mil的走線,帶狀線和微帶線的時延差為173.635ps-149.668ps=23.967ps。這個差距還是非常大的,在繞DDR的數(shù)據(jù)線的時候,如果數(shù)據(jù)線走線不同層,對于DDR的源同步時鐘系統(tǒng)來說,所謂的物理等長會帶來嚴(yán)重的時序問題。

3.過孔時延

經(jīng)過一些數(shù)據(jù)的量化,微帶線和帶狀線的傳輸延時有很明顯的差距,有了這個數(shù)據(jù),有的同學(xué)可能會對同組同層的要求認(rèn)識會更深刻。對于一些等長要求不是很嚴(yán)格的走線來說,比如說ddr的地址線,并沒有同組同層的要求。不同層的信號除了信號不同層帶來的時延差之外還相差了一個過孔的長度,這段長度嚴(yán)格來說也是要算進(jìn)去的。

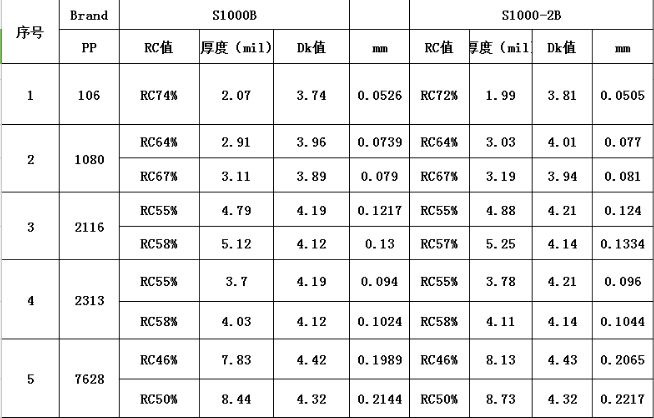

來對比一下1.6mm長的過孔和走線時延差距有多大。

過孔的延時可以用一個很簡單的公式來進(jìn)行估算:

Td_via=

L表示過孔的寄生電感,C表示過孔的寄生電容,這兩個參數(shù)都會導(dǎo)致過孔的傳輸延時變大。獲取過孔的寄生電感和寄生電容很簡單,如下圖。

上圖的過孔結(jié)構(gòu)根據(jù)過孔的時延估算公式可計(jì)算出

Td_via==sqr(0.4021pf*1326.2pH)=23.1ps

而對于普通FR4板材的微帶線,1.6mm走線傳輸延時約為11ps,對于帶狀線約為12.5ps。所以相同長度的走線和過孔之間的時延差是非常大的。

電磁信號或者光信號在傳輸介質(zhì)中的傳輸速度也可用以下簡化公式進(jìn)行估算:

V:電磁信號或者光信號在傳輸介質(zhì)中的傳輸速度

C:光速,

Dk:傳輸介質(zhì)的介電常數(shù),對于常規(guī)FR4板材來說就是2。

所以信號在PCB上的傳輸速度≈6mil/ps。

所以特別是對我們目前等長規(guī)則越來越嚴(yán)格的情況下:

(1)需要做等長的信號要盡量走同層,換層時需要注意總的長度要保持相等并且每層走線都需要等長。?

(2)需要等長的信號走相同走線層可以保持過孔的時延一致,從而消除過孔時延不一致帶來的影響。

(3)無法保證同組同層時,請把過孔的長度也考慮進(jìn)去。其實(shí)任何時候把這個選項(xiàng)勾上都是沒有問題的,前提是設(shè)置好層疊結(jié)構(gòu),這個Z軸的延時長度才會準(zhǔn)確。雖然說相同長度的過孔和走線延時上會有差別,勾上這個選項(xiàng)等長誤差也并不一定準(zhǔn)確,但是完全不勾誤差會更大。

-

pcb

+關(guān)注

關(guān)注

4365文章

23481瀏覽量

409259 -

微帶線

+關(guān)注

關(guān)注

2文章

82瀏覽量

16719 -

電磁場

+關(guān)注

關(guān)注

0文章

800瀏覽量

48127

原文標(biāo)題:繞等長的時候過孔的長度要算進(jìn)去嗎

文章出處:【微信號:PCBTech,微信公眾號:EDA設(shè)計(jì)智匯館】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

一篇很有用的文章--淺談微帶線的損耗

特性阻抗公式 (含微帶線,帶狀線的計(jì)算公式)

利用ADS設(shè)計(jì)帶狀線低通濾波器

微帶線和帶狀線設(shè)計(jì)

如何區(qū)分傳輸線權(quán)衡的微帶線和帶狀線?

PCB的受控阻抗走線設(shè)計(jì)和微帶線與帶狀線的實(shí)現(xiàn)說明

微帶線中的介電損耗有多低?

從實(shí)際測試板進(jìn)行的高速PCB板微帶線和帶狀線損耗控制研究

什么是微帶線和帶狀線

到底微帶線和帶狀線延時上的差別有多大?

到底微帶線和帶狀線延時上的差別有多大?

評論