CAN總線邊沿時間會影響采樣正確性,而采樣錯誤會造成錯誤幀不斷出現,影響CAN總線通信。那么CAN總線邊沿時間標準是什么?邊沿時間如何測量呢?

一、CAN測試邊沿時間意義

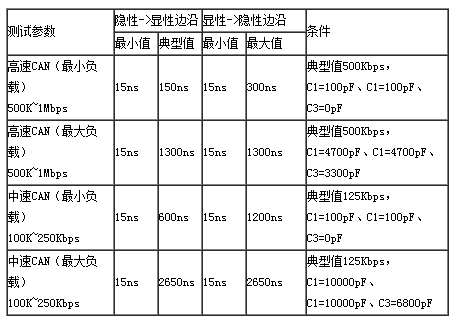

目前在國內汽車電子行業沒有明確的標準,也就造成汽車零配件質量良莠不齊,零配件整裝到汽車上將會造成CAN總線通信異常,給汽車駕駛帶來安全隱患。如下是GMW3122信號邊沿標準對CAN總線邊沿的規范要求。

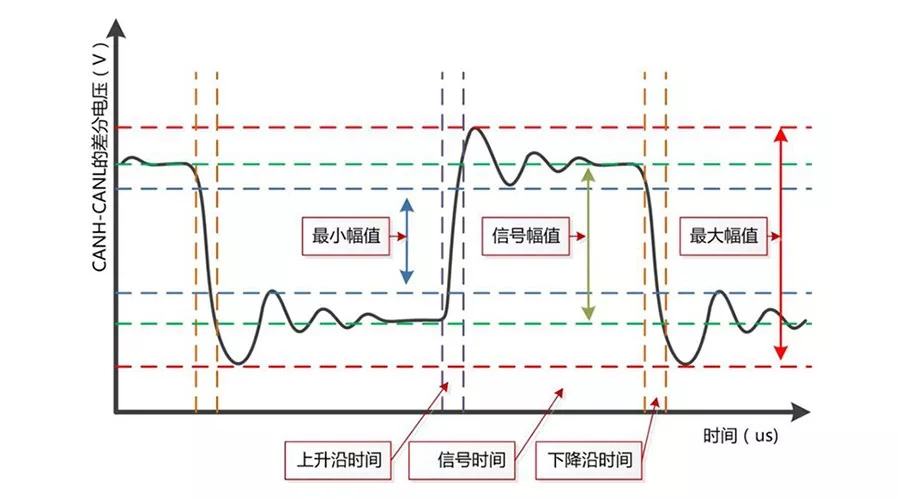

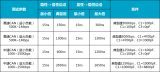

表中根據需求不同,波特率不同分為高速CAN 和低速CAN。測試的是信號邊沿時間,邊沿時間是指隱性電平到顯性電平時間和顯性電平到隱性電平變化的總時間。隱性電平(邏輯值0)到顯性電平(邏輯值1)時間為上升沿,顯性電平到隱性電平為下降沿。

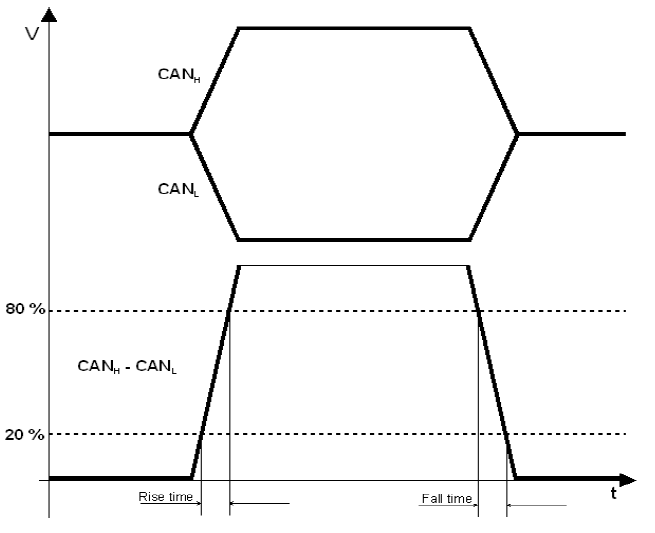

邊沿時間分為上升沿時間、下降沿時間。下降沿時間是按照電壓(20%~80%電壓區間,有些按照10%~90%電壓區間測量邊沿時間,文中以20%~80%電壓區間測量邊沿時間)。表中給出時間范圍,如果超出規定時間,會造成波形位寬增加,采樣點取值不準確,波特率異常,出現大量錯誤幀,一直重發數據幀也會造成CAN總線通信癱瘓。

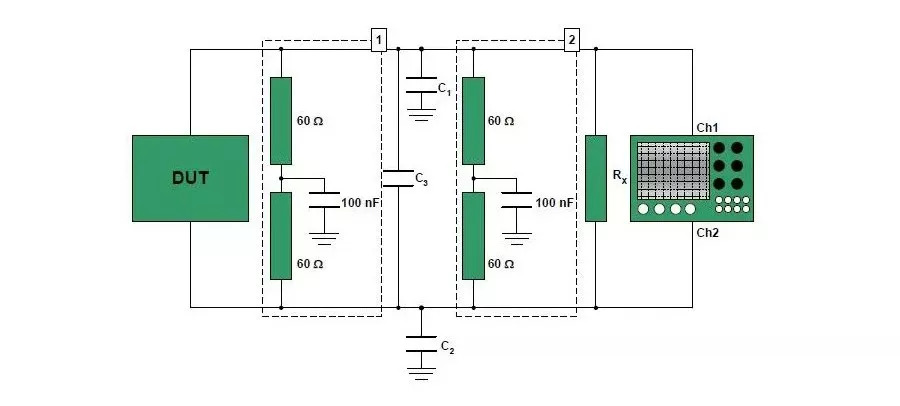

由于現場總線過長,導致總線上掛載電容增加,從而導致線路阻抗增加。在邊沿時間測試需要考慮電阻與電容匹配。模擬測試線路短,需要人為添加電容來模擬現場存在實際情況。在上表中典型值是根據現場電容、電阻得出的常用值。

二、CAN邊沿時間測試步驟

示波器測試CAN波形

用示波器采集CAN總線波形,設置幅值光標為20%~80%,記錄上升沿的時間、下降沿時間。

記錄多次數據,確認每次求得上升沿、下降沿時間都在標準范圍內。

CAN測試問題

只使用示波器測量CAN邊沿時間,需要人為操作記錄多次時間。整車CAN總線擁有多個零部件,測試CAN邊沿時間需要花費大量時間以及人力,而這還只是整車CAN一致性測試的其中一項,完成全部測試要求,需要一個人測試三天。隨著效率要求越來越高,整車廠更希望將時間花費在研發汽車應用新技術。

三、CANDT

基于汽車行業對CAN總線測試手段繁雜,致遠電子自主研發的CANDT一致性測試系統,可構建CAN總線安全保障體系,自動化完成CAN總線物理層、鏈路層及應用層自動化測試。保證整車安全四步曲如下:

步驟一:CAN一致性自動化測試

通過將汽車或節點零部件接入CAN一致性測試系統,可自動化完成CAN總線物理層、鏈路層等自動化測試,覆蓋主流主機廠標準要求,保障整車CAN總線安全穩定。

步驟二:詳細測試報表導出

單節點測試完成之后,可自動化到處詳細CAN一致性測試報表,其包含測試標準引用,評判依據,判斷結果等數據,準確判斷節點工作情況,一目了然,可作為主機廠準入依據。

步驟三:CAN總線故障定位及排查解決

新能源汽車主機廠和零部件企業在CANDT一致性測試后,對于測試報告中顯示測試不通過的問題,可以用CANScope進行故障定位和排查,加快CAN總線穩定的研發速度。

測試結果:保障整車CAN網絡安全

新能源汽車CAN節點在通過一致性測試后,質量高度一致,避免了CAN節點良莠不齊帶來的安全隱患問題,從而保證了整車CAN網絡的安全統一。

-

CAN

+關注

關注

57文章

2856瀏覽量

466587 -

電平

+關注

關注

5文章

367瀏覽量

40370 -

總線通信

+關注

關注

0文章

59瀏覽量

11976

原文標題:CAN一致性測試——邊沿時間

文章出處:【微信號:ZLG_zhiyuan,微信公眾號:ZLG致遠電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

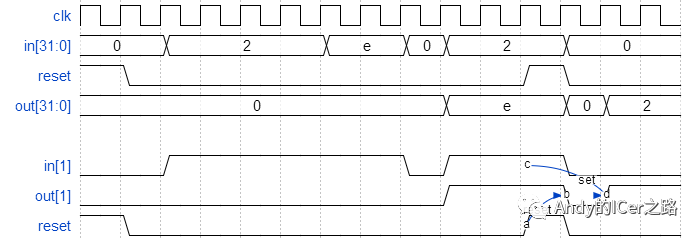

如何同步采集信號及邊沿計數方面問題

CAN總線冷知識-邊沿臺階是怎么來的?

CAN信號不穩定?“罪魁禍首”邊沿臺階不可忽視

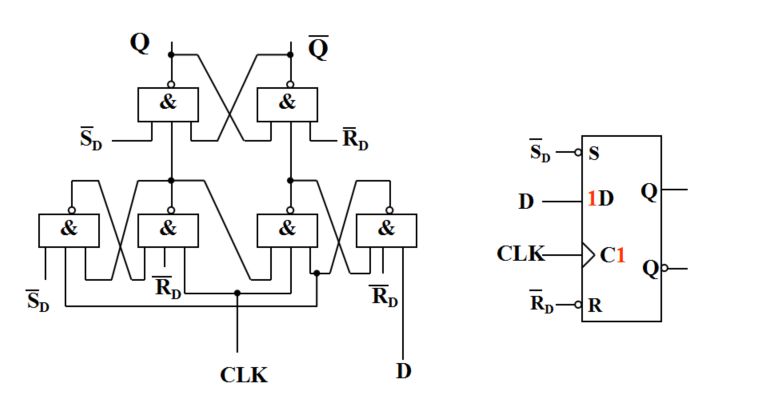

CMOS觸發器在CP邊沿的工作特性研究

邊沿觸發SR觸發器

什么是邊沿觸發器_邊沿D觸發器介紹

基于CAN節點的信號邊沿參數測量方案

CAN差分波形的邊沿如此緩慢怎么辦?

CAN總線邊沿時間標準是什么?邊沿時間如何測量呢?

CAN總線邊沿時間標準是什么?邊沿時間如何測量呢?

評論