本文將從Verilog和邊沿檢測的基本概念入手,介紹Verilog邊沿檢測的原理和應用代碼示例。

一、什么是Verilog邊沿檢測?

Verilog邊沿檢測是數字電路設計中常用的方法之一。 它是一種檢測輸入信號邊沿變化的技術,用于實現(xiàn)時序控制、數據采集和數字信號處理等功能。

Verilog邊沿檢測可以通過posedge、negedge和edge等敏感表達式來實現(xiàn),其基本原理是通過觸發(fā)器檢測輸入信號的狀態(tài)變化,并觸發(fā)相應的邏輯操作。

二、Verilog邊沿檢測的實現(xiàn)原理

Verilog邊沿檢測的實現(xiàn)原理可以通過以下幾個步驟來說明:

1、定義輸入信號和輸出信號

在開始 Verilog 邊沿檢測的實現(xiàn)之前,首先需要定義輸入信號和輸出信號。 通常情況下,輸入信號是從外部輸入的數字信號,而輸出信號是根據輸入信號經過模塊處理后所得到的數字信號。

2、設計邊沿檢測模塊

定義好輸入信號和輸出信號后,接下來就需要設計邊沿檢測模塊。 這個模塊通常由一個或多個“always”塊組成。 這些語句塊會根據輸入信號的狀態(tài)變化以及敏感表達式的定義來執(zhí)行相應的操作,從而實現(xiàn)邊沿檢測。

3、選擇敏感表達式類型

在設計邊沿檢測模塊時,需要選擇使用哪種敏感表達式類型。 Verilog中提供了多種邊沿檢測的實現(xiàn)方式,如posedge、negedge等。 其中,posedge表示上升沿檢測,negedge表示下降沿檢測。 用戶可以根據實際需求選擇適合的邊沿檢測方式。

三、Verilog邊沿檢測的代碼實現(xiàn)

下面是一個基于posedge敏感表達式的Verilog邊沿檢測實現(xiàn)的代碼示例。 該代碼實現(xiàn)了一個簡單的計數器,用于在信號上升沿時自增并輸出計數值。

module edge_detect(

input clk,

input reset,

input signal,

output reg [31:0] period,

output reg [31:0] duty_cycle

);

reg signal_delay;

wire signal_pos_edge;

wire signal_neg_edge;

reg [31:0] count;

reg [31:0] last_count;

reg [31:0] high_time;

reg [31:0] low_time;

reg [1:0] state;

//上升沿 上一個周期信號為低,當前周期信號為高,即上升

assign signal_pos_edge = (~signal_delay )&signal;

//下降沿 上一個周期信號為高,當前周期信號為低,即下降

assign signal_neg_edge = signal_delay&(~signal);

always @(posedge clk or posedge reset) begin

if (reset) begin

signal_delay <= 'b0;

count <= 0;

last_count <= 0;

high_time <= 0;

low_time <= 0;

state <= 2'b00;

period <= 0;

duty_cycle <= 0;

end else begin

signal_delay <= signal;

count <= count + 1;

case (state)

default: begin // wait for rising edge

if (signal) begin

last_count <= count - 1;

state <= 2'b01;

end

end

2'b01: begin // wait for falling edge

if (!signal) begin

high_time <= count - last_count - 1;

state <= 2'b10;

end

end

2'b10: begin // wait for rising edge

if (signal) begin

low_time <= count - last_count - high_time - 1;

period <= (low_time > 'b0)&&(high_time > 'b0) ? high_time + low_time : 'b0;

duty_cycle <= (period > 'b0) ? low_time * 100 / period : 'b0 ;

last_count <= count - 1;

state <= 2'b01;

end

end

endcase

end

end

endmodule

在這個代碼示例中,我們定義了一個邊沿檢測模塊,包括輸入信號clk、reset和signal,以及輸出信號period和duty_cycle。

注意:代碼中的除法,在正式工程中不能這么用哦,需要自己實現(xiàn)一個除法器才行。

這個模塊的設計原理是:在輸入信號上升沿時開始計時,直到下降沿出現(xiàn),然后停止計時并計算周期和占空比。

三、Verilog邊沿檢測的應用實例

我們可以使用上述代碼示例來實現(xiàn)一個簡單的時序分析電路。 下面是一個測試應用實例,該實例使用上述邊沿檢測模塊來計算輸入信號的周期和占空比。

module testbench;

reg clk;

reg reset;

reg signal;

wire [31:0] period;

wire [31:0] duty_cycle;

edge_detect uut(

.clk(clk),

.reset(reset),

.signal(signal),

.period(period),

.duty_cycle(duty_cycle)

);

initial begin

clk = 0;

reset = 1;

signal = 0;

#10 reset = 0;

#100 signal = 1;

#100 signal = 0;

#100 signal = 1;

#100 signal = 0;

#100 signal = 1;

#100 signal = 0;

#100 signal = 1;

#100 signal = 0;

#100 $finish;

end

always #5 clk = ~clk;

endmodule

在這個代碼示例中,我們定義了一個testbench,包括輸入信號clk、reset和signal,以及邊沿檢測模塊uut,編寫了測試邏輯,可以測試該模塊的性能和正確性。

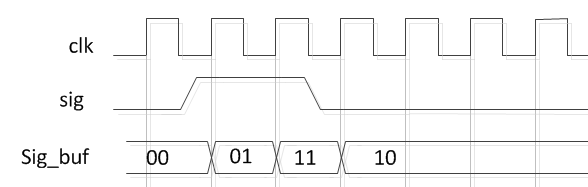

仿真結果:

四、總結

Verilog邊沿檢測是一種常用的數字信號處理方法,可用于時序分析、數據采集和數字信號處理等領域。 本文介紹了Verilog邊沿檢測的基本原理和代碼實現(xiàn),并給出了一個簡單的例子來說明其應用。

-

Verilog

+關注

關注

28文章

1365瀏覽量

111716 -

數字信號

+關注

關注

2文章

988瀏覽量

48113 -

時序

+關注

關注

5文章

397瀏覽量

37751 -

輸出信號

+關注

關注

0文章

302瀏覽量

12126 -

邊沿檢測

+關注

關注

0文章

6瀏覽量

7884

發(fā)布評論請先 登錄

頻率設計:頻率計基本原理

串口通信基本原理是什么

關于FPGA進行外部邊沿檢測,檢測不準確問題?

PIC16F15323單片機的基本原理是什么

PIC16F15323單片機的基本原理

檢測油中氣體的基本原理

聲發(fā)射檢測的基本原理

聲發(fā)射檢測的基本原理

用移位寄存器實現(xiàn)邊沿檢測的技巧

Verilog系統(tǒng)函數和邊沿檢測

Verilog實現(xiàn)邊沿檢測的原理

Verilog邊沿檢測的基本原理和代碼實現(xiàn)

Verilog邊沿檢測的基本原理和代碼實現(xiàn)

評論