CMOS級(jí)邏輯電路實(shí)現(xiàn)綜述

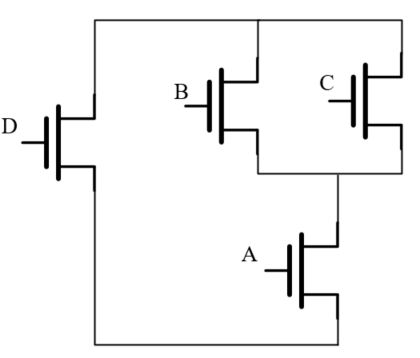

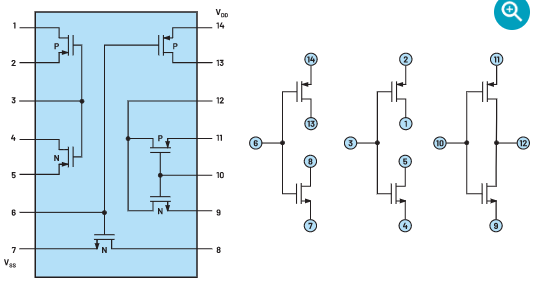

CMOS邏輯電路,分兩部分,上拉部分,下拉部分。上拉部分由PMOS管電路構(gòu)成,下拉部分由NMOS管電路組成,如下。上下拉,形成互補(bǔ)。

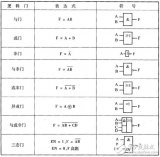

由前面的基礎(chǔ)可知,CMOS只能實(shí)現(xiàn)基本邏輯的非,比如或邏輯,與邏輯,如果不加反相器,CMOS只能實(shí)現(xiàn)或非,與非邏輯。原因就是上拉邏輯只能用PMOS實(shí)現(xiàn),下拉邏輯只能由NMOS實(shí)現(xiàn),而PMOS的導(dǎo)通需要輸入信號(hào)為0,NMOS導(dǎo)通需要輸入信號(hào)為1。

既然如此,我們?cè)谟肅MOS實(shí)現(xiàn)邏輯電路時(shí),一般可以照如下順序去做:

1. 可以先將其整體先加上一個(gè)非,作相應(yīng)的邏輯轉(zhuǎn)化。

2. 上拉邏輯中各個(gè)PMOS,與操作為并聯(lián),或操作為串聯(lián)。

3. 下拉邏輯中各個(gè)NMOS,與操作為串聯(lián),或操作為并聯(lián)。

比如我們想從CMOS層去實(shí)現(xiàn)邏輯 OUT = D+A*(B+C) (減號(hào)“-”表示取反(非)操作,“+”表示或,*表示與)。

設(shè)計(jì)過(guò)程如下:

1. OUT = - ( -(D+A*(B+C)) )

2. OUT1 =-(D+A*(B+C))

3. OUT = -OUT1

對(duì)于OUT1 = -(D+A*(B+C)),正好是邏輯整體上帶了個(gè)非。

故對(duì)于上拉邏輯:

或操作為串聯(lián),從而輸入B,C接到的PMOS之間為串聯(lián)。

與操作為并聯(lián),故輸入A接到的PMOS跟B,C或邏輯之間為并聯(lián)。

或操作為串聯(lián),故D與A*(B+C)的PMOS邏輯為串聯(lián)。

對(duì)于下拉邏輯與上拉邏輯正好相反:

或操作為并聯(lián),從而輸入B,C接到的NMOS之間為并聯(lián)。

與操作為串聯(lián),故輸入A接到的NMOS跟B,C或邏輯之間為串聯(lián)。

或操作為并聯(lián),故D與A*(B+C)的NMOS邏輯為并聯(lián)。

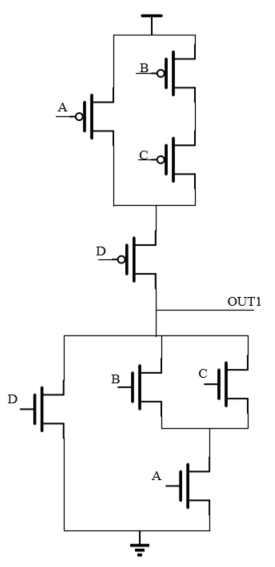

從而得到OUT1 =-(D+A*(B+C)) 的CMOS實(shí)現(xiàn)如下:

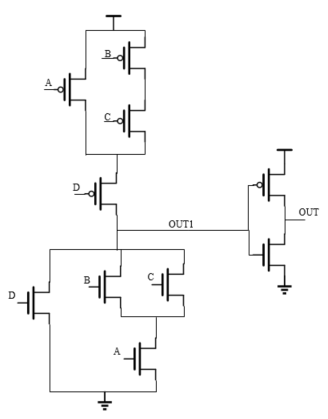

OUT = -OUT1,故得最終答案如下:

當(dāng)然,在MOS管級(jí)別還可以做一些優(yōu)化,比如MOS管級(jí)別的邏輯優(yōu)化,MOS管柵源共用,晶體管尺寸調(diào)整,重新安排各個(gè)輸入的上下順序等等,都可以在MOS管級(jí)別使得電路的時(shí)序與面積功耗等得到優(yōu)化,但這不是我們的重點(diǎn),一般對(duì)于全定制IC設(shè)計(jì)會(huì)從MOS管級(jí)開始考慮電路的實(shí)現(xiàn)。這里我們只是對(duì)其做一個(gè)了解。

我們今后的重點(diǎn)將會(huì)注重于門級(jí)以上的電路實(shí)現(xiàn)與優(yōu)化,特別是到了Verilog描述,主要著重于數(shù)據(jù)流級(jí),行為級(jí)描述。

-

CMOS

+關(guān)注

關(guān)注

58文章

5982瀏覽量

238031 -

邏輯電路

+關(guān)注

關(guān)注

13文章

502瀏覽量

43161

原文標(biāo)題:CMOS級(jí)邏輯電路實(shí)現(xiàn)綜述

文章出處:【微信號(hào):LF-FPGA,微信公眾號(hào):小魚FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

邏輯電路芯片-組合邏輯電路芯片-時(shí)序邏輯電路芯片

邏輯電路的糾錯(cuò)技術(shù)是如何實(shí)現(xiàn)的?

為什么FPGA可以用來(lái)實(shí)現(xiàn)組合邏輯電路和時(shí)序邏輯電路呢?

數(shù)字系統(tǒng)的基本算法與邏輯電路實(shí)現(xiàn)

CMOS邏輯電路高級(jí)技術(shù)與時(shí)序電路

各種邏輯電路簡(jiǎn)介

CMOS邏輯電路,CMOS邏輯電路是什么意思

邏輯電路解析和邏輯電路的分類

組合邏輯電路實(shí)驗(yàn)原理

組合邏輯電路和時(shí)序邏輯電路比較_組合邏輯電路和時(shí)序邏輯電路有什么區(qū)別

CMOS邏輯電路、傳輸門XOR

CMOS級(jí)邏輯電路實(shí)現(xiàn)綜述

CMOS級(jí)邏輯電路實(shí)現(xiàn)綜述

評(píng)論