從網(wǎng)絡(luò)的核心模塊到邊緣設(shè)備,都在經(jīng)歷著巨大的變革。無(wú)線市場(chǎng)與其數(shù)千萬(wàn)的"永遠(yuǎn)在線"連接、下一代回程通信的巨大傳輸壓力,以及各種為使用現(xiàn)有有線通信基礎(chǔ)設(shè)施的消費(fèi)者提供寬帶通信的舉措,都是推動(dòng)網(wǎng)絡(luò)發(fā)展的關(guān)鍵因素。因此,網(wǎng)絡(luò)核心朝著100及400Gbps的數(shù)據(jù)通道發(fā)展;網(wǎng)絡(luò)中心區(qū)域也從10Gbps升級(jí)為100Gbps,用以支持不斷擴(kuò)展的各種網(wǎng)絡(luò)接入標(biāo)準(zhǔn)、協(xié)議和接口。此外,為支持日益增大的用戶(hù)流量需求并降低總體傳輸延遲,接入網(wǎng)絡(luò)也正在從之前的并行接口升級(jí)到現(xiàn)代高速串行接口。

由于網(wǎng)絡(luò)運(yùn)營(yíng)商們期待以低成本提升網(wǎng)絡(luò)容量,并同時(shí)保持總體覆蓋率,因此他們往往不可能徹底更換目前已經(jīng)安裝好的硬件設(shè)施。產(chǎn)品上市時(shí)間、整體的升級(jí)費(fèi)用和現(xiàn)有軟件支持上的投入,僅僅是幾個(gè)必須考慮的問(wèn)題。當(dāng)設(shè)備升級(jí)時(shí),必須提供必要的 "翻新" 以延長(zhǎng)使用期限,同時(shí)加入符合預(yù)期網(wǎng)絡(luò)需求的功能特性,許多NEP(網(wǎng)絡(luò)設(shè)備供應(yīng)商)發(fā)現(xiàn)具有收發(fā)器功能的中端FPGA是一種十分有效的解決方案。

中端FPGA是相對(duì)較新的一類(lèi)FPGA.這些成本和功耗優(yōu)化的器件提供了傳統(tǒng)現(xiàn)場(chǎng)可編程門(mén)陣列的所有特性,并結(jié)合了僅高端器件才具有的各種先進(jìn)功能。例如,這些可編程器件提供了具有成本效益且功耗優(yōu)化了的串行接口(SERDES),這使他們能夠彌補(bǔ)現(xiàn)有的和下一代通信解決方案之間的差距。帶串行接口的中端FPGA也可以配置為支持各種數(shù)據(jù)傳輸速率和接口標(biāo)準(zhǔn),無(wú)論是否是行業(yè)標(biāo)準(zhǔn)的還是專(zhuān)用的。并且,由于同一種規(guī)格大小的器件不可能符合所有的需求,因此這些器件的SERDES通道數(shù)量隨不同型號(hào)而變化,從而使得設(shè)計(jì)工程師能夠優(yōu)化其可編程解決方案,以滿(mǎn)足特定的成本和功耗目標(biāo)。

中端FPGA中串行接口的可配置功能是十分關(guān)鍵的,它賦予了這些器件獨(dú)特的競(jìng)爭(zhēng)優(yōu)勢(shì)。雖然過(guò)去很多網(wǎng)絡(luò)設(shè)備供應(yīng)商可能會(huì)考慮采用其"自行開(kāi)發(fā)"的接口標(biāo)準(zhǔn),尤其是在整個(gè)機(jī)架的設(shè)備已經(jīng)由同一制造商開(kāi)發(fā)的情況下,但當(dāng)今市場(chǎng)擁有多樣化的選擇,并且供應(yīng)商設(shè)備之間的互操作性已成為必然。大型的系統(tǒng)供應(yīng)商仍將繼續(xù)提供完整的解決方案,而其他制造商則尋求能夠在行業(yè)標(biāo)準(zhǔn)機(jī)箱內(nèi)工作的差異化解決方案,或者獨(dú)立的"薄型設(shè)備".實(shí)現(xiàn)行業(yè)標(biāo)準(zhǔn)串行接口不僅可以減少系統(tǒng)設(shè)計(jì)時(shí)間,還能夠改善不同供應(yīng)商之間的互操作性,提高整個(gè)系統(tǒng)的可靠性,并拓寬供應(yīng)商設(shè)備的接納范圍。

在實(shí)現(xiàn)串行接口時(shí),一個(gè)重要的特性是能夠創(chuàng)建可擴(kuò)展的數(shù)據(jù)鏈路,以滿(mǎn)足傳輸帶寬的要求。為使帶寬與所支持的傳輸協(xié)議相匹配,中端FPGA加入了硬化的PMA和PCS邏輯模塊,它們?cè)诠δ苌峡梢园疃ㄔ谝黄稹0疃C(jī)制實(shí)現(xiàn)了多個(gè)收發(fā)器通道來(lái)支持一個(gè)協(xié)議,而其余的串行接口仍可以獨(dú)立地支持其他協(xié)議,或者被禁用,從而進(jìn)一步節(jié)省整個(gè)系統(tǒng)的功耗。雖然收發(fā)器通過(guò)加入PMA和PCS功能模塊提供物理層接口,但還需要在更高的"客戶(hù)"層提供大量額外的邏輯,以創(chuàng)建一個(gè)完整的行業(yè)標(biāo)準(zhǔn)解決方案。雖然ASSP可以提供帶有硬化串行接口的特定接口解決方案,但是它們?nèi)狈Ρ匾撵`活性,無(wú)法支持網(wǎng)絡(luò)接入市場(chǎng)中用到的各種接口。

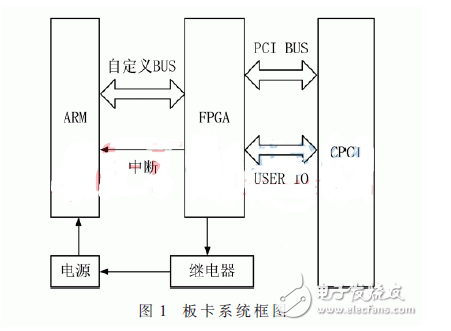

此外,基于SERDES的高端FPGA也可以被設(shè)計(jì)為在其結(jié)構(gòu)內(nèi)包含大量的串行傳輸邏輯,只是代價(jià)高昂:額外的設(shè)計(jì)和驗(yàn)證時(shí)間、更多的功耗和尺寸大小。此外,中端FPGA還為電路板級(jí)和系統(tǒng)級(jí)設(shè)計(jì)人員提供了另一個(gè)關(guān)鍵優(yōu)勢(shì)。通過(guò)為FPGA的軟邏輯陣列增加一定數(shù)量收發(fā)器(根據(jù)不同的器件),以及硬化的行業(yè)標(biāo)準(zhǔn)傳輸協(xié)議邏輯,這些器件提供了一個(gè)靈活、低成本和小尺寸的通信解決方案。如圖1所示,通過(guò)選擇適當(dāng)?shù)腇PGA,可以很容易地實(shí)現(xiàn)不同的傳輸協(xié)議解決方案。

圖1:具有收發(fā)器功能的中端FPGA.

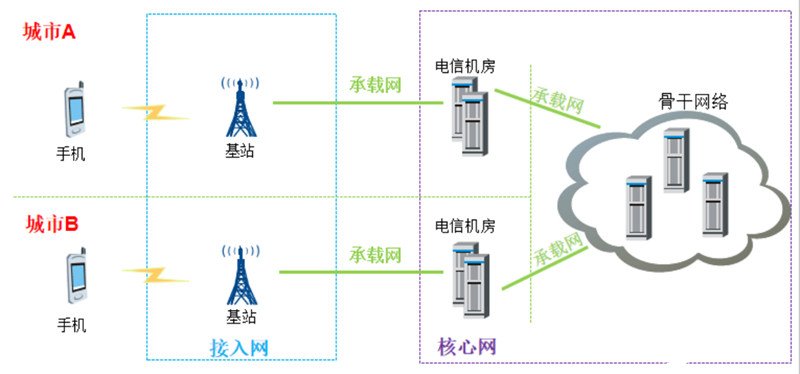

接入網(wǎng)絡(luò)由來(lái)自不同網(wǎng)絡(luò)運(yùn)營(yíng)商提供的基礎(chǔ)設(shè)備構(gòu)成。并且,由于預(yù)計(jì)將會(huì)有大量的陳舊設(shè)備仍將在之后幾年繼續(xù)使用,越來(lái)越多的運(yùn)營(yíng)商轉(zhuǎn)而使用一種全分組(all-packet)網(wǎng)絡(luò)。隨著向全分組網(wǎng)絡(luò)發(fā)展,一些行業(yè)標(biāo)準(zhǔn)技術(shù)正在迅速成為控制平臺(tái)和數(shù)據(jù)傳輸互連的主導(dǎo)。以太網(wǎng)以其悠久的歷史、使用的廣泛性以及本地IP數(shù)據(jù)包支持,將主導(dǎo)下一代網(wǎng)絡(luò)。而PCI-Express憑借廣泛用于計(jì)算、服務(wù)器和消費(fèi)電子市場(chǎng),也正在大量用于器件級(jí)和背板互連,同時(shí)還被廣泛部署用來(lái)取代并行PCI總線。串行無(wú)線IO標(biāo)準(zhǔn)則被用于各種無(wú)線、DSP和其它嵌入式計(jì)算解決方案。如上所述,許多中端FPGA支持這些關(guān)鍵標(biāo)準(zhǔn),從而為設(shè)備制造商提供了一系列豐富的硬化解決方案。除了成本和功耗上的優(yōu)勢(shì),這類(lèi)器件還無(wú)需實(shí)現(xiàn)和驗(yàn)證通信協(xié)議,這使得設(shè)計(jì)人員能夠?qū)W⒂谠贔PGA結(jié)構(gòu)內(nèi)實(shí)現(xiàn)自己的差異化解決方案和系統(tǒng)升級(jí)功能。

升級(jí)為全分組網(wǎng)絡(luò)時(shí)的一個(gè)重要元素是能夠?qū)⒕W(wǎng)絡(luò)最邊緣處具最低數(shù)據(jù)帶寬需求的數(shù)據(jù)接口和網(wǎng)絡(luò)中心區(qū)域及核心區(qū)段更高數(shù)據(jù)傳輸速率的接口匯聚在一起。邊緣路由器、接入交換機(jī)和其他網(wǎng)絡(luò)匯聚設(shè)備都同時(shí)支持低和高帶寬數(shù)據(jù)速率。為滿(mǎn)足數(shù)據(jù)匯聚的要求,中端FPGA不僅為下一代高速串行接口提供了一種經(jīng)濟(jì)的解決方案,還通過(guò)其增強(qiáng)的通用I/O(GPIO)功能支持傳統(tǒng)的串行接口。利用GPIO來(lái)支持低端串行線速率,即1.25Gbps或更低,使得較昂貴的集成收發(fā)器通道可用于更高的串行線路速率。為支持串行接口,必須有一些時(shí)鐘和數(shù)據(jù)恢復(fù)(CDR)邏輯,這是中端FPGA的另一個(gè)特點(diǎn)。圖2提供了一個(gè)典型的CDR電路模塊圖。

圖2:典型CDR電路模塊圖。

通過(guò)將硬化的時(shí)鐘和數(shù)據(jù)恢復(fù)(CDR)邏輯合并到I/O結(jié)構(gòu)中,再加上可訪問(wèn)選擇硬化傳輸協(xié)議內(nèi)核的PCS接口的結(jié)構(gòu),中端FPGA為各種不同的匯聚設(shè)備接口提供了串行線速率支持。

對(duì)設(shè)計(jì)人員而言,應(yīng)用層邏輯是在FPGA中實(shí)現(xiàn)其解決方案時(shí)需要考慮的另一個(gè)因素。大多數(shù)傳輸協(xié)議都必須支持多種數(shù)據(jù)類(lèi)型,每種都有其自己的傳輸模式、服務(wù)質(zhì)量標(biāo)準(zhǔn)和控制平臺(tái)要求。因此,硬化邏輯必須支持各種客戶(hù)層協(xié)議語(yǔ)義。為提供最符合成本效益的和完整的解決方案,中端FPGA以軟邏輯模塊的形式提供這些不同的邏輯層接口。這些軟邏輯模塊為底層的傳輸協(xié)議模塊提供了無(wú)縫接口,因?yàn)樗鼈兪钦麄€(gè)協(xié)議棧的一部分,符合各自的行業(yè)標(biāo)準(zhǔn)。

另一方面,有時(shí)設(shè)計(jì)人員會(huì)認(rèn)為專(zhuān)用的解決方案會(huì)更加適合,利用中端FPGA豐富的可編程邏輯功能,他們能夠自由地設(shè)計(jì)最適合其要求的邏輯功能。但無(wú)論軟邏輯層是專(zhuān)有的還是作為接口的一部分,建立一個(gè)完整的協(xié)議棧可能會(huì)很復(fù)雜,必須有一種簡(jiǎn)單的設(shè)計(jì)方法來(lái)幫助實(shí)現(xiàn)最終的解決方案。許多當(dāng)今的中端FPGA可以使用圖形化用戶(hù)界面設(shè)計(jì)環(huán)境進(jìn)行開(kāi)發(fā),這使得設(shè)計(jì)人員能夠很容易地實(shí)現(xiàn)硬化邏輯的實(shí)例,并很快將它們與自己的邏輯塊拼接在一起。設(shè)計(jì)人員可以在整個(gè)設(shè)計(jì)和實(shí)現(xiàn)階段都使用這套軟件工具,確保他們的串行接口能夠正確地互連到自己的邏輯塊,并且實(shí)例化的串行接口將能一次性運(yùn)行成功。

本文小結(jié)

當(dāng)前的接入網(wǎng)絡(luò)由多樣化的接口和邏輯處理單元組成。下一代網(wǎng)絡(luò)需要處理和傳輸?shù)臄?shù)據(jù)與今天運(yùn)營(yíng)商所看到的數(shù)字相比將呈現(xiàn)幾何數(shù)量級(jí)的增長(zhǎng)。并且,當(dāng)一個(gè)同構(gòu)網(wǎng)絡(luò)架構(gòu)的傳輸壓力越來(lái)越大,目前已安裝的大多數(shù)設(shè)備根本就不能處理。因此,陳舊的設(shè)備與其較慢的器件接口必須和未來(lái)的高速接口和功能銜接起來(lái)。與此同時(shí),還必須堅(jiān)持嚴(yán)格的功耗預(yù)算、降低成本目標(biāo)并縮短開(kāi)發(fā)周期。

正如圖3所示的LatticeECP4中端FPGA,它擁有可配置的收發(fā)器、硬化的行業(yè)標(biāo)準(zhǔn)傳輸協(xié)議塊、豐富的可編程結(jié)構(gòu)功能,以及圖形化用戶(hù)界面軟件設(shè)計(jì)環(huán)境,為設(shè)計(jì)人員提供了開(kāi)發(fā)下一代設(shè)備所需的功能來(lái)滿(mǎn)足功耗和成本需求,并且延長(zhǎng)了其原有設(shè)備的使用壽命。

圖3:萊迪思中端FPGA硬化的協(xié)議邏輯。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613996 -

服務(wù)器

+關(guān)注

關(guān)注

13文章

9682瀏覽量

87269 -

總線

+關(guān)注

關(guān)注

10文章

2947瀏覽量

89333

發(fā)布評(píng)論請(qǐng)先 登錄

基于FPGA的AFDX端系統(tǒng)協(xié)議芯片的設(shè)計(jì)與實(shí)現(xiàn)

基于FPGA的以太網(wǎng)系統(tǒng)軟硬件實(shí)現(xiàn)方案

基于FPGA的以太網(wǎng)系統(tǒng)軟硬件實(shí)現(xiàn)方案

關(guān)于基于FPGA的視頻無(wú)線傳輸及通信協(xié)議方面的問(wèn)題,謝謝

基于FPGA和W5500的以太網(wǎng)傳輸系統(tǒng)實(shí)現(xiàn)

基于MIPI協(xié)議的FPGA實(shí)現(xiàn)視頻傳輸技術(shù)

基于FPGA單芯片實(shí)現(xiàn)ARM系統(tǒng)設(shè)計(jì)解決方案

FPGA實(shí)現(xiàn)ARM系統(tǒng)處理的解決方案解析

FPGA上實(shí)現(xiàn)網(wǎng)絡(luò)通信用的協(xié)議

如何使用AT32F437以太網(wǎng)通信接口實(shí)現(xiàn)在應(yīng)用中編程(IAP)的解決方案

(Xilinx)FPGA中LVDS差分高速傳輸的實(shí)現(xiàn)

用FPGA來(lái)實(shí)現(xiàn)DSP解決方案的理由

基于FPGA的CPCI系統(tǒng)設(shè)計(jì)和實(shí)現(xiàn)方案

中興通訊端到端傳輸解決方案實(shí)現(xiàn)承載業(yè)務(wù)“光速直達(dá)”

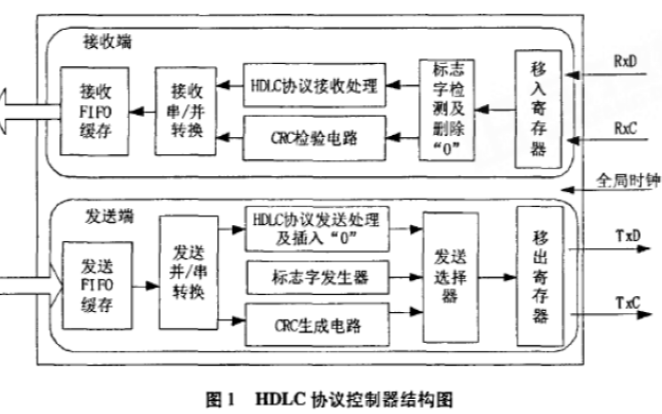

如何使用FPGA實(shí)現(xiàn)HDLC協(xié)議控制器

利用中端FPGA實(shí)現(xiàn)實(shí)現(xiàn)不同的傳輸協(xié)議解決方案

利用中端FPGA實(shí)現(xiàn)實(shí)現(xiàn)不同的傳輸協(xié)議解決方案

評(píng)論