現代的圖形采集技術發展迅速,各種基于ISA、PCI等總線的圖形采集卡已能在市場上買到,但是價格比較昂貴,并且處理功能簡單。對于特殊需要不能很好滿足,往往需要加上后續處理部分,這給特殊需要的用戶帶來了不便。采用現場可編程芯片及DSP處理芯片構成的圖像采集系統,可以根據不同的需要進行現場編程,具有通用性好、價格相對便宜等特點。

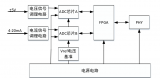

該系統采用PHILIP公司最新推出的視頻A/D芯片7111,將從CCD輸出的PAL制式的全電視信號轉換為數字信號,由FPGA作為采樣控制器將該八位數字信號存入片內RAM中,隨后可根據具體需要由DSP進行預處理,提取有用數據(數據量已很小),然后將所需結果經由ISA總線交給計算機處理,完成接口功能。圖1所示為采集系統方框圖。

1 視頻信號的A/D轉化

本文所研究的圖形對象是靜態的,要求采集512×512的灰度圖像,可采用CCD攝像機進行圖像采集。CCD的輸出為標準PAL制式,因此需要進行A/D轉化。

本系統采用的PHILIP公司的視頻A/D芯片SAA7111具有四路視頻輸入,抗混濾波、梳狀濾波都被集成到芯片內部,帶來了極大的方便。場同步信號VREF、行同步信號HREF、奇偶場信號RES1、像素時鐘信號LLC2都由管腳直接引出,省去了以往的時鐘同步電路的設計,可靠性也有所提高。系統內部鎖相環技術的集成使得可靠性和設計復雜度都有極大的降低。

在7111中有控制字可以直接控制行同步有效時間,因此可以省略行延遲電路。

2 邏輯控制部分

本系統的核心控制部分由一片FPGA芯片實現。由于FPGA芯片具有高速、高可靠性、開發周期短的特點,并且可以根據現場的需要進行編程、可擦寫多次,因而具有極大的方便性。隨著現代工藝的提高,芯片加工的成本有了極大的降低,可靠性也有保證,芯片的大小和功耗都有極大的降低,特別是3.3V的FPGA是現在廠商主推的產品,并且有繼續降低的趨勢。現代高技術的發展使得FPGA應用于電子設計中成為可能和必然趨勢。

基于FPGA技術的采樣控制器要產生眾多的控制信號。當微處理器發出采樣指令時,采樣控制器在此后到來的第一個幀同步信號到來時啟動采樣,并將這幀數據存放在SRAM中,采樣結束后向微處理器發出采樣結束ECO信號。采樣控制器主要實現三個邏輯功能:地址發生器;握手邏輯;RAM寫時序。

(1)地址發生器由計數器及一部分D觸發器和邏輯門組成。主要具有場延遲功能和地址發生功能。由于所采圖像為512×512的正方形(這是由于系統后續處理的需要),7111中的輸出信號為720×625的矩形,因此需要對7111信號進行行延遲和場延遲。

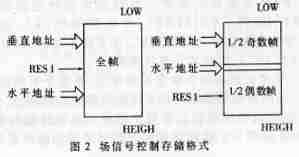

在數字量存入內存時,由于PAL制式的全電視信號為奇、偶場分離,因此可以巧妙利用奇偶信號RES1作為地址線。根據RES1為垂直地址的高位或為地址的最高位可使圖像在內存中的樣子如同一幅圖像或分為上下兩個半場分開的圖像,如圖2所示。

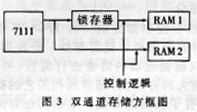

在存儲過程中可采用雙通道技術,即采用兩片內存同時存儲數據,則數據總線由八位升至十六位,可使對RAM寫時序的要求降低一半。當然這需要對7111輸出的數字信號進行數據鎖存,使得兩位數據能夠根據同一控制信號滿足RAM寫時序的要求,如圖3所示。

(2)握手邏輯是采樣控制器和CPU之間的接口,它是由幾個D觸發器及邏輯門實現的,如圖4所示。

當CS1(正脈沖)啟動采樣時,D1保存該信號,在下一個場同步脈沖到來時D2輸出高電平(即VER采樣使能信號)使行延遲計數器開始計數,同時使D1復位,確保不再采第二場。當延遲計數器計數到預置值時產生觸發信號TRI(正脈沖),此時VER為“1”,則D3置位,輸出采樣使能信號SENB(低有效)和地址選通信號ABSW,使后面的電路處在采樣狀態,在場同步脈沖下降沿D3翻轉,整個采樣控制電路處在不采樣狀態。D2要在下一個場同步脈沖的上升沿才變為無效。

當SENB變為無效時(即SENB的上跳沿)觸發D4,使Q有效,向CPU發出中斷申請INT,CPU可用CS2清除這個中斷信號。

(3)RAM寫時序電路可根據芯片對寫操作的具體要求來設計。系統采樣頻率為13.5MHz即74.1ns),采用雙通道技術可使寫時序降低一半,寫頻率為13.5/2=6.75MHz即148.2ns)。SAA7111提供了27MHz的晶振頻率,則四個時鐘周期完成一個寫操作,時序的最小時間單位為18.5ns(半個周期)。根據RAM寫操作的要求,可以設計各種控制信號(WE、HS、VS、CS、SENB)、時鐘信號(CLK)、地址信號和數據信號之間的關系。本系統采用的RAM為IS61C1024,可以滿足系統需要。

采樣控制器擔負著重要的作用,是整個系統的核心;而同步控制邏輯又是采樣控制器的控制核心。同步邏輯起著協調行、場同步信號、地址計數時鐘、SRAM寫信號、采樣數據鎖存信號之間的時間關系、

保證SRAM寫操作時各信號的時序配合。由于采樣頻率高達13.5MHz,因此在硬件實現過程中需要不斷地模擬與仿真,有時要調整整個邏輯電路,計算延遲時間,解決電路中存在的競爭與冒險等等,這些都需要系統的可修改性好,具備可編程的特點。基于FPGA技術的ASIC設計滿足了上述要求,發揮了現場可編程的特點,降低了設計成本,縮短了開發時間,因此系統開發十分方便。

3 DSP處理技術

在此采集系統中,基于DSP的圖像處理技術也得到了應用,特別是在圖像的模式識別問題上充分發揮了DSP的硬件結構和具有特色的編程指令。圖像模式識別的典型算法是卷積運算,也即乘累加,正好發揮DSP軟、硬件的特長。傳統的處理方法是基于計算機的硬件和軟件的,計算機完成一次乘累加運算需要11個機器周期,而DSP完成同樣的運算只需1個機器周期。本系統采用DSP芯片實現圖像的模式識別,提高了處理速度,解決了圖像處理過程中由于圖像識別速度慢而影響整個圖像的處理流程,解決了實際問題,收到了良好的效果。

-

FPGA

+關注

關注

1643文章

21954瀏覽量

613980 -

芯片

+關注

關注

459文章

52145瀏覽量

435976 -

圖像采集

+關注

關注

2文章

306瀏覽量

41564

發布評論請先 登錄

【FPGA新品】正點原子L22開發板來了!采用紫光的Logos系列FPGA,適合工業控制、圖像處理、高速通信等領域!

【高清視頻案例分享】CameraLink接口的PCIe采集卡 ,基于FPGA開發平臺

FPGA圖像處理基礎----實現緩存卷積窗口

基于FPGA的GigE Vision相機圖像采集方案設計

友思特方案 精析“蟬翼”:FPGA圖像處理方案助力鋰電池高速產線檢測新升級

FPGA在圖像處理領域的優勢有哪些?

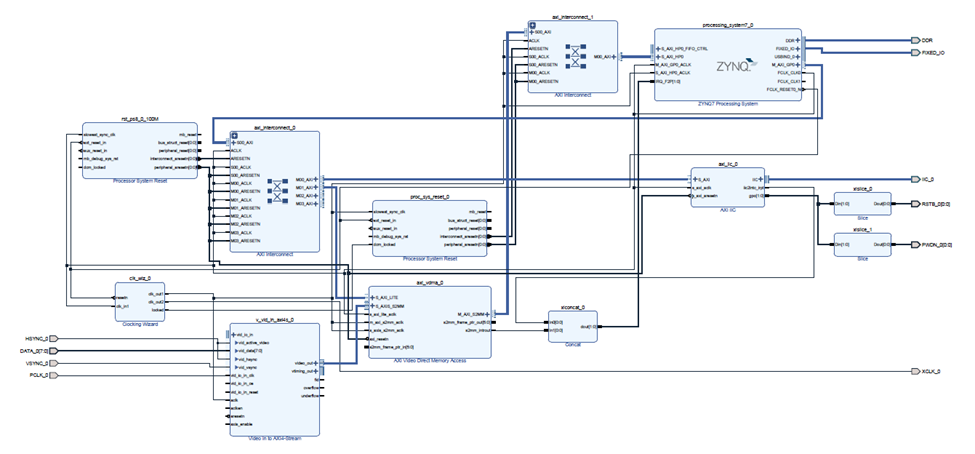

基于VDMA的遠程圖像采集系統參考設計

基于 FPGA 的會議系統設計

基于FPGA的圖像采集與顯示系統設計

圖像采集卡在工業環境中的應用:高分辨率圖像的高速應用

由FPGA芯片實現的高速圖像采集系統的設計

由FPGA芯片實現的高速圖像采集系統的設計

評論