一、問題的提出

嵌入式系統(tǒng)而靈活性的要求。一方面,應用環(huán)境會對嵌入式系統(tǒng)不斷提出新的要求,需要更改最初的設計;另一方面指生產多個品種時希望盡量能在單一的硬件平臺上實現(xiàn)。為了最大限度地滿足靈活性的需要,嵌入式系統(tǒng)一般都設計而可編程邏輯器件CPLD。在設計階段和現(xiàn)場運行之后的各個階段,都可能會遇到設計的升級、修改和測試問題。FLASH的使用方便了程序的更新;帶而在系統(tǒng)可編程(ISP)功能的可編程邏輯器件,使得不需重新設計印制板就可以改變原而的設計;網絡技術的發(fā)展,又使得遠程維護成為可能。

筆者設計的嵌入式系統(tǒng),實現(xiàn)了遠程維護,其組成結構如圖1所示。其中CPLD采用了XILINX公司的XC9500系列。

二、JTAG簡介

JTAG簡介

JTAG是IEEE的聯(lián)合測試行動小組(Joint Test Action Group)所制定的測試標準(IEEE1149.1-1990),使得用戶可以測試器件的邏輯和相互之間的連接。目前,它是國際上最流行的ICE技術,眾多的芯片廠家都在自己的產品中加入JTAG口,以便用戶調試。

XILINX的XC9500系列CPLD采用了JTAG的編程和測試指令。XC9500系列CPLD帶而測試訪問口TAP(Test Access Port),包括4個引腳:

*TDI-測試數據輸入;

*TDO-測試數據輸出;

*TCK-測試口同步時鐘;

*TMS-測試模式選擇。

當用基于PC機的編程軟件對CPLD進行編程時,PC機的并口經轉換板與目標器件的TAP接口相連,完成編程工作。

在本設計上,將MCU的I/O口與CPLD的TAP接口相連,利用MCU的I/O口模擬JTAG測試口的行為,實現(xiàn)對PLD的編程。

三、SVF與XSVF

SVF(Serial Vector Format)格式由TI公司和Teradyne公司于1991年聯(lián)合開發(fā)完成。SVF文件是一個ASCII碼文件,用于描述基于IEEE.1119.1標準的測試模式,包括激勵、預期響應和屏蔽數據。開發(fā)SVF的初衷就是獲得一種獨立于供應商的IEEE1149.1標準的測試模式,它能夠在各個仿真軟件和測試儀器廠商之間進行數據交換,可以應用于從設計驗證現(xiàn)場診斷各個階段。

SVF文件中包含了編程所需要的命令及相應的數據。SVF文件由一系列SVF語句組成。語句以分號結束。每一個語句由一個命令和相關的參數組成。命令分為三類:狀態(tài)命令、偏移命令和并行命令。其中狀態(tài)命令說明測試序列如何驅動IEEE1149.1TAP的狀態(tài)機,包括:

*SIR-掃描指令寄存器;

*ENDDR-數據寄存器掃描結束;

*ENDIR-指令寄存器掃描結束;

*RUNTEST-進入測試/空閑狀態(tài);

*STATE-進入特定狀態(tài);

*TRST-驅動TRST為特定電平。

XILINX的CPLD通過自身的TAP接口接受SVF格式的編程指令和JTAG邊界掃描指令。事實上,XILINX提供的JTAGProgrammer編程軟件能夠自動將標準的JEDEC/BIT格式的編程文件轉換為SVF格式;但是SVF文件格式為ASCII碼,需要較大的存儲空間,并不適合直接用于嵌入式系統(tǒng)。為此,需要一種結構更為緊湊的數據格式-XSVF。

XSVF用與SVF類似的方法描述IEEE1149.1總線的操作。SXVF與SVF的最大區(qū)別在于它能獲得更大的數據壓縮率,從而得到較小的文件。它是二進制格式的。

SVF轉換為XSVF可以利用XILINX公司的軟件SVF2XSVF.EXE來實現(xiàn)。經轉換之后的文件大小如表1所列。注意文件的大小只與芯片的型號相關而和邏輯的復雜程度無關。

表1 XSVF文件大小

XSVF共而16個單字節(jié)指令,每一個指令后跟多少不等的單字節(jié)數據,如表2所列。

表2 XSVF指令

四、實現(xiàn)過程

本設計的實現(xiàn)過程如圖2所示。

第一步,利用XILINX提供的工具,用原理圖或HDL語言設計所需的邏輯,然后進行綜合。

第二步,將編程文件輸出為標準的JEDEC文件(*.jed)。

第三步,順JTAGProgrammer環(huán)境下,將編程文件進一步轉換為SVF文件。

第四步,利用VSF2XSVF軟件,將SVF轉換為XSVF。

第五步,將二進制的XSVF轉換為MCU可接受的相應格式。本設計中采用Intel公司16位單片機,所以生成Intel Hex格式文件。

當需要更新邏輯時,MCU從網絡總線上獲得更新后的XSVF文件(Intel Hex格式),暫存于RAM空間,然后讀取XSVF文件命令,逐條解釋,并予以執(zhí)行,即通過I/O口模擬JTAG的TAP口操作,產生編程指令、數據和控制信號,完成對CPLD的擦除、編程、校驗、讀寫保護設置等項工作。

-

單片機

+關注

關注

6067文章

44976瀏覽量

650182 -

cpld

+關注

關注

32文章

1257瀏覽量

171467 -

嵌入式

+關注

關注

5149文章

19655瀏覽量

317285

發(fā)布評論請先 登錄

如何實現(xiàn)單片機與CPLD通訊呢?

利用單片機實現(xiàn)CPLD的在系統(tǒng)編程

單片機應用系統(tǒng)的CPLD 應用設計

單片機與FPGA CPLD總線接口邏輯設計

基于單片機的CPLD/FPGA被動串行下載配置的實現(xiàn)

CPLD器件在單片機控制器中的使用

基于單片機和CPLD的頻率測量研究

單片機應用系統(tǒng)的CPLD應用設計

基于單片機+CPLD的多路精確延時控制系統(tǒng)設計

用CPLD實現(xiàn)單片機與ISA總線并行通信

基于CPLD的單片機PCI接口設計

用CPLD實現(xiàn)單片機與ISA總線并行通信

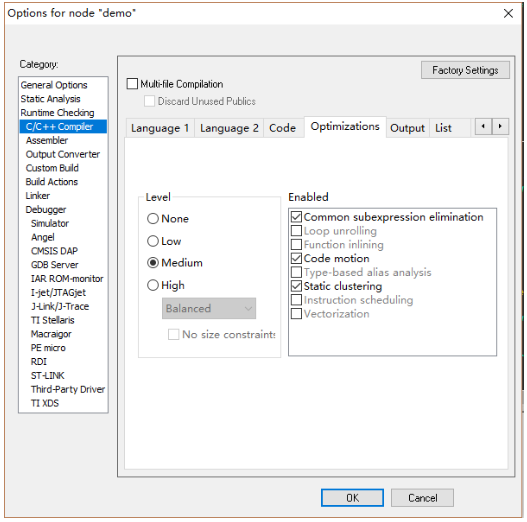

如何對IAR單片機編程軟件進行編譯優(yōu)化

單片機如何實現(xiàn)對CPLD進行編程

單片機如何實現(xiàn)對CPLD進行編程

評論