引言

256級灰度LED點陣屏在很多領域越來越顯示出其廣闊的應用前景,本文提出一種新的控制方式,即逐位分時控制方式。隨著大規模可編程邏輯器件的出現,由純硬件完成的高速、復雜控制成為可能。

逐位分時點亮工作原理

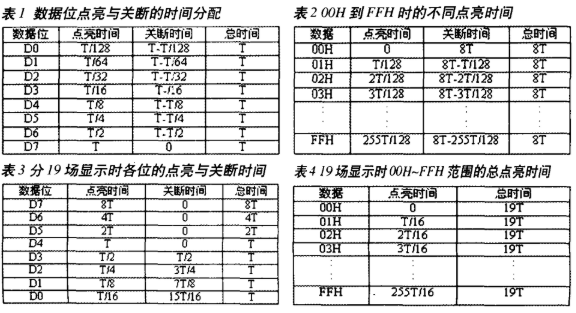

所謂逐位分時點亮,即從一個字節數據中依次提取出一位數據,分8次點亮對應的像素,每一位對應的每一次點亮時間與關斷時間的占空比不同。如果點亮時間從低位到高位依次遞增,則合成的點亮時間將會有256種組合。定義點亮時間加上關斷時間為一個時間單位,設為T 。表1列出了每一位的點亮與關斷的時間分配。

如果定義數據位“1”有效(點亮),“0”無效(熄滅),則表2列出了數據從00H到FFH時的不同點亮時間。由表2可知:數據每增1,點亮時間增加T/128。根據點亮時間與亮度基本為線性關系的原理,從0~255T/128的點亮時間則對應256級亮度。當然,這個亮度是時間上的累加效果。如果把一個LED點陣屏所有像素對應的同一數據位點亮一遍稱為一場的話,那么8位數據共需8場顯示完,稱為“8場原理”。

理論上講,8場即可顯示出256級灰度,然而通過表2可看出,即使數據為FFH時,在8T時間內也只是點亮了255T/128時間。關斷時間可接近6T,點亮時間僅為總時間的約25%,因此,8場原理雖也能實現256級灰度顯示,但亮度損失太大。為了提高亮度,可采用“19場原理”,即8位數據分19場顯示完,其中D7位數據連續顯示8場,D6位連續顯示4場,依次遞減。表3列出了各位的點亮與關斷時間。

由表3可推導出數據從00H~FFH范圍的總點亮時間,如表4所示。在19T時間內,最大點亮時間可達近16T, 占總時間的84.21%,遠大于“8場原理”的25%。數據每增1,點亮時間增加了T/16 ,該值大于“8場原理”的T/128。所以 ,“19場原理”較“8場原理”的對比度更明顯,圖像層次分明、表現力強。

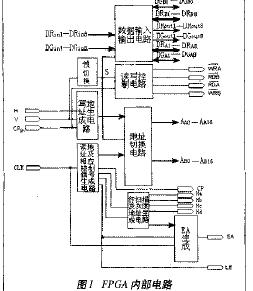

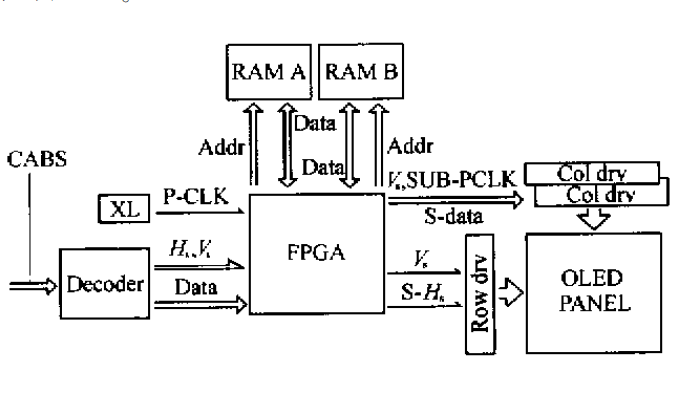

256級灰度LED點陣屏通常要具有能遠程同步實時顯示計算機視頻信號的功能,涉及到的電路包括:數字視頻信號的采集、數字信號的格式轉換及非線性校正、遠程傳輸及接收、灰度顯示控制電路、LED點陣顯示電路等。 本文重點討論“灰度顯示控制電路”的設計,控制對象以紅、綠雙基色LED點陣屏、1/16掃描顯示電路為例。FPGA內部電路如圖1所示。

因為被控對象為1/16掃描顯示電路,所以顯示屏每16行只需要一路數據信號即可。DRout1、 DGout1即為第一個16行的紅、綠基色輸出信號;DRout2、DGout2為第2個16行的紅、綠基色輸出信號。以此類推。

Ha、Hb、Hc、Hd的二進制編碼,定義當前的數據輸出應是16行中的哪一行。CP信號為數據串行輸出的同步移位脈沖。LE信號為一行串行數據輸出結束后的鎖存脈沖, LE每有效一次,Ha、Hb、Hc、Hd二進制編碼狀態增1。EA為灰度控制信號,其寬度為在一個時間單位T內LED的點亮時間。當然, 不同的數據位其寬度不同, 具體由表3決定。一個時間單位T即一行串行數據的傳輸時間,也即LE信號的周期,其大小取決于屏寬的像素點數量和CP信號的頻率。

DRin1~8和DGin1~8為紅、綠數據輸入信號,分別對應第1個16行點陣區到第8個16行點陣區。Cpin為同步脈沖,一個脈沖對應一位數據,8個脈沖對應一個像素點的8位數據輸入。H信號為行同步脈沖,一行數據輸入結束,H信號有效一次。V為幀同步脈沖,一幀(16行)數據輸入結束,V信號有效一次。上述信號均為前級系統提供的信號。

FPGA外部接有兩組高速靜態RAM(圖中未畫出),DRA1~8、DGA1~8為A組RAM的紅、綠數據線,DRB1~8、DGB1~8為B組RAM的紅、綠數據線;/WRA、/RDA為A組的讀、寫控制信號,/WRB、/RDB為B組的讀、寫控制信號;AA0~16為A組的地址線,AB0~16為B組的地址線。使用兩組RAM的目的是保證對RAM的讀寫操作能同時進行。當寫RAM(A)時,讀RAM(B);當寫RAM(B)時,讀RAM(A)。二者的寫/讀切換由幀信號V控制。V每有效一次,就進行一次切換。

Cpin為前級系統提供的寫脈沖,同時亦作為寫地址生成電路的計數脈沖,計數地址范圍為A0~A16, 共128K字節, 其中A0~A2為灰度位數據地址(決定訪問8位的哪一位)。A3~A12為X方向的像素地址,A13~A16為Y方向的像素地址,即行地址。H信號到來時,清零A0~A12,同時A13~A16地址加1。V信號到來時,A0~A12及A13~A16全部清零。上述地址作為RAM的寫地址。

CLK為讀地址生成電路計數脈沖(外電路提供),計數地址范圍亦為A0~A16, 共128K字節, 其中A0~A9為X方向的像素地址,A10~A13為Y方向的像素地址,即行地址。A14~A16為灰度位數據地址。上述地址 作為RAM的讀地址,這些地址的變化規律應符合“19場原理”對地址要求的變化規律,即:A0~A9計滿后清零,產生一個行信號即LE信號。LE信號作為A10~A13的計數脈沖,A10~A13計滿后清零,產生一個場信號。場信號作為A14~A16的計數脈沖。不過,A14~A16并不是一簡單的二進制計數,其規律如表5所示。為了能正確地讀取寫到RAM中的數據,生成的讀地址應按表6所示的方法與RAM連接。

讀寫控制電路的作用是向兩組RAM提供讀寫控制信號,邏輯關系如表7所示。數據輸入/輸出電路的作用是切換數據的傳輸方向,如表8所示。

幀切換電路的作用是產生上述電路所需要的切換信號S。實現的方法是,幀同步脈沖V每有效一次,S的邏輯狀態翻轉一次。幀切換電路保證了兩組RAM隨V信號不斷進行讀寫轉換。

灰度信號生成電路產生被控對象需要的EA信號,它隨讀地址A14、A15、A16的狀態而變化。邏輯關系如表9所示。

依據幀周期Tp=20ms,一幀=19場原理,可得如下計算結果: 場周期Tv=Tp/19=1.05ms; 行周期T=Tv/16=66ms; 輸出移位脈沖周期Tcp=T/1024=64ns;輸出移位脈沖頻率fcp=1/Tcp=15.6MHz。CLK信號頻率fclk=fcp=15.6MHz; 實際應用時,選取CLK時鐘信號頻率為16MHz。

在MAX PLUSII10.0環境下,使用圖形和硬件描述語言完成了以上電路的設計。

FPGA選型及仿真結果

由圖1可知,FPGA必須提供113個I/O引腳,內部資源、工作頻率須滿足電路設計要求。采用Altera公司的ACEX1K系列EP1K10QC208-3芯片,該FPGA芯片速度高、價位低、有114個I/O引腳,576個邏輯宏單元,可兼容輸入輸出電路的TTL電平。仿真結果報告: 引腳利用率達99%,內部邏輯單元利用率達到85 %,達到了充分利用資源、提高性價比的目的。

-

FPGA

+關注

關注

1645文章

22036瀏覽量

618119 -

led

+關注

關注

242文章

23828瀏覽量

673821 -

控制系統

+關注

關注

41文章

6780瀏覽量

112134

發布評論請先 登錄

基于FPGA EP1K10QC208-3芯片實現256級灰度LED點陣屏控制系統的設計

基于FPGA EP1K10QC208-3芯片實現256級灰度LED點陣屏控制系統的設計

評論