SoC芯片的規(guī)模一般遠(yuǎn)大于普通的ASIC,同時深亞微米工藝帶來的設(shè)計困難等使得SoC設(shè)計的復(fù)雜度大大提高。仿真與驗(yàn)證是SoC設(shè)計流程中最復(fù)雜、最耗時的環(huán)節(jié),約占整個芯片開發(fā)周期的50%~80%,采用先進(jìn)的設(shè)計與仿真驗(yàn)證方法成為SoC設(shè)計成功的關(guān)鍵。一個簡單可行的SoC驗(yàn)證平臺,可以加快SoC系統(tǒng)的開發(fā)與驗(yàn)證過程。FPGA器件的主要開發(fā)供應(yīng)商都針對自己的產(chǎn)品推出了SoC系統(tǒng)的開發(fā)驗(yàn)證平臺,如基于Nios II微處理器的SOPC系統(tǒng)與基于MicroBlaze微處理器的SOPC系統(tǒng)等。它們功能強(qiáng)大,而且配有相應(yīng)的開發(fā)環(huán)境與系統(tǒng)集成的IP核。但每個器件廠商的SOPC系統(tǒng)只適用于自己開發(fā)的器件,同時需要支付相應(yīng)的使用費(fèi)用且沒有源代碼,所以在學(xué)習(xí)以及普通設(shè)計開發(fā)驗(yàn)證中使用起來會有諸多的不便。

本文采用OpenCores組織所發(fā)布的32位微處理器AEMB作為SoC系統(tǒng)的控制中心,通過Wishbone總線互聯(lián)規(guī)范將OpenCores組織發(fā)布維護(hù)的相關(guān)IP核集成在目標(biāo)SoC系統(tǒng)上,構(gòu)成了最終的SoC驗(yàn)證平臺。

1 AEMB及Wishbone總線介紹

AEMB是一款高效的開源微處理器軟核,在指令上與Xilinx公司針對其器件開發(fā)的Microblaze微處理器兼容,而且在結(jié)構(gòu)上還有所增強(qiáng)。它主要有以下特點(diǎn):

①軟核設(shè)計得非常小,相對于其他的一些微處理器軟核,在物理實(shí)現(xiàn)上占用較少的硬件邏輯資源;

②支持硬件上的多線程,可以有效地執(zhí)行操作系統(tǒng)相關(guān)的代碼;

③AEMB是在LGPL3下開發(fā)的,所以它完全可以作為一個部分嵌入到一個大的設(shè)計中,同時非常適合一些科研院所以及高校或者個人用來學(xué)習(xí);

④支持Wishbone總線規(guī)范,可以非常容易地集成其他的一些支持Wishbone總線規(guī)范的開源IP核;

⑤完全通過一些參數(shù)來定義系統(tǒng)的可配置功能,如系統(tǒng)的地址空間和一些其他可選的功能單元;

⑥在指令上99%與EDK6.2兼容,可以方便地使用已經(jīng)非常成熟的開發(fā)工具鏈。

Wishbone總線規(guī)范是一種片上系統(tǒng)IP核互連體系結(jié)構(gòu)。它定義了一種IP核之間公共的邏輯接口,減輕了系統(tǒng)組件集成的難度,提高了系統(tǒng)組件的可重用性、可靠性和可移植性,加快了產(chǎn)品市場化的速度。Wishbone總線規(guī)范可用于軟核、固核和硬核,對開發(fā)工具和目標(biāo)硬件沒有特殊要求,并且?guī)缀跫嫒菽壳按嬖诘乃芯C合工具,可以用多種硬件描述語言來實(shí)現(xiàn)。Wishbone總線提供了4種不同的IP核互連方式:

◆點(diǎn)到點(diǎn)(point-to-point),用于兩IP核直接互連;

◆數(shù)據(jù)流(data flow),用于多個串行IP核之間的數(shù)據(jù)并發(fā)傳輸;

◆共享總線(shared bus),多個IP核共享一條總線;

◆交叉開關(guān)(crossbar switch),同時連接多個主從部件,可提高系統(tǒng)吞吐量。

2 SoC系統(tǒng)驗(yàn)證平臺總體框架

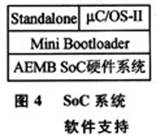

SoC系統(tǒng)中主要包含的IP模塊有:32位開源微處理器軟核AEMB、中斷控制器、時鐘定時器、Wishbone總線、片上RAM控制器、SDRAM控制器、SSRAM控制器、Flash控制器、UART16550控制器、GPIO控制器。整個SoC系統(tǒng)的總體結(jié)構(gòu)如圖1所示。

為了方便后續(xù)開發(fā)與應(yīng)用,本SoC系統(tǒng)中的Wishbone總線仲裁采用了開源的IP軟核wb_conmax。其為8×16的結(jié)構(gòu),即在該Wishbone總線模塊中可以使用8個主設(shè)備與16個從設(shè)備。本系統(tǒng)中使用了8個從設(shè)備接口和2個主設(shè)備接口。AEMB軟核中沒有提供時鐘定時器與中斷控制器,為了正常使用該軟核,本系統(tǒng)中加入了中斷控制器和時鐘定時器,這兩個控制器是作為從設(shè)備添加進(jìn)來的。針對一些對存儲空間需求很少的應(yīng)用,系統(tǒng)將片上RAM作為主存儲器。然而,F(xiàn)PGA片上存儲器的空間是非常有限的,為了能夠運(yùn)行需要大量存儲空間的操作系統(tǒng),以及讓系統(tǒng)正常上電啟動,就需要外部存儲器作為系統(tǒng)的主存儲器。所以,系統(tǒng)中還添加了SDRAM、SSRAM控制器及Flash存儲器。UART16550控制器和GPIO控制器作為2個從設(shè)備連接在系統(tǒng)中。

3 SoC系統(tǒng)驗(yàn)證平臺具體構(gòu)建

3.1 AEMB版本的選擇與配置

AEMB軟核采用最新的EDK62版本。本設(shè)計的目的在于整個SoC系統(tǒng)驗(yàn)證平臺的構(gòu)建,對微處理器性能及整個SoC系統(tǒng)的具體應(yīng)用性能沒有要求。為了簡化設(shè)計,將AEMB軟核中可配置的一些優(yōu)化選項(xiàng)全部禁掉。這樣不僅省去了對FPGA硬件邏輯資源的占用,而且也避免了因一些具體細(xì)節(jié)使用不當(dāng)而帶來的諸多問題。

3.2 片上RAM的生成

為了減少對FPGA邏輯資源的占用,同時又能夠滿足最基本的啟動代碼的存放與運(yùn)行,將片內(nèi)存儲器的大小設(shè)為4 KB。使用Altera公司的FPGA開發(fā)環(huán)境QuartusII 9.0中的MegaWizard Plug-In Manager工具,來生成設(shè)定大小為4 KB的片上RAM。EDA開發(fā)工具生成的片上存儲文件僅是具有相關(guān)存儲器地址、數(shù)據(jù)及讀寫控制信號的一個HDL描述文件。為了能夠在本SoC系統(tǒng)中使用,需要將其包裝成符合Wishbone總線接口的一個從設(shè)備,以掛接在系統(tǒng)的Wishbone總線上。

3.3 片外存儲控制器的配置

在該SoC系統(tǒng)上,片外存儲控制器主要有SDRAM、Flash、SSRAM控制器。根據(jù)***友晶公司的DE2-70開發(fā)板上實(shí)際存儲芯片的需要,對控制器的數(shù)據(jù)總線寬度與地址總線寬度作相應(yīng)的修改與定制。一般情況下,SDRAM作為系統(tǒng)的主存儲器,F(xiàn)lash用來存儲系統(tǒng)的一些固化程序。在對一些實(shí)時系統(tǒng)進(jìn)行時間參數(shù)測量的過程中,為了減小程序運(yùn)行空間中時序的不穩(wěn)定性影響,一般情況下測試程序都是在SSRAM器件中運(yùn)行的。

作為存儲器件的物理芯片,數(shù)據(jù)總線的端口基本上都是雙向的,而在片內(nèi)系統(tǒng)中數(shù)據(jù)端口基本上都是單向的。這些片外存儲控制器在進(jìn)行物理板級的連接時需要對相應(yīng)的數(shù)據(jù)端口作處理。以Flash控制器為例,數(shù)據(jù)總線的雙向I/O口具體實(shí)現(xiàn)RTL代碼如下:

其他的存儲器(如SDRAM、SSRAM)的數(shù)據(jù)總線雙向I/O的實(shí)現(xiàn),也都是采用這種方法來完成的。

3.4 中斷控制器與時鐘定時器的配置

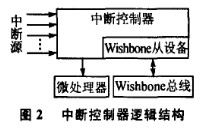

中斷控制器主要用于接收外部中斷源的中斷請求,并對中斷請求進(jìn)行處理后再向CPU發(fā)出中斷請求,等待CPU響應(yīng)中斷并進(jìn)行處理。在CPU響應(yīng)中斷的過程中,中斷控制器仍然負(fù)責(zé)管理外部中斷源的中斷請求,從而實(shí)現(xiàn)中斷的嵌套與禁止。在本設(shè)計中,中斷控制器的邏輯結(jié)構(gòu)如圖2所示。所采用的中斷控制器主要負(fù)責(zé)接收片內(nèi)IP核及片外器件所發(fā)出的中斷請求,然后根據(jù)一定的優(yōu)先級與規(guī)則將中斷發(fā)送給微處理器。微處理器可以通過設(shè)置與讀取相應(yīng)的中斷寄存器來管理查看中斷優(yōu)先級與中斷狀態(tài)。

時鐘定時器主要是作為操作系統(tǒng)的時鐘滴答定時器,本質(zhì)上就是一個簡單的計數(shù)器。在每個系統(tǒng)時鐘來到時計數(shù)器會自動加1,當(dāng)計數(shù)器的值達(dá)到設(shè)定數(shù)值時便產(chǎn)生1次時鐘中斷。PTC是OpenCores組織發(fā)布的一個支持Wishbone總線接口的脈沖定時計數(shù)器。其不僅可以作為時鐘定時器,還可以通過配置寄存器的設(shè)置產(chǎn)生PWM脈沖輸出。本SoC系統(tǒng)中主要是使用PTC的定時器功能。

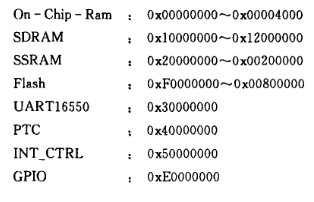

3.5 地址空間的分配

根據(jù)DE2-70開發(fā)板上各器件的特點(diǎn)與AEMB微處理器的中斷例外向量表及wb_conmax的邏輯實(shí)現(xiàn),系統(tǒng)地址空間分配結(jié)果為:

4 SoC系統(tǒng)的FPGA綜合實(shí)現(xiàn)

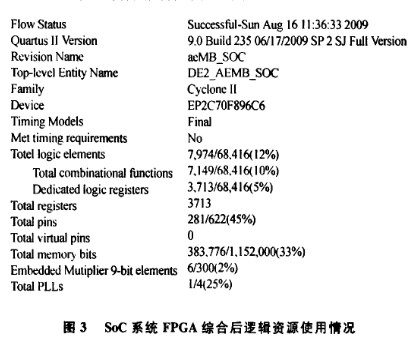

針對DE2-70開發(fā)板在進(jìn)行SoC系統(tǒng)的FPGA綜合時選用CycloneII系列器件EP2C70F896C6。系統(tǒng)時鐘頻率預(yù)設(shè)為50 MHz,不加額外約束條件下進(jìn)行綜合,綜合后的邏輯資源占用報告如圖3所示。

通過時序分析報告可知,該SoC系統(tǒng)在滿足時序的前提下,系統(tǒng)實(shí)際運(yùn)行頻率可達(dá)到65.31 MHz。

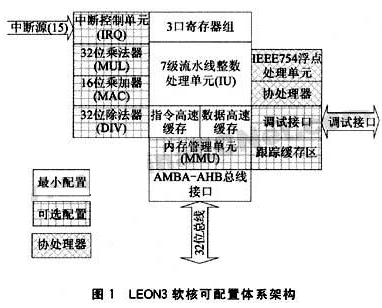

5 SoC系統(tǒng)驗(yàn)證平臺軟件支持

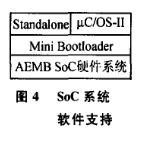

考慮到SoC驗(yàn)證平臺所包含的硬件部件與該平臺的具體應(yīng)用,系統(tǒng)軟件主要構(gòu)成如圖4所示。Mini Bootloader負(fù)責(zé)應(yīng)用程序從Flash器件向程序運(yùn)行空間的加載。在DE2-70開發(fā)板上,借助于NiosII開發(fā)工具與開發(fā)板自帶的基于NiosII的SOPC硬件系統(tǒng),燒寫Flash很方便。系統(tǒng)啟動時可以從Flash開始啟動,完成應(yīng)用程序的拷貝后再跳轉(zhuǎn)到主程序運(yùn)行的存儲器空間。在本系統(tǒng)中,為了使編程更加方便,將拷貝程序放在片上RAM中存儲。系統(tǒng)從片上RAM開始啟動,完成應(yīng)用程從Flash到SDRAM的拷貝之后,跳轉(zhuǎn)到SDRAM開始執(zhí)行應(yīng)用程序。

AEMB微處理器在指令上與MicroBlaze達(dá)到99%的兼容,而后者的應(yīng)用程序及操作系統(tǒng)的開發(fā)已經(jīng)有非常成熟的范例。操作系統(tǒng)的移植主要是完成對硬件地址空間的修改與操作系統(tǒng)一些底層初始化代碼的編寫。最終在該SoC系統(tǒng)驗(yàn)證平臺上完成了μC/OS-II的移植工作。

結(jié) 語

本文基于32位微處理器AEMB設(shè)計了一款SoC系統(tǒng)驗(yàn)證平臺,給出了SoC系統(tǒng)經(jīng)過FPGA綜合后的邏輯資源占用情況,以及系統(tǒng)能夠運(yùn)行的最高時鐘頻率。該平臺已在***友晶公司的DE2-70開發(fā)板上完成了FPGA驗(yàn)證。

-

asic

+關(guān)注

關(guān)注

34文章

1242瀏覽量

121905 -

soc

+關(guān)注

關(guān)注

38文章

4318瀏覽量

221473 -

微處理器

+關(guān)注

關(guān)注

11文章

2365瀏覽量

83754

發(fā)布評論請先 登錄

處理器及微處理器系統(tǒng)

基于AVR 8位微處理器的FSPLC微處理器SOC設(shè)計

龍芯處理器IP核的FPGA驗(yàn)證平臺該怎么設(shè)計?

龍芯處理器IP核的FPGA驗(yàn)證平臺該怎么設(shè)計?

SoC驗(yàn)證平臺的FPGA綜合怎么實(shí)現(xiàn)?

怎樣去構(gòu)建一種SoC系統(tǒng)驗(yàn)證平臺?

STM32微處理器

基于IDE構(gòu)建用于STM32微處理器的完整人工智能項(xiàng)目

AEMB軟核處理器設(shè)計的SoC系統(tǒng)驗(yàn)證平臺

S3C4510B型ARM微處理器最小系統(tǒng)構(gòu)建

龍芯處理器IP核的FPGA驗(yàn)證平臺設(shè)計

基于FPGA的驗(yàn)證平臺及有效的SoC驗(yàn)證過程和方法

利用FPGA軟硬件協(xié)同系統(tǒng)驗(yàn)證SoC系統(tǒng)的過程和方法

基于LEON開源微處理器IP軟核實(shí)現(xiàn)SoC系統(tǒng)基本平臺的構(gòu)建

基于AEMB微處理器構(gòu)建SoC系統(tǒng)驗(yàn)證平臺

基于AEMB微處理器構(gòu)建SoC系統(tǒng)驗(yàn)證平臺

評論