過渡至65納米工藝的FPGA具備采用更小尺寸工藝所帶來的優勢:低成本、高性能和更強的邏輯能力。盡管這些優勢能夠為高級系統設計帶來激動人心的機會,但65納米工藝節點本身也帶來了新的挑戰。例如,在為產品選擇FPGA時,功耗的考慮變得越來越重要。很可能下一代設計會需要在功耗預算不變(或更小)的情況下,集成更多的特性和實現更高的性能。

本文將分析功耗降低所帶來的益處,還將介紹Virtex-5器件中所采用的多種技術和結構上的革新,它們能提供功耗最低的解決方案,并且不犧牲性能。

1 降低功耗的好處

低功耗的FPGA設計所帶來的優勢不僅是能滿足器件工作的散熱要求。雖然滿足元件指標對于性能和可靠性十分重要,但如何實現這一點對于系統成本和復雜性都有著巨大的影響。

首先,降低FPGA的功耗使設計人員能夠采用更便宜的電源,這樣的電源使用的元件數量較少,并且占用的PCB面積也較小。高性能電源系統的成本通常為每瓦0.5到1美元。低功耗的FPGA直接降低了系統的整體成本。

其次,由于功耗直接與散熱相關,低功耗使設計人員能夠使用更簡單、更便宜的熱量管理解決方案。在很多情況下,設計者將不再需要散熱器,或者只需要更小、更便宜的散熱器。

最后,由于低功耗工作意味著更少的元件和更低的器件溫度,因此將提高整個系統的可靠性。器件工作溫度每降低10℃,就相當于元件壽命提高了兩倍,因此對于需要高可靠性的系統而言,控制功耗和溫度十分重要。

2 功耗:挑戰和解決方案

FPGA(或任何半導體器件)中的總功耗等于靜態功耗和動態功耗之和。靜態功耗主要由晶體管的泄漏電流引起,即晶體管在邏輯上被關斷時,從源極“泄漏”到漏極或通過柵氧“泄漏”的小電流。動態功耗是器件核心或I/O在開關過程中消耗的能量,與頻率相關。

2.1 靜態功耗

在縮小晶體管尺寸時(例如,從90納米到65納米),泄漏電流將會增大。新工藝節點所使用的短溝長和薄柵氧使電流更容易從晶體管的溝道區或通過柵氧泄漏。

在90納米Virtex-4系列產品中,賽靈思公司使用了“三柵極氧化層”的工藝技術,向電路設計者提供了一種強有力的阻止漏電工具。在前幾代FPGA中,使用兩種柵氧厚度:薄柵氧用于FPGA核心中高性能、低工作電壓的晶體管,而厚柵氧用于I/O模塊中尺寸較大,需要承受大電壓的晶體管。簡言之,“三柵極氧化層”指增加一種中間厚度柵氧的晶體管,它的漏電比薄柵氧的核心晶體管要小得多。

“中間柵氧”的晶體管用在器件核心外圍非關鍵性能的電路(像設置存儲器)或不需要對變化的柵壓進行快速開關響應的電路(像傳輸門)中。薄柵氧、漏電最大的晶體管只保留在需要快速開關速度的路徑部分。結果,總的器件漏電大幅減小,同時性能比上一代FPGA有很大提高。

三柵極氧化層工藝使Virtex-4器件比競爭性90納米FPGA在靜態功耗上平均減少了超過70%。這一結果非常成功,因此Virtex-5系列產品中大量使用了這一技術,在65納米工藝節點上降低漏電。

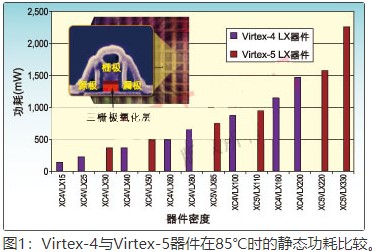

盡管業界預測65納米器件的靜態功耗將會大幅提高,但是圖1顯示了三柵極氧化層工藝使65納米Virtex器件在最壞(溫度最高)工作條件下達到了與尺寸相當的90納米Virtex-4器件相同水平的靜態功耗。因此,Virtex-5系列產品和競爭性高性能FPGA產品相比,在靜態功耗方面具有真正的優勢。

圖1:Virtex-4與Virtex-5器件在85℃時的靜態功耗比較。

2.2 動態功耗

動態功耗為65納米FPGA帶來一些其它方面的挑戰。動態功耗的公式為:

動態功耗=C×V2×f

其中,C是總開關電容、V是電源電壓、f是開關頻率。65納米工藝使FPGA的邏輯能力和性能比傳統器件有了顯著提高,也就是說更多的結點工作在更高的頻率上。

如果其它方面的條件不變,動態功耗將會增大。不過對于動態功耗而言,也有一個好消息:FPGA電源電壓和結點電容通常在每一代新工藝中都會下降,從而使得動態功耗比上一代FPGA有所下降。

Virtex-5器件中,核心電源電壓(VCCINT)從Virtex-4中所使用的1.2V下降到1.0V。由于寄生電容變小(與更小的晶體管相關),以及邏輯塊間的互聯線長度變短、電容變小,使結點電容減小。此外,Virtex-5器件在金屬互聯層之間使用了一種介電常數較低的材料。

Virtex-5器件的平均結點電容比Virtex-4器件大約減小了15%。加上電壓降低帶來的好處,至少相當于將Virtex-5器件的核心動態功耗降低了35~40%。

除了因工藝尺寸縮小到65納米所致固有的35~40%動態功耗降低外,Virtex-5器件的架構創新還能進一步降低每個設計的功耗。大多數可增加動態 功耗的結點電容,是由邏輯單元間的互連線引起的。新型Virtex-5架構從以下方面減小了連線電容:

Virtex-5的可配置邏輯模塊(CLB)是基于6輸入查找表(6-LUT)邏輯結構的,在以前的器件中是使用4輸入查找表。這意味著在每個LUT中能夠實現更多的邏輯,相當于較少的邏輯級,從而降低了對邏輯單元之間大電容連線的需求。

Virtex-5的互聯結構目前包括了對角線對稱的連線,意味著每個CLB與所有相鄰的模塊(包括處于對角線位置的模塊)之間都有直接的“單一”連接。當邏輯功能之間需要連接時,這一連接更有可能成為總電容最小的“單一”連接,而以往的互聯結構對于相同的連接問題可能會需要兩個或更多結點。

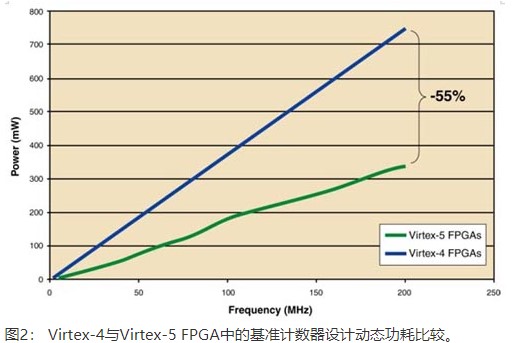

6-LUT結構和改進的互聯模式,通過降低平均結點電容來降低核心動態功耗,效果遠遠超過僅使用65納米工藝所帶來的改進。圖2顯示了來自標準設計的核心動態功耗的測量結果,其中每個Virtex-5器件和Virtex-4器件中都有1,024個8位計數器。這些實際的測量結果顯示,工藝和結構上的共同優化所帶來的動態功耗的降低超過了50%。

2.2 硬IP模塊

Virtex-5器件中所包含的硬IP模塊(專門用來實現一些常用功能的電路)數量,超過業界其他任何一款FPGA。相比使用通用FPGA邏輯而言,使用搭載這些模塊的FPGA設計來實現相同功能,可進一步降低功耗。

與FPGA結構不同,這些專用模塊中只含有為實現所要求功能而必需的晶體管,并且沒有可編程的互聯,因此互聯電容最小。較少的晶體管和較小的結點電容能降低靜態和動態功耗。因而這些專用模塊在實現相同功能的同時,功耗只有采用通用FPGA結構的十分之一。

除了增加新型的專用模塊之外,Virtex-4器件中融合的很多模塊,在Virtex-5器件中都被重新設計,以增加新的特性,提高性能并降低功耗。例如,Virtex-4系列中18Kb的block RAM存儲器在Virtex-5器件中被增加到了36Kb;每個block RAM能被分成兩個獨立的18Kb的存儲器,以便向下兼容Virtex-4的設計。

有趣的是,從功耗的角度來看,每個18Kb的子模塊由兩個9Kb的物理存儲陣列構成。對于大多數block RAM配置,任何對block RAM的讀寫請求一次只需要訪問9Kb物理存儲器中的一個。因此其余的9Kb存儲器能在不被訪問時可有效地“關斷”。在過渡至65納米工藝所帶來的功耗降低的基礎上,這種結構又使功耗進一步降低了50%。這一對于9Kb模塊的乒乓式存取是新型block RAM結構所固有的,這就意味著使用這項功能不需要用戶或軟件來進行控制。它能動態并自動地進行,使所有使用block RAM的設計降低了大量的功耗,并且不會影響模塊的性能。

Virtex-5器件中專用的DSP元件也進行了大量的改進,以實現更多的功能,提高性能并降低功耗。在片與片的功耗比較中,新型的Virtex-5 DSP片比Virtex-4 DSP片降低了大約40%。這主要歸功于前面所討論的65納米工藝中電壓和電容的減小。

然而,由于Virtex-5 DSP片具有更強的功能和更廣泛的接口,許多DSP運算通過利用這些附加的功能進一步降低了功耗。在許多情況下,當使用新型DSP片的全部功能時,總功耗最高可降低75%。即使你不是在設計一個DSP產品,也能使用DSP片來實現標準的邏輯功能(計數器、加法器、桶式移位器),這樣會比在標準FPGA邏輯中實現同樣的功能節省功耗。

最后介紹經過改進的專用模塊——Virtex-5系列的LXT平臺,其中包括了幾吉位的串行收發機,能以高達3.125Gbps的速率工作。這些“SERDES”模塊在實現時著重考慮了低功耗需求。每個Virtex-5 LXT器件中的全雙工收發機在3.125Gbps的速度下的總功耗小于100mW,與Virtex-4串行收發機相比降低了大約75%。

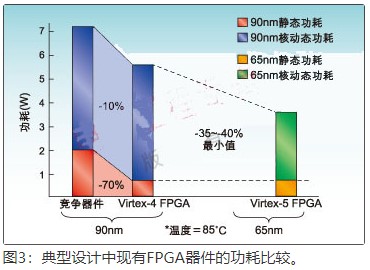

與Virtex-4系列產品一樣,Virtex-5器件也采用了一系列工藝和架構上的革新,力求在提供盡可能低的功耗的同時,仍然使性能提高30%或更多。如圖3所示,Virtex-5系列產品的靜態功耗與Virtex-4器件相當,但比競爭性FPGA具有明顯的優勢。

Virtex-5器件核心的動態功耗比市場上其高性能FPGA低至少35~40%。新型6-LUT和對角線對稱的互聯等架構上的革新,使實際核心動態功耗進一步降低了50%或以上。此外,利用改進的專用模塊也進一步降低了功耗。

-

電源

+關注

關注

185文章

18372瀏覽量

256299 -

FPGA

+關注

關注

1645文章

22050瀏覽量

618476 -

半導體

+關注

關注

335文章

28918瀏覽量

237909

發布評論請先 登錄

基于Virtex-5器件的QDR II SRAM接口設計

如何在VIrtex-5器件上實現擴展LVDS?

Virtex-5亞穩態保護是什么

在Virtex-5 FPGA中如何使用BRAM代替SRAM

Xilinx Virtex-5 FXT FPGA開發方案

Virtex-5 Embedded Tri-Mode Eth

基于Virtex-5 FPGA的音視頻監視系統設計

利用Virtex-5 SXT 的高性能DSP解決方案

WWP248 - 移植到Virtex-5 FPGA的指南

WP245 - 使用Virtex-5系列FPGA獲得更高系統性能

如何利用Virtex-5器件實現最小功耗

如何利用Virtex-5器件實現最小功耗

評論