I. 引言

歷史上,MFP和打印機廠商都是開發定制ASIC或SoC器件來執行圖像處理操作。這些ASIC/SoC器件包括圖像流水線,用以接受來自CCD或CIS傳感器的RGB數據,執行濾波、縮小/放大、色彩空間轉換、圖像分割和半色調操作。然后,由此產生的經處理的圖像使用減色著色劑進行打印:青色、品紅、黃色和黑色。其目標是在打印副本上精確地再現原始文檔,而不引入視覺假像。

在底層技術(如DDR內存和USB連接)變得過時之前,ASIC/SoC器件通常有三年的有限壽命。隨著硅技術的不斷萎縮,開發一個定制ASIC/SoC所需的投資在繼續增加。一個采用雙核處理器、必要的連接、DDR3內存控制器、圖像處理、GPU、LCD控制器等的28納米SoC的設計、開發和交付需要花費超過1000萬美元的成本。

取決于許多因素,大型SoC/ASIC器件的開發周期要花18至30個月,包括新IP的數量和大小、利用以往設計的能力、設計團隊經驗和成熟的有針對性的硅技術。

打印機/MFP市場的產品周期是24到36個月的時間。打印機/MFP市場成長速度平緩,增加了以較低成本和較短開發周期提供更多功能的競爭壓力。

隨著ASIC/SoC開發周期接近同一時間MFP產品的生命周期,MFP/打印機廠商需要一個新的平臺來縮短開發和部署周期。基于SoC的OpenCL和FPGA的組合為解決這一難題提供了一個有趣的解決方案。

II. MFP圖像處理流水線背景

一個重要的研究機構已經在文檔圖像處理領域積累了近20年的經驗]。大部分早期工作都側重于圖像處理的基礎知識,包括提供統一色彩的校準輸入傳感器數據、去除來自傳感器噪聲的濾波,實現圖像尺寸縮小或放大的縮放算法,以及實現使用二進制像素打印連續色調圖像數據的半色調。當前的文檔圖像處理研究和開發處于圖像分析、內容提取和數據壓縮技術領域。

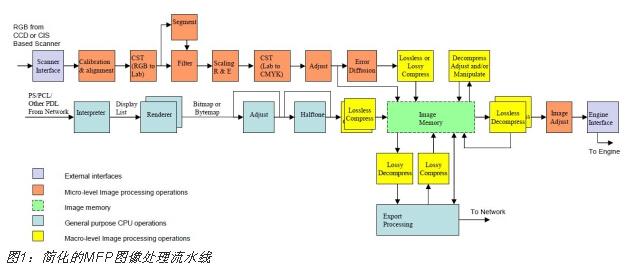

所有MFP文檔圖像處理產品都可執行一系列基本功能——復印、掃描和打印。圖1用圖形說明了一臺個MFP設備的基本功能或流水線。復印和掃描的操作相類似,開始于從一個掃描設備到設備無關的彩色空間的原始RGB數據轉換。復印操作進一步處理設備無關的色彩空間圖像,并創建用于打印的CMYK圖像。掃描操作在設備無關的色彩空間圖像上執行一組不同的圖像處理操作。這些操作可以包括:圖像分析、用不同頻率內容將圖像分割為多個圖像層、OCR、光學字符識別和數據壓縮。然后,所產生的圖像轉被移到任一本地存儲介質,如USB閃存驅動器或網絡設備。

圖字:

來自CCD或基于CIS掃描儀的RGB;分割

掃描儀接口;校準和調整;CST(RGB到Lab);濾波器;縮放R & E;CST(Lab到CMYK);調整;誤差擴散;無損或有損壓縮;解壓縮調整和/或操作

來自網絡的PS/PCL/其他PDL;解譯;顯示列表;渲染器;位圖或字節圖;調整;半色調;無損壓縮;圖像存儲;無損解壓縮;圖像調整;引擎接口

有損解壓縮;有損壓縮;至引擎

出口處理;至網絡

外部接口;微觀圖像處理操作;圖像存儲;通用CPU操作;宏觀圖像處理操作

打印功能接收一個采用PDL(頁面描述語言)的編碼,或圖形顯示接口格式的文件。在采用PDL文件的情況下,MFP設備必須首先解釋文檔語言,并創建一個原始對象列表。渲染器捕獲這些對象,并將其轉換成數字CMYK位圖/位圖圖像。所產生的數字圖像可被進一步處理和隨意壓縮。GDI打印機不需要解釋過程,因為傳送到打印機的圖像是一個顯示對象的列表。

一旦打印或復印流水線創建了CMYK位圖/位圖圖像,圖像即被發送到引擎在所需介質上打印。

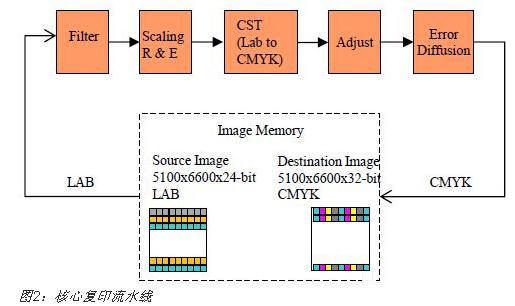

本文的重點是一個OpenCL MFP核心復印流水線(CCP)的開發,如圖2所示。

圖字:

濾波器;縮放R & E;CST(Lab到CMYK);調整;誤差擴散

圖像存儲

源圖像5100x6600x24位LAB;目標圖像5100x6600x32位CMYK

III. MFP核心復印流水線

CCP由5個內核組成:7×7濾波器;用pad/crop縮放或減小與放大;色彩空間轉換;調整和誤差擴散。我們將簡要地回顧各個算法和相關的內存需求。

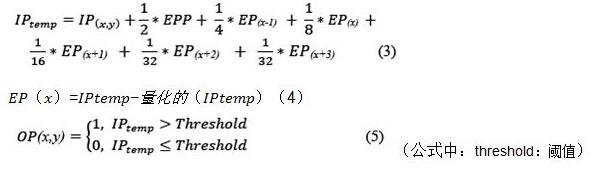

A. 7×7濾波器

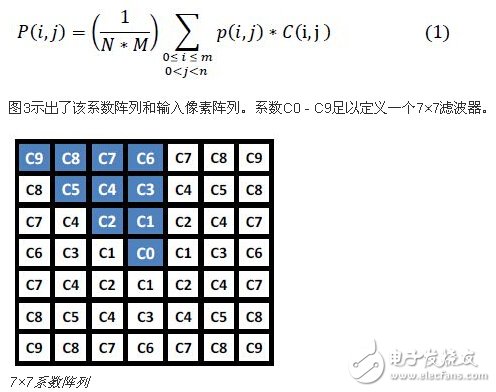

7×7濾波器是一個2D對稱濾波器,可降低圖像噪聲。它的每一行需要跨連續7行乘連續7個像素的49個像素的上下文(context)。MFP應用通常使用一組系數來實現一個平均或銳化濾波器。7×7濾波器的一般形式是:

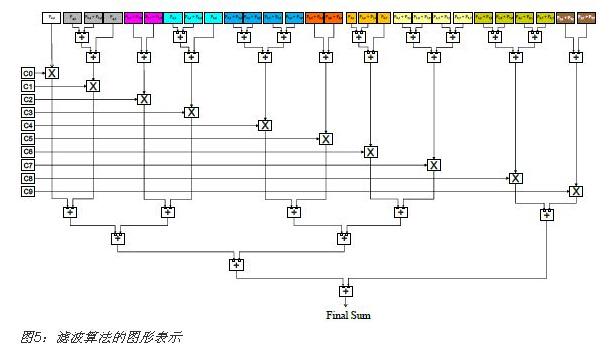

由于系數值經常重復,濾波處理可以避免重復的乘法和加法。相反,乘以相同系數的像素可首先加入,然后與濾波器系數相乘一次。圖4直觀地顯示了潛在的優化。這個數字僅為了清晰起見,并不代表OpenCL設計。

圖字:

M每頁掃描線

N每掃描線像素

像素;減少的濾波矩陣;有相同顏色的條目分享共同系數

工作矩陣對稱濾波器計算的高度概括,針對左到右滑動進行了優化,包括:

1. 針對每一個加載的新的像素欄3種加法A

2. 針對屬于圖4所示4×7矩陣中相同濾波器系數像素的18種加法

3. 針對每個系數一個C0至C9的10種乘法M

4. 計算系數乘法最終結果的9種加法

那么,計算的總數是10M + 3A + 18A + 9A = 10M + 30A。圖5示出了計算樹。

隨著濾波器在圖像上從左至右的滑動,僅需要加載最右側像素列,即7個像素。邏輯上,這涉及將內部像素列移到左邊,并在右側加上新的像素列。

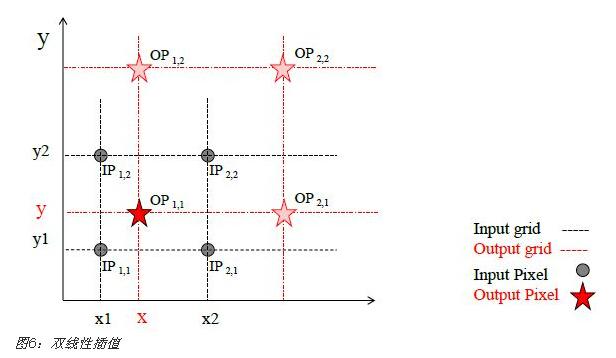

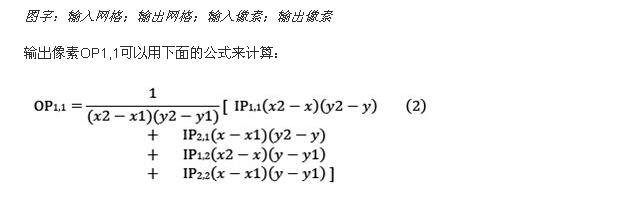

B. 縮放

縮放模塊使用雙線性插值來減小和/或放大一幅圖像。雙線性插值是一個眾所周知的算法,在所需的新輸出像素周圍使用了4個輸入像素。圖6示出了要測試像素的雙線性插值輸入和輸出網格。

C. 色彩空間轉換

CCP采用設備無關的色彩空間數據,通常是LAB格式,并將其轉換為設備相關的CMYK色彩空間。不幸的是,沒有公式化的方法來直接轉換L*a*b*至CMYK。每臺打印機的著色劑以非線性方式進行交互。打印行業的公認方法是打印測試斑點,測量所得色,并創建一組C、M、Y和K查找表,即LUT。關鍵是要盡量減少LUT的大小,同時提供最高的色彩保真度。為了計算這些存儲在LUT之間的值,我們必須使用一個插值方案。有許多方法來執行插值,但四面體插值法被廣泛認為是最準確的。

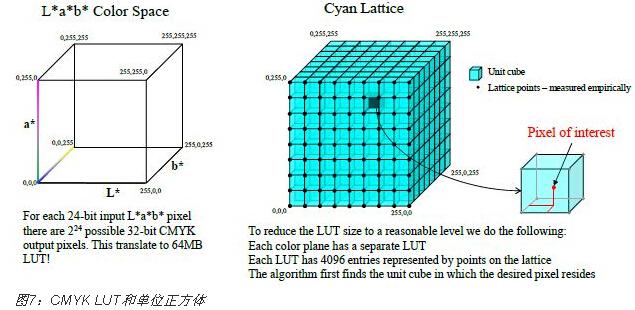

顧名思義,四面體插值法使用4個已知點來計算一個中間點。在我們的L*a*b*情況下,這些已知點的每一個都具有對應于輸入色彩空間的三個維度。三個輸入維度L、a、b形成一個我們可以用來確定輸出像素的立方體。圖7示出了色彩空間和LUT概念。注意每個輸出彩色平面都有獨立的LUT。

圖字:

第一張圖:

L*a*b* 色彩空間

下方注解:

對于每24位輸入L*a*b*像素,可能有224個32位CMYK輸出像素。這相當于64MB LUT!

第二張圖:

青色點陣

單位立方體

格點——憑經驗測量

感興趣的像

要使LUT大小降低到一個合理水平,我們可執行以下操作:

每彩色平面有各自的LUT

每個LUT有代表點陣點的4096個條目

算法首先發現期望像素點駐留的單位立方體

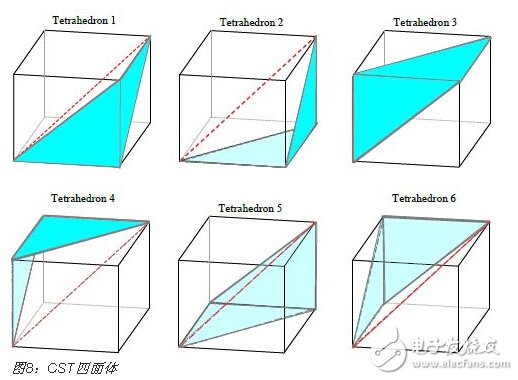

一旦算法確定了哪一個單位立方體包含要測試的輸出像素,我們必須從一組8個已知像素中計算出輸出像素。這是三線性插值的實際情形。四面體插值法利用一個單位立方體可以被劃分成一組6個非重疊四面體的方法,其每個終點都位于單位立方體的頂點。使用一個四面體(有4個點)內插來削減一半像素數時,我們必須使用插值結果。圖8以圖形示出了六個四面體。

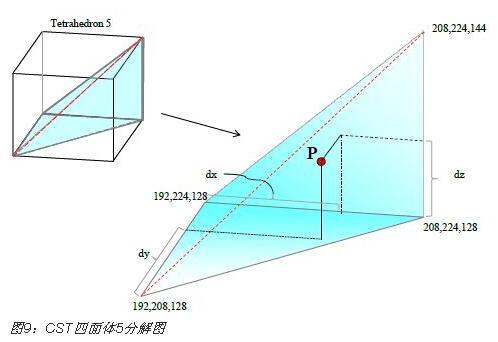

CST算法首先確定了輸出像素(P)駐留在哪個四面體中,并使用了4個已知輸出像素插入最終結果——見圖7。圖9示出了四面體5中的像素P。該算法計算了每個單位立方體軸端點和像素dx、dy、dz之間的距離,并使用了已知點之間的線性插值距離。

D. TRC調整

TRC調整算法是一個簡單的LUT。它允許C、M、Y、K值的進一步調整,以校正非線性色調再現。具體C、M、Y、K LUT條目憑經驗來測量。

E. 誤差擴散

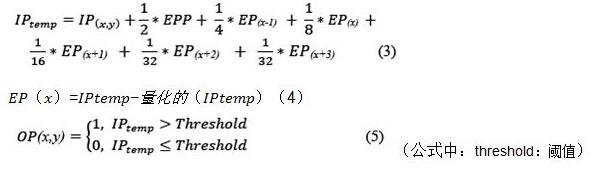

最后階段執行半色調功能。彩色激光MFP產品使用一個激光系統來消除感光介質上的電荷。無論電荷清除的是C、M、Y、K,墨粉都不能轉移到感光體。激光束掃過移動的感光體,被調制來創建一個倒置的圖像。調制的最小時間周期是一個像素。在反轉圖像被寫入感光體后,它經過一個墨粉分配器附近。然后,帶有相反電荷的墨粉被吸引到電荷存在的感光區。墨粉“粘”到感光體上。最后一個步驟是將感光體上的圖像轉印到紙張或其他介質上。單個像素或開或關,實現二進制的1過程。來自TRC內核的8位CMYK像素必須半色調或二進制化,以驅動打印機中的激光系統。有許多算法可以將連續色調數據轉換為二進制數據。誤差擴散是MFP/打印機中使用的一種通用算法。我們選擇了實施眾所周知的弗洛伊德-斯坦伯格(Floyd-Steinberg)誤差擴散算法的一個變種,它有簡單的算術修正系數[7]。

弗洛伊德-斯坦伯格誤差擴散量化了基于一個閾值陣列的輸入像素,然后將剩余誤差分配到相鄰像素。在我們的案例中,我們將一個8位輸入像素減少到二進制輸出像素。因此,我們的閾值陣列是一個127的值。大于127的輸入像素成為了邏輯1。≤127的像素成為了0。該算法定義如下:

1. IP(x,y)是當前輸入像素

2. EPP是來自以前像素的剩余閾值誤差,IP(x-1,y)

3. EP是來自以前掃描線的誤差矢量,y-1。

IV. ALTERA OpenCL編譯器

超出實際OpenCL代碼的OpenCL系統的最關鍵部分是編譯器。針對OpenCL 13.1,Altera SDK提供了一些獨特的功能,包括[8]:

A. 通道

B. I/O通道

C. 內存訪問合并(coalescing)

D. 自動循環流水線

E. 移位寄存器推理

A. 通道

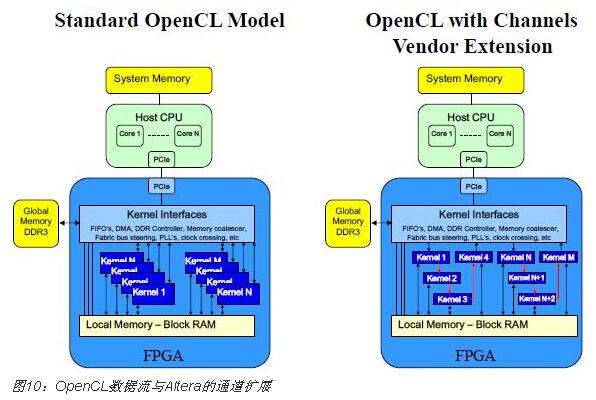

標準OpenCL模型假設內核運行在基于全局內存的數據集。由內核#1從全局內存讀取一個輸入塊,經處理將其結果寫回全局內存的不同部分。如果第二個內核需要進一步處理來自內核#1的結果,就必須等待,直到內核#1完成,所有輸出數據被寫回全局內存。只有這樣,內核#2才能讀取和處理數據。顯然,這個連續過程導致了流水線延遲,每個額外內核都以最佳線性增加的。而且,內存的每一次進出都增加了全局內存帶寬,并降低了流水線吞吐量。為了解決這個問題,Altera提供了內核通道的概念,它允許來自內核#1的輸出結果直接轉到內核#2的輸入。Altera離線編譯(AOC)增加了所有必要的同步邏輯和FIFO存儲器,允許數據從子內核n傳遞給內核n+1。圖10顯示了標準OpenCL和Altera廠商擴展通道數據流。

圖字:

標準OpenCL模型:

系統內存

主機CPU

核心1;核心N

全局內存DDR3;內核接口

FIFO、DMA、DDR控制器、內存聚結器、結構總線轉向、PLL時鐘交錯,等

內核N;內核;內核;內核1;內核M;內核;內核;內核N

本地內存——RAM塊

內核

FPGA

有通道廠商擴展的OpenCL:

系統內存

主機CPU

核心1;核心N

全局內存DDR3;內核接口

FIFO、DMA、DDR控制器、內存聚結器、結構總線轉向、PLL時鐘交錯,等

內核N;內核2;內核3;內核4;內核N;內核M;內核N+1;內核N+2

本地內存——RAM塊

內核

FPGA

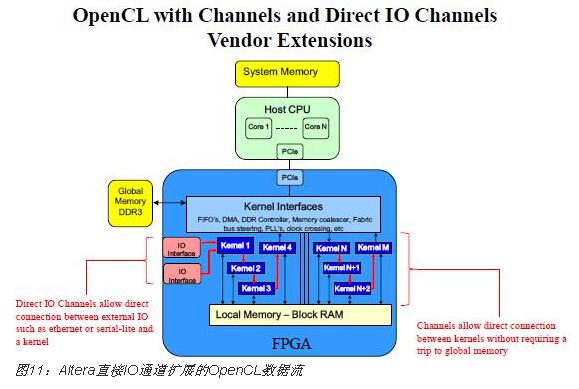

B. IO通道

IO通道是一個擴展通道概念,它允許外部IO直接連接到OpenCL內核。IO通道允許外部端口,如以太網、串行LVDS或OEM專用接口連接到內核,而無需首先進入全局內存。

在我們的MFP例子中,IO通道可以允許RGB掃描儀數據饋送到校準內核,然后連接到CCP。此外,CCP誤差擴散輸出視頻數據可以饋送到在彩色打印機上打印圖像數據的一個引擎內核。(請注意,我們尚未實現IO通道。這是留給未來的工作。)圖11示出了IO通道數據流。

圖字:

有通道和直接IO通道廠商擴展的OpenCL

系統內存

主機CPU

核心1;核心N

全局內存DDR3;內核接口

FIFO、DMA、DDR控制器、內存聚結器、結構總線轉向、PLL時鐘交錯,等

IO接口

IO接口

內核1;內核2;內核3;內核4;內核N;內核M;內核N+1;內核N+2

本地內存——RAM塊

內核

FPGA

左邊紅字注解:直接IO通道允許外部IO(如以太網或串行Lite)和內核之間的直接連接

右邊紅字注解:通道允許內核之間的直接連接,而不需要訪問全局內存

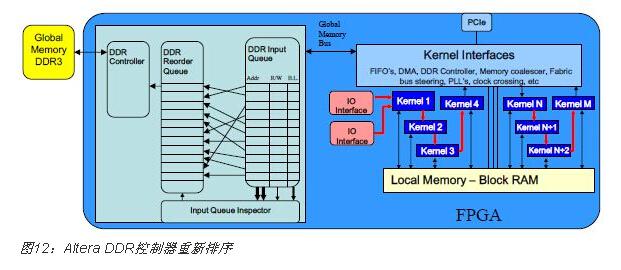

C. 內存訪問合并

DDR內存對于隨機訪問非常低效。它對長脈沖串順序數據效果最好。Altera的OpenCL編譯器提供靜態和動態內存合并。編譯器將嘗試靜態識別OpenCL內核代碼中的多個連續請求,并創建硬件來發出一個寬請求。例如,如果一個整數陣列被連續訪問,則編譯器將創建硬件用一個DDR控制器請求來一次抓取八個整數。此外,Altera的OpenCL內存系統提供動態數據重新排序。DDR輸入隊列按順序接受它們收到的來自不同內核的內存訪問請求。內部數據重新排序模塊,檢查輸入隊列地址和操作類型,然后動態重新排序請求。重新排序請求以優化排序存儲在重新排序緩沖器中。內存控制器器讀取重新排序緩沖器,并以優化形式存儲/檢索數據。圖12示出了有排序緩沖器的高電平DDR控制器。

圖字:

全局內存DDR3;DDR控制器;DDR隊列重新排序;DDR輸入重新排序;全局內存總線PCIe

內核接口

FIFO、DMA、DDR控制器、內存聚結器、結構總線轉向、PLL時鐘交錯,等

IO接口

IO接口

內核1;內核2;內核3;內核4;內核N;內核M;內核N+1;內核N+2

本地內存——RAM塊

FPGA

輸入隊列檢查器

D. 自動循環流水線 - ALP

OpenCL內核通常描述一個單線程的工作,目的在于啟動大量這樣的線程來處理一個數據集。但是,一些問題最好表達為單線程算法。濾波和誤差擴散是兩個這樣的例子。使用多線程進行濾波要么將需要過多的內存讀取,這將在稍后討論,要么需要線程之間過多的通信。由于從當前像素到其鄰近像素的誤差傳播,用在CCP的佛洛伊德-斯坦伯格誤差擴散算法很難并行化。

Altera OpenCL編譯器以單線程算法提供了自動流水線循環。ALP允許以自然方式表達這類算法,并仍然獲得了FPGA加速的全部好處。對于這個項目,濾波和誤差擴散內核都通過編譯器形成了自動流水線,實現了每個時鐘周期一個像素的理想流水線效率。

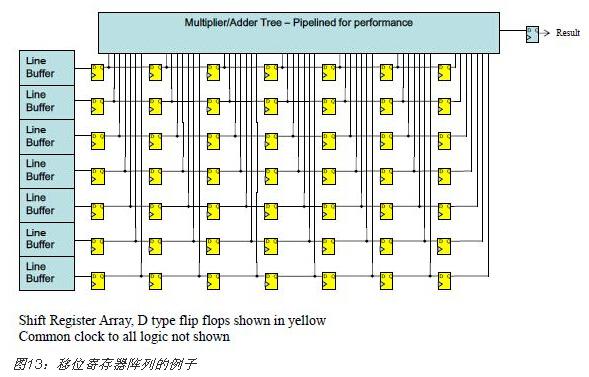

E. 移位寄存器推理

Altera的OpenCL編譯支持所謂移位寄存器推理(SRI)的優化。SRI對于濾波等滑動窗口操作特別有用,通常適用于上述循環流水線功能。從軟件的角度來看,一個滑動窗口操作由一個固定大小陣列(通常比要處理的數據量小得多)和定義在該陣列中固定位置的元素操作組成。此時,要處理的數據被轉換成陣列的一個元素,固定大小陣列的每個值下移一個位置,以容納新的值。每個轉移的數據值出現一個輸出值。圖13示出了用于7×7濾波器的移位寄存器陣列概念。

圖字:

Line Buffer 行緩沖區

乘法器/加法器樹——流水線的性能

結果

以黃色顯示了移位寄存器陣列、D型觸發器

通用時鐘到所有邏輯沒有顯示

7×7濾波器要求來自7條輸入線的7個輸入像素來計算一個輸出像素。一種簡單方法是讀取所有49個像素,計算一個輸出像素,然后重復上述過程,讀取接下來的49個像素等。但是這非常低效,因為你最終會讀取圖像N×M*49次,其中N是圖像寬度,M是圖像長度。

減少內存帶寬的理想解決方案是一次讀取一個圖像像素,并把它們存儲在本地移位寄存器的末端。在每個讀取的像素上,移位寄存器被左移一位,濾波值是通過訪問49個抽頭點(tap point)來計算的。要執行7×7濾波器,移位寄存器必須是6條掃描線加7個像素長。一個新輸出像素計算的是每個輸入像素讀取,除了第6條掃描線讀取。另外,圖像讀取正好一次。不過,FPGA片上存儲器的成本是很高的。對于一個7×7濾波器和寬度為5100像素的掃描線,6條掃描線+7個像素移位寄存器陣列是5100×6+7 = 30,607像素。在每個像素3個字節時,片上RAM塊幾乎是90KB或717Kbits。圖14是編譯器如何實例化一個移位寄存器和行緩沖陣列,減少了全局內存帶寬的框圖:

圖字:

全局內存;DMA讀取通道;7×7濾波器矩陣

乘法器/加法器樹——流水線的性能

Altera OpenCL編譯器可自動識別來自OpenCL內核代碼的移位寄存器設計模式,而無需編譯器提示(如程序)的幫助。你可以簡單斷言用作代碼中移位寄存器的一個固定大小陣列,而AOC將創建所需的硬件。

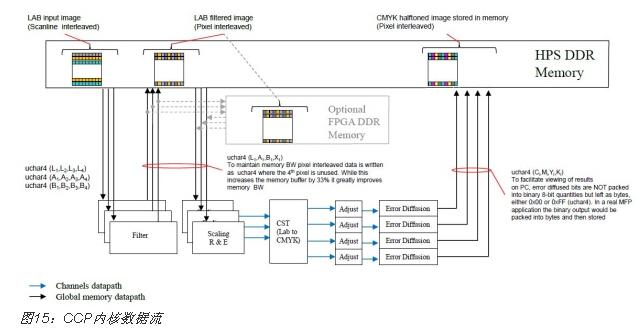

F. CCP數據流

CCP利用了所有Altera OpenCL編譯器的改進,以提供最佳的性能。第一個CCP階段是濾波,在邏輯上實現了3個并聯濾波器操作。每個濾波器處理3個輸入色彩空間(L*、a*和b*)中的一個。7×7濾波器從全局內存提取數據,填補移位寄存器,執行濾波功能,最終結果存回全局內存。存儲在全局內存中的原始輸入數據以隔行掃描線(SI)格式結構化。SI數據被定義為連續存儲的一個彩色平面接著下一個彩色平面的整個掃描線,即N個像素。SI數據是突發讀取全局內存的理想選擇。我們選擇這個格式實現未來的CCP增強,其中的輸入數據將直接來自掃描儀。所有CCP數據均作為uchar4讀取。

CCP縮放算法目前不能進行結構化來接受SI數據。由于縮放內核在濾波器輸出上運行,我們要確保濾波結果以像素隔行格式寫入全局內存。此外,后續內核、CST、調整和ED都需要像素隔行數據。像素隔行數據被定義為一個連續存儲像素的所有四個彩色平面——Ci、Mi、Yi Ki Ci+1、Mi+1、Yi+1 Ki+1。圖15示出了CCP數據流和數據格式。

圖字:

LAB輸入圖像(掃描線交錯);LAB過濾后的圖像(像素交錯);存儲在內存中的CMYK半色調圖像(像素交錯)

EHPS DDR內存

可選FPGA DDR內存

uchar4(L1,A1,B1,X1)

為了保持內存BW像素隔行數據隨uchar4寫入,

第4像素未使用。雖然這增加了33%的內存緩

沖區,仍會大大改善內存BW

BWuchar4(Ci,Mi,Yi,Ki)

為了便于觀看PC上的結果,誤差擴散位沒有被打包成二進制8位量,

而是留作字節,無論是0x00或0xFF(uchar4)。在一臺真正的MFP

應用中,二進制輸出將打包成字節,然后進行存儲

濾波器;縮放R&E;CST(Lab到CMYK);調整;誤差擴散

通道數據通路

全局內存數據通路

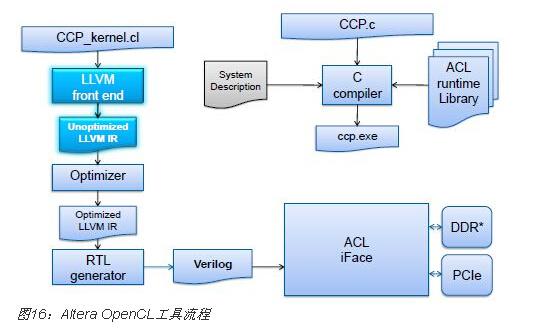

V. OPENCL系統級接口

一旦OpenCL內核代碼被寫入并進行了編譯,它必須加以打包、加載并在參考板上執行。Altera提供了完整的SW架構來實現FPGA的匯編構建、加載和利用[8][9]。Altera OpenCL編譯器采用OpenCL內核,并創建了一個優化的Verilog RTL映射。然后,采用Altera的AOC設計流程來處理Verilog代碼,從而得到FPGA二進制編程文件,名為.sof。與創建FPGA.sof文件并行,一個標準C編譯器(如gcc)用來編譯與OpenCL內核通信的C主機代碼。通信機制是通過一組鏈接到主機可執行文件的Altera OpenCL運行程序庫實現的。圖16示出了創建.sof和.exe文件的Altera OpenCL工具流程[9][10]。

圖字:

LLVM前端;系統描述;C編譯器;AC運行程序庫

未優化LLVM IR

優化程序

優化的LLVM IR

RTL發生器;Verilog

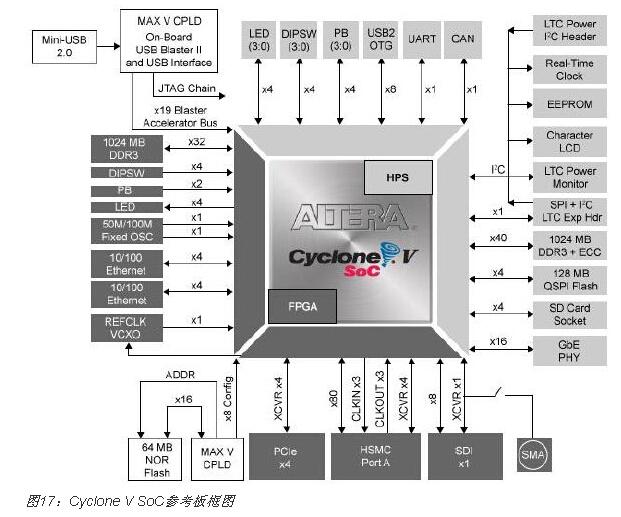

A. Altera參考板

Altera提供與OpenCL兼容的多種解決方案:可作為PCIe子卡的FPGA板和獨立的SoC/FPGA板。我們選擇了Altera Cyclone V SoC FPGA作為開發平臺[11]。OpenCL Cyclone V SoC參考平臺包含以下內容:

● 雙核ARM Cortex A9 - 800MHz

● 1GB的DDR3 HPS,硬處理器系統,內存采用Linux,也可以直接訪問FPGA。它是OpenCL全局內存的首選地點。

● 1GB的DDR31GB只可訪問FPGA。它可用作OpenCL內核的“暫存(scratch pad)”全局內存。

● 千兆以太網與外部PC的通信

● Cyclone V FPGA5CSXFC6D6F31C8N FPGA

圖17是我們的設計和測試中所使用的Altera參考板的框圖[12]:

B. Altera OpenCL接口

OpenCL定義了4個一組的模型:平臺;執行;內存和編程[13]。在平臺模型級別,主機是Cyclone V SoC ARM內核,器件是FPGA架構。在器件內,我們采用了多個計算單元(CU)。

Altera OpenCL將內核模擬為通過其工作項目流動的深度流水線硬件架構。它定義了作為1個計算單元的內核流水線實例。程序員可以選擇指定計算單元內核實例化的數量,以實現空間與吞吐量的權衡。指定較大數量的計算單元可消耗更多的FPGA架構,并在提高有效吞吐量的同時帶來了全局內存爭用和恒定緩存爭用。在CCP例子中,我們采用了5個OpenCL內核,即7×7濾波器、縮放、CST、調整和誤差擴散,每個都同時作為1個計算單元運行。

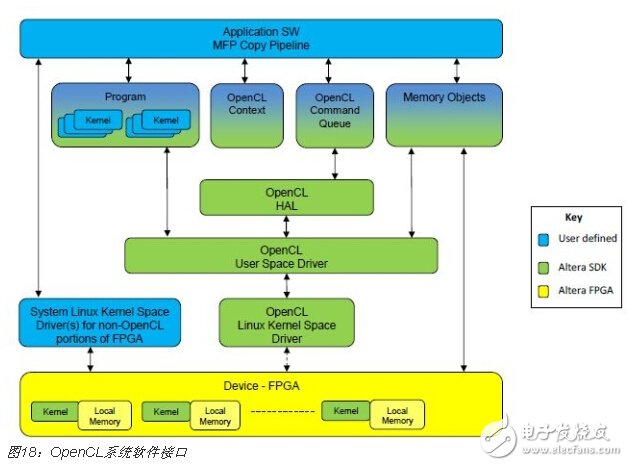

執行模型采用Altera的OpenCL上下文、命令隊列和內存對象。CCP流水線是在一個ARM內核上運行的基于C語言的程序。它管理FPGA加速器架構中的主機程序和CU之間的所有切換。圖18是一個簡化系統軟件接口圖,示出了哪些單元是由用戶提供的,Altera公司又提供了什么。

圖字:

應用SW MFP復印流水線

程序;OpenCL上下文;OpenCL命令隊列;內存對象

內核;內核

OpenCL HAL

OpenCL用戶空間驅動程序

FPGA非OpenCL部分Linux內核空間驅動程序;OpenCLLinux內核空間驅動程序

器件——FPGA

內核;本地內存;內核;本地內存;內核;本地內存

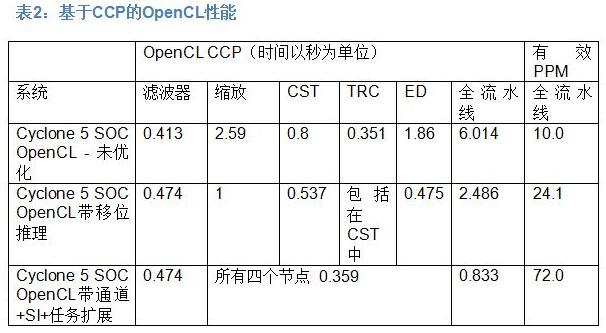

VI. 效果

所有CCP算法都是采用運行在x86 PC的標準C語言開發的。我們創建了一個簡單的基于C語言的CCP流水線來順序執行算法。然后,在x86和Cyclone V SoC ARM Cortex A9 CPU上同時執行基于C語言的流水線。基于C語言的流水線性能和效果是我們的標準參考。

之后,將每個基于C語言的CCP算法移植到OpenCL,并在x86上重新測試內核。然后,使用AOC重新編譯標準OpenCL內核,并在Cyclone V SoC開發平臺上進行測試。最后一步是修改OpenCL內核和包括Altera的通道廠商特定優化。

基于C語言的CCP運行于頻率為3.1GHz的單核i7-3770,以及輸出16.6 PPM的32GB的DDR3內存。同樣基于C語言的CCP在一個Cyclone V SoC Cortex A9內核上執行,運行頻率為800MHz,還有輸出1.4PPM的1GB的DDR3內存。

請注意,在基于C語言的CCP實驗中,我們使用了最高水平的GCC Linux優化——O3選項。不過沒有嘗試使用GPU/NEON協處理器。

在一個CSXFC6D6F31C8N Cyclone V器件上以74MHz運行的標準OpenCL內核輸出10PPM。包括Altera的廠商增強的優化的CCP實現了72PPM。由于Altera的通道最大限度地減少了進/出全局內存的讀取/寫入結果,以及內核中的循環流水線,性能提升了7倍。

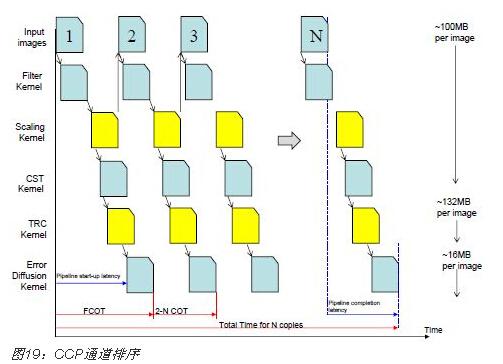

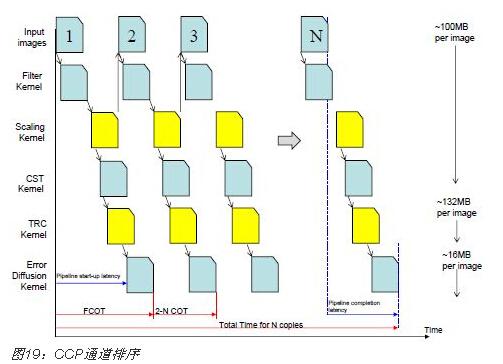

A. CCP多頁性能

利用Altera通道擴展,具體內核執行時間不再是疊加性的。一旦數據進行了處理,并由內核N生成了結果,內核N+1即可開始其處理。這種并行處理使得CCP以最緩慢的內核速度執行,可忽略因流水線充填和排空造成的延遲。圖19 CCP通道排序顯示了這些通道的性能優勢。

由于非順序輸入訪問模式,我們當前的縮放內核實現方法不能接收來自通道的數據。像這樣的濾波器結果必須首先寫入內存,然后可以啟動縮放內核。進一步的通道優化有可能消除中間全局內存存儲/檢索操作。三個通道和每個通道2行緩沖陣列將消除濾波器到定標器(Scaler)全局內存操作。

圖字:

輸入圖像;每幅圖像約100MB

濾波器內核

縮放內核

CST內核

TRC內核;每幅圖像約132MB

誤差擴散內核;每幅圖像約16MB

FCOT;2-N COT;流水線完成延遲

N份總時間;時間

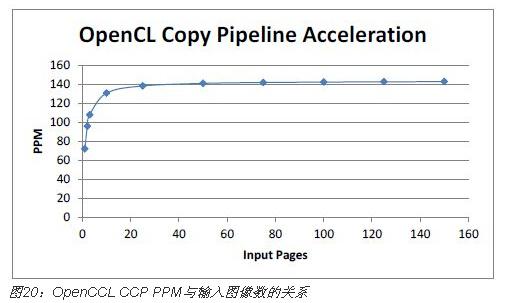

首次復印時間(FCOT)是測量完成第一張圖像處理需要多長時間。2-N-COT是處理第二張和任何后續圖像所需要的時間。在圖19中我們看到,在濾波器和擴展內核處理完第一張圖像后,它們可以立即開始處理第二張圖像。隨著處理的圖像數目增加,CCP啟動延遲和空延遲可以分攤到圖像總數N。

圖字:

OpenCL復印流水線加速

輸入頁數

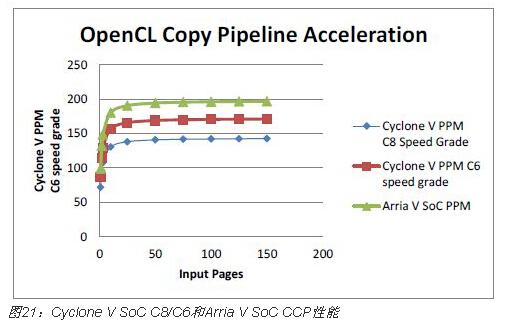

在C8速度等級測量的OpenCL CCP性能是最低成本/最低性能的Cyclone V系列。圖20示出了作為輸入頁面數量函數的基準CCP性能。Cyclone V C6速度等級最快,會增加20%的性能。

相比Cyclone V C6,Altera的Arria V SoC系列FPGA預計將提高15%的性能。圖21顯示了三個速度等級的實際和預期性能。

圖字:

OpenCL復印流水線加速

Cyclone V PPM C6速度等級 Cyclone V PPM C8速度等級

Cyclone V PPM C6速度等級

Arria V SoC PPM

輸入頁數

B. 器件利用率

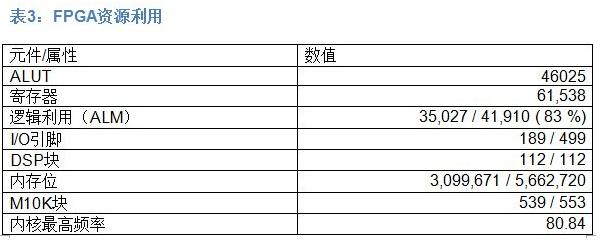

與所有Altera的擴展一起優化的CCP消耗83%的5CSXFC6D6F31C8N邏輯資源。崩潰(breakdown)總結于表3中。

VII. 擴展和增強

A. 擴展CCP到整個系統

下一步驟是采用CCP并將其連接到數據輸入的掃描裝置和數據輸出的打印裝置。這將需要增加一個校準內核和簡單的CST將RGB轉換為L*a*b*。根據在掃描設備中使用的傳感器陣列類型,即電荷耦合器件或接觸式圖像傳感器,紅、綠和藍行數據可能無法在垂直方向對準。行數據的對準可能需要幾十行緩沖區,這在FPGA內存資源方面是非常昂貴的。為了緩解這一問題,原始RGB數據將使用DMA暫時保存在HPS內存中。然后,紅、綠、藍、行數據的對準可以使用DMA指針和偏移來完成。然后校準對準的RGB數據,并通過通道傳遞到基本CST內核。

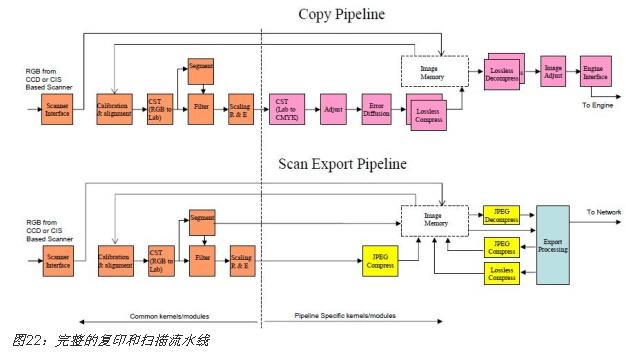

基本CST內核將依次使用通道直接將數據傳遞到濾波器輸入模塊。我們的期望是,這些額外內核將適合未使用的邏輯和內存資源。圖22顯示了完整的復印流水線。請注意,除了有全掃描儀接口的CCP,分割、無損壓縮模塊和引擎級都不適合Cyclone V SoC器件。完整的圖像路徑將需要更大型的FPGA。

B. ARM內核和NEON協處理

除了FPGA架構和OpenCL,Altera SoC系列器件還采用了雙核ARM Cortex A9內核和NEON協處理器。圖像處理流水線的某些模塊可以卸載到CPU。在分割操作和完成壓縮/解壓縮功能的特定部分可以使用NEON提供的有SIMD加速的CPU來完成。

C. 動態FPGA可重編程性

Altera SoC FPGA提供的動態重新配置允許用戶重新編程FPGA架構,同時CPU運算繼續運行。這個特點在MFP中特別有用,而其中的一些操作永遠不可能同時發生。例如,掃描和復印操作共享6個共同輸入功能,如圖22所示。其余的復印操作、CST壓縮,以及剩下的掃描輸入功能、JPEG壓縮將永遠不會同時運行。因此,我們可以創建兩套內核,其中包括共同的掃描儀功能和多種后端功能。這些流水線可以在給定所需時間基于MFP操作來動態加載。在一個傳統ASIC中,這些模塊和數據通路都必須包括在內。動態圖像路徑的重新配置可以實現更小的FPGA,從而實現更低成本的圖像路徑。

D. Arria V和Arria 10 SoC

Altera的Arria V和最近發布的Arria10 SoC為功能齊全的MFP圖像路徑解決方案提供了一個可擴展平臺。增加的內存、更快的時鐘速度,加上更高性能ARM內核的大型FPGA架構為圖像處理和一般計算要求提供了完整解決方案。

圖字:

復印流水線

來自CCD或基于CIS掃描儀的RGB;分割;圖像內存;無損解壓縮;圖像調整;引擎接口

掃描儀接口;校準和調整;CST(RGB到Lab);濾波器;縮放R & E;CST(Lab到CMYK);調整;誤差擴散;無損壓縮;至引擎

掃描出口流水線

來自CCD或基于CIS掃描儀的RGB;分割;圖像內存;JGEG解壓縮;至網絡

掃描儀接口;校準和調整;CST(RGB到Lab);濾波器;縮放R & E;JGEG壓縮;JGEG壓縮;出口處理;無損壓縮

通用內核/模塊;流水線特定內核/模塊

VIII. 總結和結論

OpenCL和Altera的工具鏈有助于2名全職OpenCL軟件工程師、1名全職硬件工程師和其他兼職人員的一個小型團隊在約4.5個月內實現CCP。團隊可從C語言算法開始,創建一個高水平的基于C語言的CCP圖像流水線,將算法移植到OpenCL,在x86平臺上測試OpenCL以驗證基本功能,增加廠商特定擴展,學會Altera OpenCL工具流程,最后在Altera的參考平臺上測試結果。團隊還可開發一個測試環境來驗證位級別OpenCL結果的正確性。此外,團隊可創建一個基于Web的應用,允許用戶選擇源圖像,通過一個基于C語言的CCP和OpenCL加速的CCP運行圖像,顯示半色調圖像,并提供計時結果。軟件工程師可以沒有以往的FPGA經驗,硬件工程師也可以沒有以往的OpenCL經驗。

這種新模式演示了一個小型團隊如何可以快速從一組算法到全面功能,優化以硬件實現的流水線。大約50%的開發時間專注于優化,包括最大限度地提高性能和最大限度地減少FPGA資源利用。該團隊預計,后續項目開發時間可減少50%。

MFP廠商不再需要投入數百萬美元和多年時間來開發ASIC或SoC。OpenCL和Altera SoC器件提供了一種在最短時間內實現高性能、低成本MFP控制器的新模式。

-

傳感器

+關注

關注

2563文章

52575瀏覽量

763739 -

FPGA

+關注

關注

1643文章

21964瀏覽量

614114 -

usb

+關注

關注

60文章

8143瀏覽量

270846

發布評論請先 登錄

利用FPGA器件加速OpenCL在MFP圖像處理中的應用

利用FPGA器件加速OpenCL在MFP圖像處理中的應用

評論