數據采集是工業測量和控制系統中的重要部分。它是測控現場的模擬信號源與上位機之間的接口,其任務是采集現場連續變化的被測信號。系統應將所采集的模擬數據信號盡可能真實、不失真地顯示給控制人員。

隨著計算機技術和EDA技術的發展,由于復雜可編程邏輯器件(CPLD)具有高集成度、小體積、低成本、低功耗以及高穩定性等諸多優點而廣泛使用到諸如傳統工業控制等各個領域。基于ISA的接口電路,其布線要求遠沒有PCI或USB接口板高。由于它能夠提供16位I/O操作,對I/O的直接讀寫可以完全不考慮復雜的驅動程序和應用程序,因而在ISA總線上開發接口電路目前仍是首先考慮的方法。因此,這里提出一種基于CPLD和ISA總線的數據采集系統設計。

1 系統硬件設計

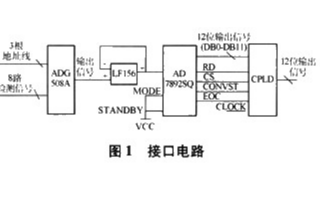

數據采集系統的硬件電路主要包括:CPLD邏輯控制電路、8254定時器電路、A/D轉換電路。該系統硬件設計框圖如圖1所示。

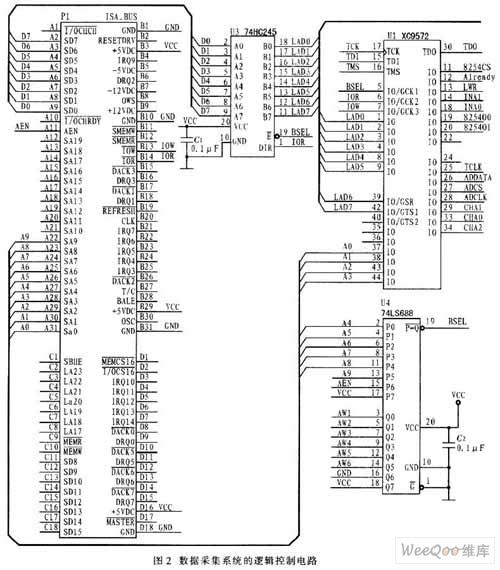

1.1 CPLD邏輯控制電路

該系統使用XC9572作為主控器件。XC9572是一款高性能可編程邏輯器件,內含4個36 v 18功能模塊,具有l 600個可用系統門。ISA總線上的地址、控制指令和數據被送進CPLD,經處理后送到相應電路中。由A/D轉換電路得到的數據也返回到CPLD進行處理,并經ISA總線送至計算機中。

圖2為數據采集系統的邏輯控制電路,Ul是數據緩沖器74HC245,由lSA總線的讀/寫信號(IOR/IOW)和板卡選擇信號(BSEL)決定數據的流向。比較器74LS688和XFl組成板卡選擇信號發生電路。通過在XFl上的跳線可確定采集系統板的基地址。該系統基地址設置為280H。

ISA總線上的讀寫信號,經緩沖器的數據信號(LADO~LAD7),地址信號(A0~A3)均與XC29572相連,CPLD發送A/D轉換器的片選信號(ADCS)、A/D時鐘信號(ADCLK)以及通道選擇信號(CHA0~CHA2)。

1.2 8254可編程定時器電路

8254可編程定時器內部具有3個獨立的16位減法計數器,它可由程序設置成多種工作方式,有6種可選工作方式。計數器按照設置各工作方式寄存器中控制字工作,按十進制計數或二進制計數,最高計數速率可達10 MHz。

該數據采集系統需要由8254提供AD轉換電路的時鐘信號和片選信號,通過改變8254的控制字改變數據采集系統的轉換頻率。8254定時器的輸入時鐘由外部晶振提供。定時器和定時器的輸出信號直接送入可編程邏輯器件XC9572,經處理后提A/D轉換電路使用。上位機寫入的控制字經ISA總線送至8254,同時XC9572給8254提供必要的控制信號,如:8254讀/寫信號、片選信號、地址信號等。

假設系統的外部時鐘為2 MHz,如果需要8254的定時器0輸出一個頻率為l MHz,占空比為50%的時鐘,則8254的定時器控制字可設置為:D7~D0=00110110,其中,D7D6=00,表示選擇定時器;D5D4=11,表示先讀/寫低8位,后讀/寫高8位數據;D3D2Dl=011,表示工作方式3,方波發生器;D0=0,表示二進制計數。

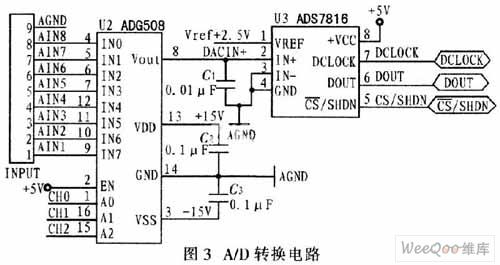

1.3 A/D轉換電路

A/D轉換電路完成數據采集和轉換,主要包括MD轉換和模擬信號采樣兩部分電路。

8通道模擬采樣開關ADG508用于采樣模擬信號。由CPLD送來的通道選擇信號(CH0~CH2)用于選擇輸入的通道號。被選通的通道采樣得到的模擬信號送給ADS7816的IN+端,進行AD轉換,如圖3所示。

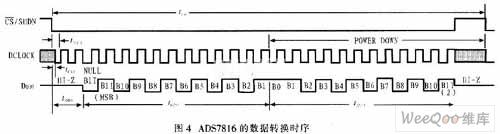

A/D轉換電路采用TI公司的ADS7816,該器件是12位串行A/D轉換器,采樣頻率高達200 kHz,轉換所需時間短,轉換精度高,輸出形式為位串行,因此在對ADS7816進行讀數據操作時需注意數據轉換過程中的時序。

圖4是ADS7816的數據轉換時序。當ADS7816的片選端下降沿到來時,開始啟動一次A/D轉換,保持轉換時鐘輸入和片選信號低電平,最初的1.5~2個時鐘時間里,完成模擬信號的采樣,這段時間ADS7816的輸出呈高阻狀態(HI-Z)。緊接著的1個時鐘周期里,DOUT輸出1個空位(NULL BIT)。隨后,ADS7816在12個連續的時鐘周期內把12位的A/D轉換結果輸出,其中先輸出最高位(MSB),最后輸出最低位(LSB)。如果12位數據送出后仍有轉換時鐘且ADS7816的片選仍保持低電平,那么轉換器會從最低位起逐位重復輸出之前轉換的結果。當下一個片選信號的下降沿到來時,A/D轉換器開始啟動下一次A/D轉換。

2 系統軟件設計

系統軟件設計包括基于VHDL的邏輯控制程序設計和基于C語言的上位機采集測試程序設計。

2.1 VHDL程序設計

系統設計硬件中,可編程邏輯器件完成的內容有:接收上位機的地址和數據,為模擬開關提供通道選擇信號,為A/D轉換電路提供時鐘信號和片選信號,接收ADS7816轉換的數據,向上位機傳送轉換結果。

從圖4中可得到ADS7816在片選信號下降沿到來后的14.5~15個時鐘周期里,完成一次轉換并逐位輸出12位轉換結果。為了能夠得到完整的正確的A/D轉換結果,采用計數方式設置標志位FLG。在ADS7816的片選信號為低電平的前15個時鐘周期中,即“計數器計數值≤14”時,FLG=l,表示A/D轉換正在進行;當“計數器的計數值>14”,則FLG=0,表示A/D轉換結束。當FLG=0時,程序可讀取一次正確的A/D轉換數據。

因為ADS7816的數據轉換結果是串行輸入到CPLD中,需在CPLD中將得到的數據進行串并轉換后再通過ISA總線的8位數據線分2次送出。

系統進行數據轉換前需先選擇輸入通道,確定采集哪一路信號。上位機輸入的通道號經CPLD送至8路模擬采樣開關。

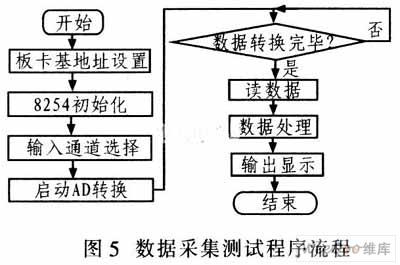

2.2 數據采集測試程序設計

上位機的數據采集測試程序采用C語言設計。因為系統采用ISA接口,所以功能測試無需編寫復雜的應用程序,只需在Win98操作系統里編寫C語言的測試程序即可實現系統的數據采集功能。上位機的數據采集測試程序主要完成:采集系統的硬件初始化、通道選擇、數據采集、數據處理和數據輸出。其程序設計流程如圖5所示。

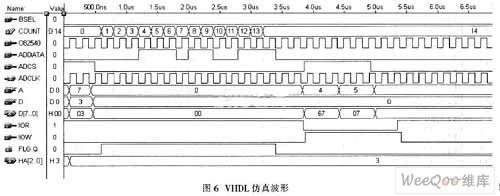

3 仿真和實驗結果

圖6所示為寫入XC9572的VHDL程序的仿真波形,主要是CPLD控制A/D轉換的功能仿真。從仿真波形圖中可以看出,當地址A為7時,寫入通道號3,得到的輸入通道選通信號為3,實現通過上位機選擇輸入通道功能。當ADCS的下降沿到來后開始啟動A/D轉換;ADCS下降沿起的第3個時鐘對應的ADDATA為系統轉換的第1個數據,直到這次轉換完畢。由給定的ADDATA數據得知,串行輸入的數據是767H(011l O110 0111B)。仿真結果中,地址為4時,數據的低8位結果為67H;地址為5時,數據的高8位結果為07H,仿真結果完全正確。

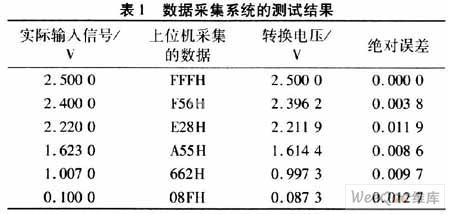

在Windows98下,使用基于C語言的數據采集測試程序,可得到如表l所示的測試數據。從所列數據看出,該數據采集系統采集數據正確,且精度高。

4 結論

基于CPLD的數據采集系統具有硬件線路簡單、精度高、采集速度快的特點。ISA總線和CPLD結合的數據采集系統有其獨特的優勢。該數據采集系統可循環采樣多路(8路)模擬信號采樣。實際測試結果表明該設計方案可行,且具有很高的實用價值。

-

cpld

+關注

關注

32文章

1257瀏覽量

171515 -

計算機

+關注

關注

19文章

7663瀏覽量

90805 -

數據采集

+關注

關注

40文章

7181瀏覽量

116510 -

定時器

+關注

關注

23文章

3298瀏覽量

118947

發布評論請先 登錄

基于復雜可編程邏輯器件(CPLD)的120MHZ高速A/D采集卡的設計

如何采用可編程邏輯器件和A/D轉換器組成高速數據采集卡?

PLD可編程邏輯器件

基于復雜可編程邏輯器件(CPLD)的120MHZ高速AD采集

可編程邏輯器件基礎及應用實驗指導書

基于單片機的復雜可編程邏輯器件快速配置方法

什么是PLD(可編程邏輯器件)

采用復雜可編程邏輯器件實現多路信號采集系統的設計

采用復雜可編程邏輯器件與ISA總線相結合實現數據采集系統設計

采用復雜可編程邏輯器件與ISA總線相結合實現數據采集系統設計

評論