數(shù)據(jù)采集系統(tǒng)是數(shù)字存儲(chǔ)示波器的核心部分,在示波器采集控制電路的控制下,數(shù)據(jù)采集系統(tǒng)將待測(cè)的模擬信號(hào)量化后進(jìn)行緩存,供示波器軟件系統(tǒng)進(jìn)行數(shù)據(jù)的處理、運(yùn)算、顯示。隨著計(jì)算機(jī)技術(shù)的不斷發(fā)展,高速ADC的性能不斷提高,功能強(qiáng)大的DSP信號(hào)處理的實(shí)時(shí)性越來(lái)越強(qiáng),可編程的邏輯器件的性能不斷提升,為示波器數(shù)據(jù)采集系統(tǒng)的實(shí)現(xiàn)提供了一個(gè)可靠而且實(shí)用的數(shù)字平臺(tái)。相應(yīng)的,數(shù)據(jù)采集系統(tǒng)的采樣速率、存儲(chǔ)深度、波形捕獲能力、鑒別能力等指標(biāo)也在不斷提高。國(guó)際上,示波器行業(yè)像安捷倫、泰克等公司在數(shù)字存儲(chǔ)示波器市場(chǎng)上占據(jù)了主導(dǎo)地位,均有實(shí)時(shí)采樣率達(dá)到幾十Gsps的示波器面市,但是由于受到器件和工藝的限制,國(guó)內(nèi)實(shí)現(xiàn)真正的高速高分辨率的數(shù)據(jù)采集系統(tǒng)還具有比較大的困難。

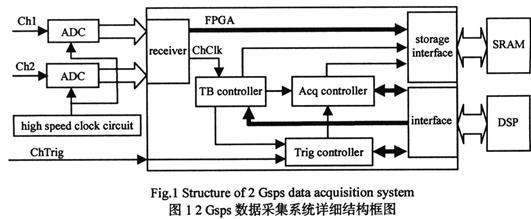

本文采用ADC+高頻時(shí)鐘電路+FPGA+DSP的結(jié)構(gòu)模式,設(shè)計(jì)了一種實(shí)時(shí)采樣率為2 Gsps的數(shù)字存儲(chǔ)示波器數(shù)據(jù)采集系統(tǒng),為國(guó)內(nèi)高速高分辨率的數(shù)據(jù)采集系統(tǒng)的研制提供了一個(gè)參考方案。

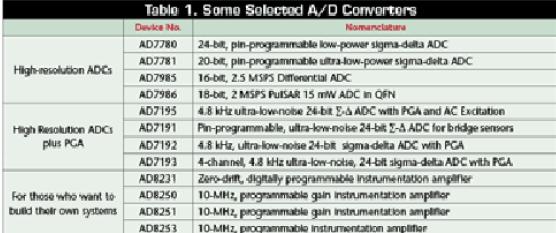

1 關(guān)鍵器件選擇

DSO數(shù)據(jù)采集系統(tǒng)的主要技術(shù)指標(biāo):a)雙輸入通道同時(shí)工作,每通道最高實(shí)時(shí)采樣率達(dá)到2 Gsps;b)垂直分辨率8 bit;c)存儲(chǔ)深度:8 MB/CH。整個(gè)系統(tǒng)的關(guān)鍵器件包括ADC、高頻時(shí)鐘芯片、FPGA、DSP、SRAM。通過(guò)對(duì)目標(biāo)系統(tǒng)主要技術(shù)指標(biāo)的分析,結(jié)合數(shù)字存儲(chǔ)示波器的應(yīng)用特性,選擇了以下一系列器件。

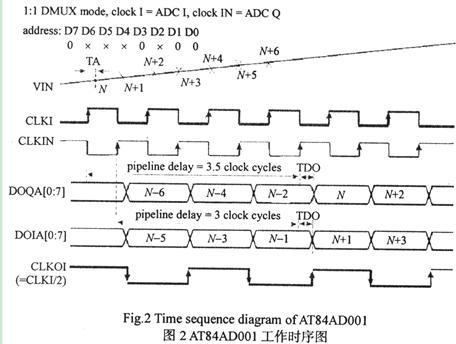

數(shù)據(jù)采集系統(tǒng)要求達(dá)到的最高實(shí)時(shí)采樣率為2 Gsps,同時(shí)考慮目標(biāo)系統(tǒng)所要求的垂直分辨率、數(shù)據(jù)輸出格式,另外兼顧示波器的模擬帶寬以及器件的購(gòu)買渠道和性價(jià)比,選擇了Atmel公司的AT84AD001。AT84AD001是雙通道ADC,每一通道具有1 Gsps的實(shí)時(shí)采樣率,在交錯(cuò)模式下雙路ADC并行采樣可以達(dá)到2 Gsps的實(shí)時(shí)采樣率。其分辨率為8 bit,數(shù)據(jù)輸出格式是LVDS(Low Voltage Differential Signaling),具有1:1數(shù)據(jù)輸出或1:2數(shù)據(jù)輸出模式可選,此外,全功率輸人帶寬(-3 dB)為1.5 GHz,差分電壓輸入范圍為500 mVVpp。

此外,重要的一點(diǎn),AT84AD001還具有FISDA(Fine Sampling Delay Adjustment on Channel Q)功能,通過(guò)調(diào)整Q通道的采樣時(shí)刻,有效地避免了因?yàn)椴蓸訒r(shí)鐘的占空比不等于50%而造成的誤差,保證了采樣精度。

高速高精度的ADC對(duì)采樣時(shí)鐘的精度要求非常高,時(shí)鐘電路一般的設(shè)計(jì)方法是直接利用FPGA內(nèi)部的鎖相環(huán)倍頻電路產(chǎn)生,但是目標(biāo)系統(tǒng)要求采樣時(shí)鐘頻率達(dá)到1 GHz,而目前Altera和Xilinx公司的高端FPGA其I/O輸出頻率最高只能達(dá)到800MHz。經(jīng)過(guò)綜合評(píng)價(jià),最終選定了美國(guó)NS公司的高頻時(shí)鐘芯片LMX2531LQ1910E。其輸出低段頻率為917 MHz~1 014 MHz,滿足設(shè)計(jì)要求,此外,LMX2531具有非常低的抖動(dòng)和相位噪聲。而且還集成了低噪聲、高性能的低壓差線性穩(wěn)壓器LDO(Low Drop Out regulator)元件,使電路的抗干擾性和穩(wěn)定性得到了提高。

FPGA的可編程性以及豐富的內(nèi)部邏輯資源和外部I/O資源,用來(lái)作為數(shù)字存儲(chǔ)示波器數(shù)據(jù)采集與控制系統(tǒng)。特別地,單片AT84AD001量化輸出是16路1 Gbps速率、LVDS格式的差分?jǐn)?shù)據(jù),目標(biāo)系統(tǒng)雙輸入通道同時(shí)工作,這就要求FPGA具有32個(gè)能支持1 Gbps的差分I/O,利用高速I/O將數(shù)據(jù)接收并存儲(chǔ)。由此,選擇了Altera公司的Stratix II EP2S60F1020C4,該FPGA最多可以支持多達(dá)84個(gè)1 Gbps的差分通道,并且增加了源同步通道的動(dòng)態(tài)相位對(duì)準(zhǔn)電路,為高速數(shù)據(jù)的接受提供了有力的支持。

在示波器的高速數(shù)據(jù)采集系統(tǒng)中,需要對(duì)采集到的數(shù)據(jù)進(jìn)行大量實(shí)時(shí)性的運(yùn)算和處理,綜合考慮市面上的各款處理器,選擇ADI公司的DSP芯片Blackfin561作為嵌入式計(jì)算系統(tǒng)。Blackfin561主頻最高可達(dá)750 MHz,其內(nèi)核包含2個(gè)16位乘加器MAC(Multiplier and Accumulator)、2個(gè)40位累加器ALU、1個(gè)40位移位器、100KB的片內(nèi)L1存儲(chǔ)器以及128 KB的片內(nèi)L2存儲(chǔ)器SRAM,同時(shí)具有動(dòng)態(tài)電源管理功能。此外,Blackfin處理器還包括豐富的外設(shè)接口,滿足設(shè)計(jì)的需要。

本文設(shè)計(jì)的數(shù)字存儲(chǔ)示波器的存儲(chǔ)深度要求達(dá)到每通道8 MB,而FPGA芯片Stratix II EP2S60F1020C4的片內(nèi)存儲(chǔ)單元總共只有552 KB,所以,必須采用片外存儲(chǔ)器作為采集RAM來(lái)存儲(chǔ)量化后的波形數(shù)據(jù),經(jīng)過(guò)綜合考慮,選用美國(guó)賽普拉斯公司的SRAM芯片CY7C1440AV33。

2 系統(tǒng)結(jié)構(gòu)

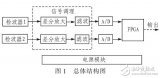

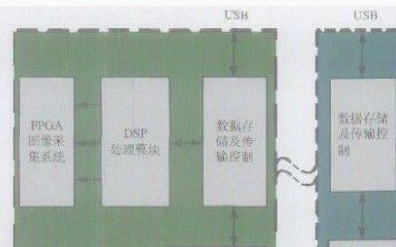

本文設(shè)計(jì)的數(shù)據(jù)采集系統(tǒng)采用ADC+高速時(shí)鐘電路+FPGA+SRAM+DSP的結(jié)構(gòu)模式,其系統(tǒng)結(jié)構(gòu)如圖1所示。通道1、通道2均采用一片最高實(shí)時(shí)采樣率為2 Gsps的AT84AD001作為模數(shù)轉(zhuǎn)換器完成對(duì)模擬輸入信號(hào)的量化,高頻時(shí)鐘電路用來(lái)產(chǎn)生整個(gè)數(shù)據(jù)采集系統(tǒng)所需要的工作時(shí)鐘,F(xiàn)PGA用來(lái)完成采樣數(shù)據(jù)的接收,并且實(shí)現(xiàn)FPGA與DSP的接口電路;SRAM作為數(shù)據(jù)采集系統(tǒng)的采集RAM,完成將量化后的波形數(shù)據(jù)緩存;DSP作為數(shù)據(jù)采集系統(tǒng)的主控機(jī),完成對(duì)采集電路的控制和接收采集電路采集的數(shù)據(jù),并對(duì)采樣數(shù)據(jù)進(jìn)行處理、分析和顯示。

3 硬件設(shè)計(jì)

3.1 目標(biāo)系統(tǒng)高速時(shí)鐘電路的設(shè)計(jì)

通過(guò)LMX2531的標(biāo)準(zhǔn)的三線串行接口(CLK,DATA,LE)對(duì)其編程,以控制LMX2531能夠輸出期望的頻率。時(shí)鐘輸出頻率大小的計(jì)算公式為:

fout=N×(OSCin/R) (1)

其中,N=Ninteger+Nfractional(包括整數(shù)和小數(shù)兩部分),Ninteger的值即為Ⅳ分頻器的值,Nfractional的值包括NUM和DEN兩部分的值,R代表R分頻器的值,OSCin為參考時(shí)鐘輸入值。R分頻器的值可以由用戶在1,2,4,8,16,32中任選一個(gè),而且參考時(shí)鐘輸入OSCin和輸出頻率fout也是用戶自己決定的。根據(jù)設(shè)計(jì)要求,確定各個(gè)寄存器的具體取值,將計(jì)算好的數(shù)據(jù)寫入芯片內(nèi)的11個(gè)24位控制寄存器,從而得到ADC需要的1 GHz的時(shí)鐘。

3.2 AT84AD001工作模式的設(shè)置

AT84AD001的工作時(shí)序如圖2所示。I,Q通道ADC都使用I通道輸入模擬信號(hào),I通道工作時(shí)鐘頻率為1 GHz,Q通道的工作時(shí)鐘與I通道工作時(shí)鐘同頻反相,在這種模式下,通過(guò)兩個(gè)實(shí)時(shí)采樣率為1 Gsps的ADC按照交替方式并行采樣,將得到的數(shù)據(jù)按照一定的輸出格式拼合成2 Gsps的數(shù)據(jù)流。

3.3 FPGA內(nèi)部邏輯模塊介紹

FPGA內(nèi)部邏輯模塊主要包括:

1)時(shí)基電路模塊:接收AT84AD001的輸出數(shù)據(jù)同步鎖存時(shí)鐘作為FPGA內(nèi)部的工作時(shí)鐘,并且為數(shù)據(jù)采集系統(tǒng)提供時(shí)間基準(zhǔn)尺度。

2)數(shù)據(jù)采集接口、存儲(chǔ)接口模塊:利用

FPGA的串行收發(fā)器SERDES(Serializer/Deserializer)和動(dòng)態(tài)相位對(duì)準(zhǔn)DPA(Dynamic Phase Alignment)電路接收LVDS格式、1 Gbps速率的差分?jǐn)?shù)據(jù)流,并且對(duì)其降頻,然后根據(jù)差分通道和ADC數(shù)據(jù)位的對(duì)應(yīng)順序以及接收器數(shù)據(jù)的輸出格式,設(shè)計(jì)恢復(fù)電路,將64位的數(shù)據(jù)按采樣點(diǎn)的格式恢復(fù)為8個(gè)采樣點(diǎn),最后在FPGA與片外存儲(chǔ)器之間建立數(shù)據(jù)存儲(chǔ)接口,將數(shù)據(jù)按照一定的速率和格式寫入片外存儲(chǔ)器。

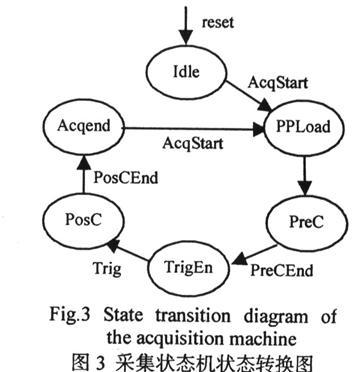

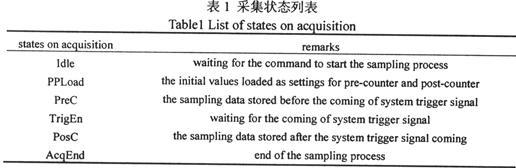

3)采集控制模塊:利用采集狀態(tài)機(jī),配合軟件系統(tǒng)完成對(duì)整個(gè)采集過(guò)程進(jìn)行管理,按照設(shè)定的預(yù)觸發(fā)和后觸發(fā)數(shù)據(jù)量完成成整個(gè)采集工程。

4)觸發(fā)控制模塊:用來(lái)實(shí)現(xiàn)信號(hào)特征點(diǎn)的捕捉及波形顯示的同步。

5)計(jì)算系統(tǒng)接口模塊:完成FPGA和DSP之間的通信。

其中,采集狀態(tài)機(jī)作為采集控制模塊的核心,負(fù)責(zé)整個(gè)數(shù)據(jù)采集過(guò)程的控制,具有舉足輕重的地位。它是一個(gè)用VHDL語(yǔ)言編制的狀態(tài)機(jī),其狀態(tài)轉(zhuǎn)換如圖3所示。圖3中狀態(tài)轉(zhuǎn)換所涉及的采集狀態(tài)說(shuō)明如表1所示。

4 數(shù)據(jù)采集系統(tǒng)監(jiān)控軟件設(shè)計(jì)

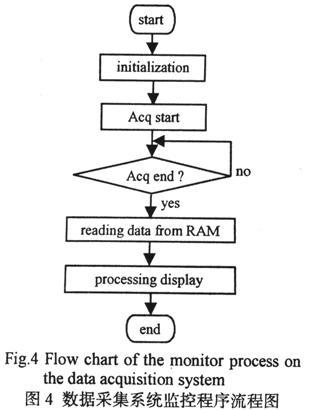

為了便于測(cè)試整個(gè)硬件的工作,在DSP中編制了簡(jiǎn)單的監(jiān)控程序,程序流程圖如圖4所示。首先,DSP調(diào)用時(shí)鐘芯片和ADC的初始化程序,完成對(duì)高速時(shí)鐘電路和采集電路的初始化,使其工作在目標(biāo)系統(tǒng)所需要的工作模式下;然后發(fā)出采集開(kāi)始命令,數(shù)據(jù)采集系統(tǒng)進(jìn)入采集過(guò)程;延遲一段時(shí)間以后,查詢采集結(jié)束標(biāo)志;當(dāng)?shù)弥杉^(guò)程結(jié)束時(shí),便從RAM中讀取波形數(shù)據(jù),經(jīng)過(guò)分析處理后送去顯示。

5 調(diào)試結(jié)果

5.1 實(shí)時(shí)采樣率的分析

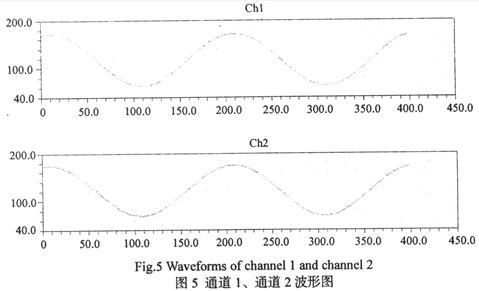

均是10 MHz,150 mvVpp正弦波,在軟件開(kāi)發(fā)環(huán)境Visual DSP++中運(yùn)行數(shù)據(jù)采集系統(tǒng)監(jiān)控程序,得到通道1和通道2的采樣數(shù)據(jù),利用VDSP中的調(diào)試工具分別以通道1和通道2的采樣數(shù)據(jù)作為數(shù)據(jù)源,經(jīng)過(guò)通道校準(zhǔn),調(diào)整每一通道的模數(shù)轉(zhuǎn)換器所包含的雙通道ADC之間的偏移和模擬信號(hào)增益存在的差別。選取任意400個(gè)采樣點(diǎn)以折線圖的形式恢復(fù)出采樣波形,如圖5所示。

從采到的波形數(shù)據(jù)提取連續(xù)400個(gè)采樣點(diǎn)恢復(fù)出波形,正好顯示了兩個(gè)信號(hào)周期,另外恢復(fù)出的波形的幅度與信源幅度相符合,可以得知通道1、通道2均實(shí)現(xiàn)了2 Gsps的實(shí)時(shí)采樣率。

5.2 有效位數(shù)(ENOB)的分析

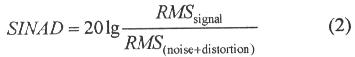

有效位數(shù)(ENOB)是衡量數(shù)據(jù)采集系統(tǒng)動(dòng)態(tài)特性的一個(gè)最為重要的指標(biāo)。計(jì)算公式為:ENOB=(SINAD-1.16 dB)/6.02 。 SINAD是信號(hào)幅度的均方根值與從直流到fs/2的帶寬內(nèi)所有其他頻譜成分的均方根值的比值(包括諧波但不包括直流成分)。其計(jì)算公式為:

通道1、通道2的輸入信號(hào)均是10 MHz,330 mVVpp的正弦波,在VDSP中運(yùn)行數(shù)據(jù)采集系統(tǒng)監(jiān)控程序,得到通道1和通道2的采樣數(shù)據(jù),從每個(gè)通道的采樣數(shù)據(jù)中各取任意連續(xù)1 024個(gè)采樣點(diǎn)作為測(cè)試數(shù)據(jù),利用Matlab編程,計(jì)算其有效位數(shù)(ENOB)分別是:6.71(通道1),6.77(通道2)。由以上計(jì)算結(jié)果得知該數(shù)據(jù)采集系統(tǒng)具有較高的量化分辨率。

6 結(jié)論

通過(guò)實(shí)驗(yàn)板硬件調(diào)試與軟件仿真,設(shè)計(jì)了雙通道同時(shí)工作,每通道最高實(shí)時(shí)采樣率為2 Gsps,分辨力為8 bit,存儲(chǔ)深度8 MB/CH的數(shù)字示波器數(shù)據(jù)采集系統(tǒng),并且驗(yàn)證了實(shí)驗(yàn)板上的數(shù)據(jù)傳輸和數(shù)據(jù)存儲(chǔ)均能滿足2 Gsps數(shù)據(jù)采集系統(tǒng)的要求。

-

dsp

+關(guān)注

關(guān)注

556文章

8157瀏覽量

357419 -

FPGA

+關(guān)注

關(guān)注

1645文章

22046瀏覽量

618277 -

adc

+關(guān)注

關(guān)注

99文章

6705瀏覽量

549176

發(fā)布評(píng)論請(qǐng)先 登錄

高分辨率精密ADC的雜散產(chǎn)生原因是什么?

EVAL-AD7716EBZ,高分辨率ADC非常適用于生物醫(yī)學(xué)數(shù)據(jù)采集系統(tǒng)

如何利用單片機(jī)內(nèi)置ADC實(shí)現(xiàn)高分辨率采樣

ADC信噪比要怎么分析?高速高分辨率ADC電路要怎么實(shí)現(xiàn)?

如何設(shè)計(jì)高速高分辨率ADC電路?

單片機(jī)內(nèi)置ADC實(shí)現(xiàn)高分辨率采樣的方法

基于FPGA+PowerPC的高分辨率圖像實(shí)時(shí)壓縮系統(tǒng)的設(shè)計(jì)

高分辨率模數(shù)轉(zhuǎn)換器(ADC)概述

垂直分辨率與使用高分辨率示波器測(cè)量微小信號(hào)的介紹

基于高分辨率模數(shù)轉(zhuǎn)換器的振動(dòng)信號(hào)采集系統(tǒng)設(shè)計(jì)

高分辨率ADC的板布線分析

驅(qū)動(dòng)高分辨率 SAR ADC

基于FPGA的高分辨率高刷新率圖像采集系統(tǒng)設(shè)計(jì)

太秀了!單片機(jī)內(nèi)置ADC實(shí)現(xiàn)高分辨率采樣?

采用ADC+時(shí)鐘電路+FPGA+DSP實(shí)現(xiàn)高分辨率的數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

采用ADC+時(shí)鐘電路+FPGA+DSP實(shí)現(xiàn)高分辨率的數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

評(píng)論