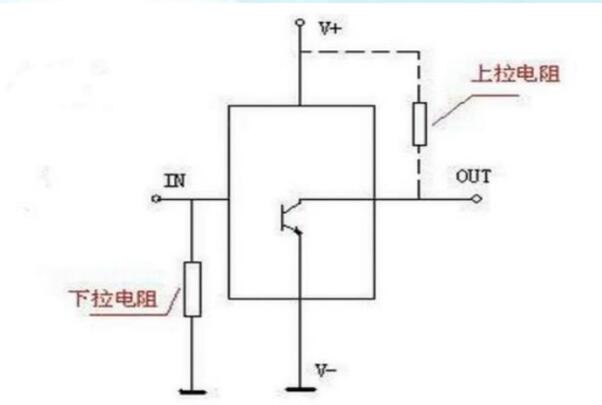

下拉電阻

1、概念:將一個(gè)不確定的信號(hào),通過(guò)一個(gè)電阻與地GND相連,固定在低電平;

2、下拉是從器件輸出電流;拉電流;

3、當(dāng)一個(gè)接有下拉電阻的IO端口設(shè)置為輸入狀態(tài)時(shí),它的常態(tài)為低電平;

下拉電阻的作用

1、提高電壓準(zhǔn)位:

a、當(dāng)TTL電路驅(qū)動(dòng)COMS電路時(shí),如果TTL電路輸出的高電平低于COMS電路的最低高電平(一般為3.5V), 這時(shí)就需要在TTL的輸出端接上拉電阻,以提高輸出高電平的值。

b、OC門(mén)電路必須加上拉電阻,以提高輸出的搞電平值。

2、加大輸出引腳的驅(qū)動(dòng)能力,有的單片機(jī)管腳上也常使用上拉電阻。

3、N/A pin防靜電、防干擾:在COMS芯片上,為了防止靜電造成損壞,不用的管腳不能懸空,一般接上拉電阻產(chǎn)生降低輸入阻抗, 提供泄荷通路。同時(shí)管腳懸空就比較容易接受外界的電磁干擾。

4、電阻匹配,抑制反射波干擾:長(zhǎng)線(xiàn)傳輸中電阻不匹配容易引起反射波干擾,加上下拉電阻是電阻匹配,有效的抑制反射波干擾。

5、預(yù)設(shè)空間狀態(tài)/缺省電位:在一些 CMOS 輸入端接上或下拉電阻是為了預(yù)設(shè)缺省電位。 當(dāng)你不用這些引腳的時(shí)候, 這些輸入端下拉接 0 或上拉接 1。在I2C總線(xiàn)等總線(xiàn)上,空閑時(shí)的狀態(tài)是由上下拉電阻獲得

6、提高芯片輸入信號(hào)的噪聲容限:輸入端如果是高阻狀態(tài),或者高阻抗輸入端處于懸空狀態(tài),此時(shí)需要加上拉或下拉,以免收到隨機(jī)電平而影響電路工作。同樣如果輸出端處于被動(dòng)狀態(tài),需要加上拉或下拉,如輸出端僅僅是一個(gè)三極管的集電極。從而提高芯片輸入信號(hào)的噪聲容限增強(qiáng)抗干擾能力。

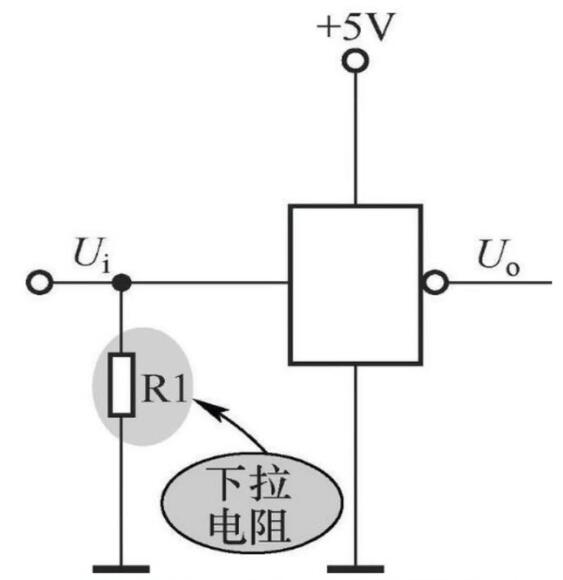

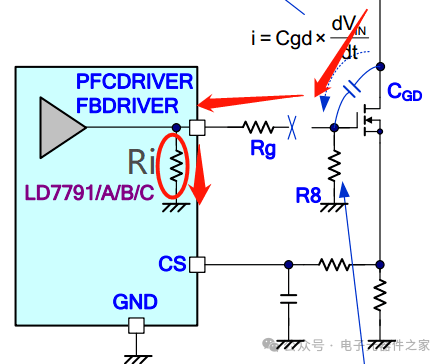

下拉電阻的原理圖

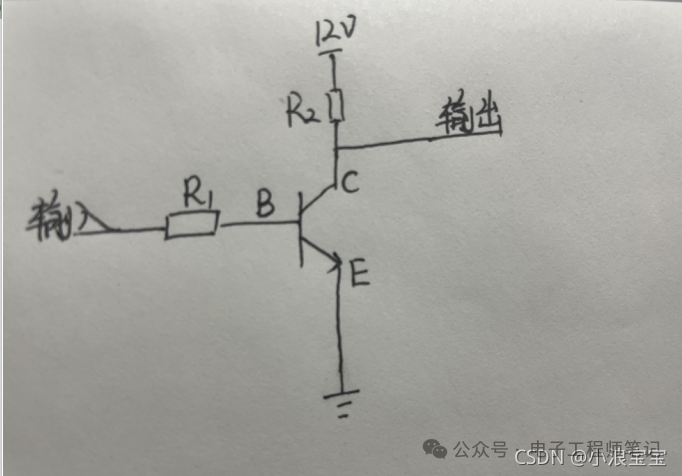

下拉電阻典型電路

圖所示是下拉電阻電路。這是數(shù)字電路中的反相器,輸入端Ui通過(guò)下拉電阻R1接地,這樣在沒(méi)有高電平輸入時(shí),可以使輸入端穩(wěn)定地處于低電平狀態(tài),防止了可能出現(xiàn)的高電平干擾使反相器誤動(dòng)作。

如果沒(méi)有下拉電阻R1,反相器輸入端懸空,為高阻抗,外界的高電平干擾很容易從輸入端加入到反相器中,從而引起反相器朝輸出低電平方向翻轉(zhuǎn)的誤動(dòng)作。

在接入下拉電阻R1后,電源電壓為5伏時(shí),下拉電阻R1一般取值在100至470歐,由于R1阻值很小,所以將輸入端的各種高電平干擾短接到地,達(dá)到抗干擾的目的。

下拉電阻選擇

下拉電阻的設(shè)定的原則和上拉電阻是一樣的。下拉電阻的選擇應(yīng)結(jié)合開(kāi)關(guān)管特性和下級(jí)電路的輸入特性進(jìn)行設(shè)定,主要需要考慮以下幾個(gè)因素:

1、驅(qū)動(dòng)能力與功耗的平衡。以上拉電阻為例,一般地說(shuō),上拉電阻越小,驅(qū)動(dòng)能力越強(qiáng),但功耗越大,設(shè)計(jì)時(shí)應(yīng)注意兩者之間的均衡。

2、下級(jí)電路的驅(qū)動(dòng)需求。同樣以上拉電阻為例,當(dāng)輸出高電平時(shí),開(kāi)關(guān)管斷開(kāi),上拉電阻應(yīng)適當(dāng)選擇以能夠向下級(jí)電路提供足夠的電流。

3、高低電平的設(shè)定。不同電路的高低電平的門(mén)檻電平會(huì)有不同,電阻應(yīng)適當(dāng)設(shè)定以確保能輸出正確的電平。以上拉電阻為例,當(dāng)輸出低電平時(shí),開(kāi)關(guān)管導(dǎo)通,上拉電阻和開(kāi)關(guān)管導(dǎo)通電阻分壓值應(yīng)確保在零電平門(mén)檻之下。

4、頻率特性。以上拉電阻為例,上拉電阻和開(kāi)關(guān)管漏源級(jí)之間的電容和下級(jí)電路之間的輸入電容會(huì)形成RC延遲,電阻越大,延遲越大。上拉電阻的設(shè)定應(yīng)考慮電路在這方面的需求。

-

下拉電阻

+關(guān)注

關(guān)注

4文章

152瀏覽量

20809

發(fā)布評(píng)論請(qǐng)先 登錄

浮思特 | 電子電路下拉電阻詳解:原理、計(jì)算與應(yīng)用指南

一次性說(shuō)清上拉電阻和下拉電阻

三極管下拉電阻設(shè)計(jì):穩(wěn)定與效率的平衡藝術(shù)

請(qǐng)問(wèn)Type C的CC管腳的CC1和CC2的下拉電阻是否能共用一個(gè)電阻?

DAC101S101初次上電瞬間下拉電阻的開(kāi)關(guān)是默認(rèn)閉合的嗎?

零歐姆電阻的作用和使用技巧

【RS-485總線(xiàn)】詳解RS-485上下拉電阻的選擇

下拉電阻的作用原理

下拉電阻的作用原理

評(píng)論