各位群友,大家晚上好,我是黃曉宗,一直從事模擬和混合信號(hào)IC設(shè)計(jì)工作,對(duì)ESD保護(hù)設(shè)計(jì)有一定的心得,今天和大家談?wù)?a href="http://www.asorrir.com/v/tag/123/" target="_blank">集成電路ESD保護(hù)的器件和電路,在交流的過程中會(huì)分享一些實(shí)際的案例,希望能夠?yàn)榇蠹易鲆恍┗A(chǔ)知識(shí)的鋪墊,也感謝大家在這里進(jìn)行交流。

我將分為以下部分介紹,在完成背景介紹后,將在第二、三和四章針對(duì)基本器件、二極管、SCR器件提高維持電壓的技術(shù)進(jìn)行討論。然后,通過工程案例和器件應(yīng)用,分析和優(yōu)化全芯片ESD保護(hù)設(shè)計(jì);第五章將討論SiP ESD中板級(jí)和片上協(xié)同保護(hù)的策略,提高系統(tǒng)的保護(hù)能力。

靜電放電現(xiàn)象在日常生活中非常常見,干燥的冬天手指觸碰到金屬門把手,就會(huì)發(fā)生放電現(xiàn)象。不同物體的接觸和分離就是最常見的靜電產(chǎn)生方式,例如摩擦可產(chǎn)生靜電。人體有感覺的靜電放電電壓在3000—5000V,這些靜電對(duì)人體并不是致命的,但是對(duì)沒有靜電防護(hù)的電子產(chǎn)品來說可能會(huì)造成非常嚴(yán)重的后果。

電子產(chǎn)品離不開芯片,也就離不開ESD保護(hù)設(shè)計(jì)。以我們的手機(jī)為例,移動(dòng)電話轉(zhuǎn)向智能電話技術(shù),智能手機(jī)按鍵被觸摸技術(shù)替代,取消了按鍵接口,人機(jī)交互通過觸摸屏完成。雖然目前的智能手機(jī)仍有耳機(jī)、電源充電、電源按鍵等端口外露,但是已經(jīng)大大減少。對(duì)于未來發(fā)展,當(dāng)“非接觸技術(shù)”(類似手勢(shì)控制)替代目前的“接觸技術(shù)”,那么直接的人機(jī)交互將減少靜電損傷的風(fēng)險(xiǎn)。芯片在生產(chǎn)、封裝、測(cè)試、組裝等過程中都受到ESD的威脅,所以保護(hù)設(shè)計(jì)也就貫穿整個(gè)芯片的始終。這是典型的ESD失效照片。

一般來講,一顆芯片上都會(huì)有相應(yīng)的ESD保護(hù)電路,其目標(biāo)就是泄放電流和鉗位電壓,保護(hù)脆弱的內(nèi)部電路。當(dāng)然,RF電路為了性能的考慮,可能無ESD保護(hù)結(jié)構(gòu),其靜電能力就可能200V-250V。

ESD對(duì)IC的損傷主要有兩類,即大電流產(chǎn)生局部熱量、高電場(chǎng)損傷絕緣層,都會(huì)導(dǎo)致電路或者器件功能性能的異常。ESD保護(hù)的基本原理就是并聯(lián)保護(hù)器件,以此泄放大電流和鉗位高電壓,避免對(duì)內(nèi)部電路造成損傷。

保護(hù)的原理已經(jīng)非常清楚,那么在具體實(shí)施過程中,一種方式是減少靜電的產(chǎn)生,例如靜電手套、指套、離子風(fēng)扇等中和靜電,這樣就減少了芯片受到的ESD威脅;另一種就是讓自身變得更加強(qiáng)大,既然無法避免強(qiáng)大靜電的產(chǎn)生,那么盡可能增強(qiáng)自身的抗ESD沖擊能力,這可以通過系統(tǒng)級(jí)和片上保護(hù)來實(shí)現(xiàn)。

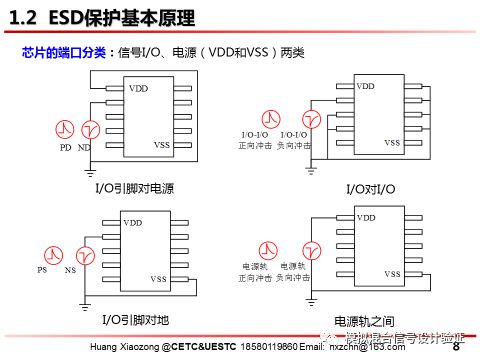

分析完這些ESD現(xiàn)象和保護(hù)原理,那么如何來評(píng)價(jià)一顆芯片的ESD能力呢?我們通常將芯片的引腳分為信號(hào)I/O、電源(VDD和VSS)兩類。這些引腳可以形成不同的沖擊組合,即PD/ND、PS/NS、I/O-I/O和電源軌之間進(jìn)行ESD沖擊,便于研究。

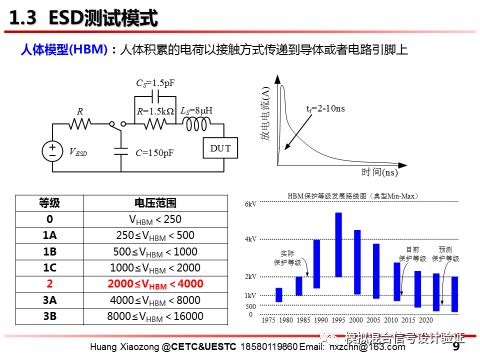

為了模擬芯片在不同場(chǎng)景下受到的ESD沖擊,建立了一系列標(biāo)準(zhǔn)的、可重復(fù)的ESD脈沖,對(duì)待測(cè)試器件進(jìn)行沖擊。例如模擬人體積累電荷對(duì)器件放電的人體模型,這是最常用的一種模式。通常IC的HBM ESD能力都要求2000V以上,但是對(duì)于敏感電路,例如RFIC、超高速的信號(hào)端口等,ESD能力要求會(huì)降低。

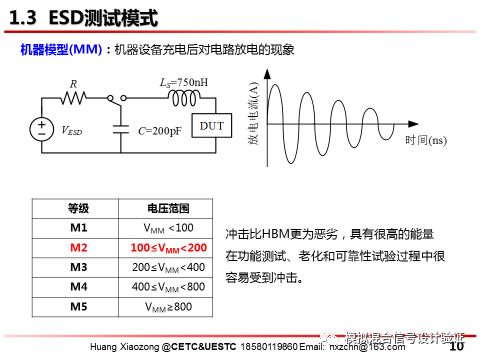

模擬充電金屬機(jī)械手對(duì)器件沖擊的機(jī)器模型,沖擊能量比HBM更加惡劣。

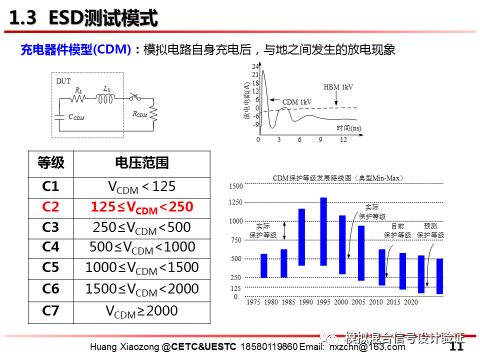

模擬器件自身充電,并對(duì)地放電的充電器件模型。CDM模式與HBM/MM模式顯著的不同在于電荷產(chǎn)生的方式,CDM是由器件自身積累電荷,而通過引腳泄放到地,形成沖擊電流,從而可能對(duì)電路造成損傷;HBM/MM則是外部(無論是人體還是機(jī)器)的電荷對(duì)電路造成損傷。

這些模型都是對(duì)獨(dú)立芯片或者器件的ESD沖擊。

當(dāng)器件裝配到系統(tǒng)中,仍需要對(duì)系統(tǒng)的ESD性能進(jìn)行評(píng)價(jià),那么就是通過電子槍對(duì)系統(tǒng)進(jìn)行沖擊的IEC系統(tǒng)級(jí)測(cè)試。然而,這些測(cè)試都只能對(duì)芯片的等級(jí)進(jìn)行判定,并不能對(duì)器件特性進(jìn)行表征,那么TLP測(cè)試模式就被引入了。

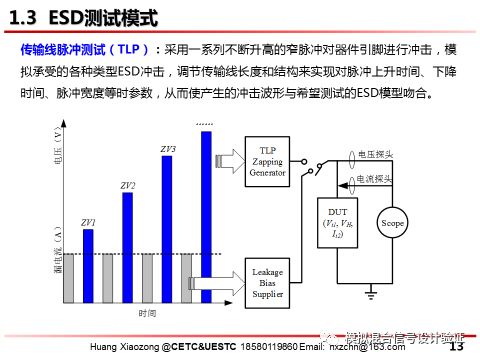

TLP是常用的分析手段,通過一系列窄脈沖對(duì)引腳進(jìn)行沖擊,并且可以調(diào)節(jié)時(shí)間參數(shù),模擬不同沖擊下的行為。

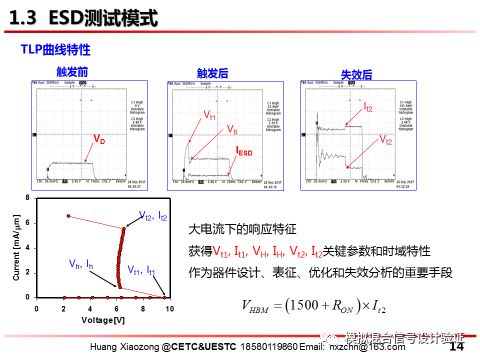

通過時(shí)域波形提取每次沖擊下的電壓、電流,并監(jiān)測(cè)漏電流變化,從而獲取關(guān)鍵參數(shù),作為器件設(shè)計(jì)和優(yōu)化的重要手段。

目前已有大量的TLP商用設(shè)備,我的研究主要基于Hanwa的TLP設(shè)備。TLP可以表征HBM/MM的等效特征,快速TLP(VeryFast TLP,vfTLP)通過調(diào)節(jié)傳輸線長度和結(jié)構(gòu)實(shí)現(xiàn)了CDM沖擊等效特征的模擬,產(chǎn)生脈沖寬度1ns-5ns,上升時(shí)間0.1ns-0.4ns,如此短暫的時(shí)間小于硅材料中熱擴(kuò)散時(shí)間常數(shù),可以較好評(píng)估器件和電路在快速放電狀態(tài)下的行為,但是因?yàn)関fTLP和CDM的電流泄放路徑通常存在差異,所以并不能預(yù)測(cè)器件和電路的失效閾值。

下面我們對(duì)ESD基本保護(hù)器件的特性進(jìn)行簡單分析。

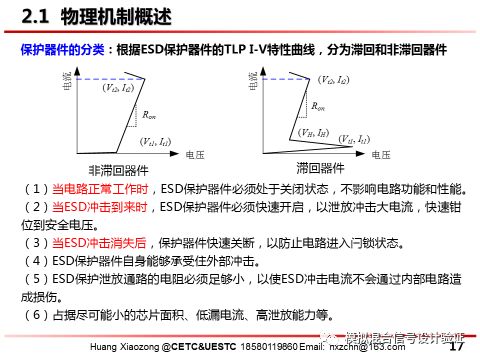

ESD保護(hù)器件主要有滯回和非滯回兩類,都需要滿足以下條件:

(1)當(dāng)電路正常工作時(shí),ESD保護(hù)器件必須處于關(guān)閉狀態(tài),不影響電路功能和性能。

(2)當(dāng)ESD沖擊到來時(shí),ESD保護(hù)器件必須快速開啟,以泄放沖擊大電流,快速鉗位到安全電壓。

(3)當(dāng)ESD沖擊消失后,保護(hù)器件快速關(guān)斷,以防止電路進(jìn)入閂鎖狀態(tài)。

ESD保護(hù)器件就像一位優(yōu)秀而強(qiáng)健的保鏢,當(dāng)有危險(xiǎn)到來時(shí),及時(shí)現(xiàn)身保護(hù)主人,當(dāng)危險(xiǎn)消失后,保鏢也就默默地走到一旁。

(4)ESD保護(hù)器件自身能夠承受住外部沖擊。

(5)ESD保護(hù)泄放通路的電阻必須足夠小,以使ESD沖擊電流不會(huì)通過內(nèi)部電路造成損傷。

(6)占據(jù)盡可能小的芯片面積、低漏電流、高泄放能力等。

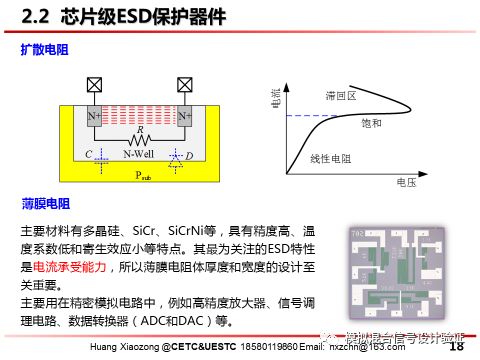

電阻在ESD保護(hù)中起到輔助作用,具有不同的行為特性。擴(kuò)散電阻在沖擊下具有飽和特性,這是因?yàn)?a target="_blank">半導(dǎo)體材料的電阻率是由載流子遷移率和濃度決定,當(dāng)電場(chǎng)強(qiáng)度使得載流子遷移率飽和后,電阻率只與濃度相關(guān),所以出現(xiàn)飽和特性;當(dāng)電壓進(jìn)一步增大時(shí),出現(xiàn)碰撞電離,雪崩產(chǎn)生大量載流子,從而出現(xiàn)滯回區(qū)。薄膜電阻則重點(diǎn)關(guān)注電流承受能力,后面將有所涉及。

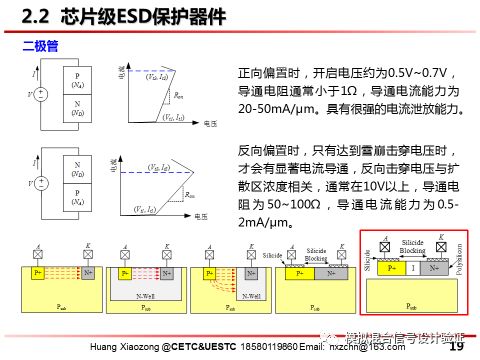

正向?qū)ǘO管具有很強(qiáng)的泄放能力,是重要的保護(hù)器件,在射頻、數(shù)字端口保護(hù)中常用。但是反向二極管電流能力弱,若作為ESD保護(hù),需要較大的芯片面積。

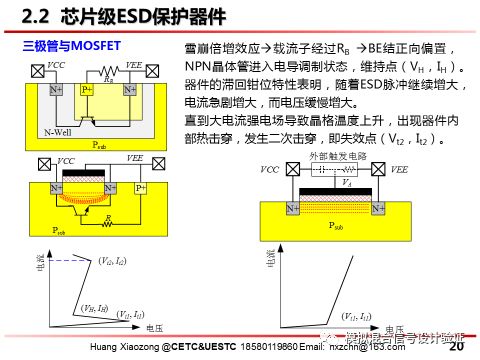

三極管和GGNMOS在反偏結(jié)擊穿后,整體器件進(jìn)入電導(dǎo)調(diào)制的滯回狀態(tài),形成S形滯回曲線,泄放電流。MOS管的柵極還可通過RC觸發(fā)實(shí)現(xiàn)動(dòng)態(tài)的溝道電流泄放能力。

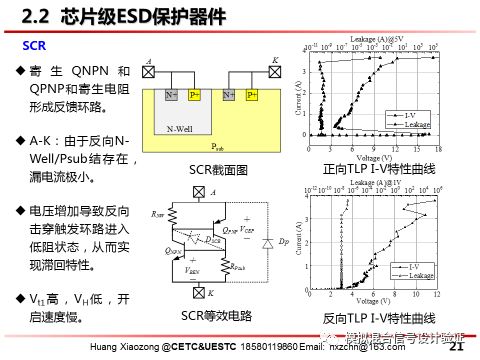

SCR是重要的ESD保護(hù)器件,通過PNPN結(jié)構(gòu)形成反饋環(huán)路,這是典型的特性曲線,具有Vt1高,VH低,開啟速度慢的特點(diǎn)。注意對(duì)于SCR來說,反向特性雖然也是一個(gè)二極管,但是串聯(lián)了Rpsub和RNW,會(huì)影響導(dǎo)通電阻,直接影響鉗位特性和導(dǎo)通電阻,所以通常并聯(lián)一個(gè)Dp。第四章將針對(duì)其維持電壓進(jìn)行優(yōu)化設(shè)計(jì)。

下面我們來討論一下二極管在ESD保護(hù)中的應(yīng)用及其優(yōu)化設(shè)計(jì)的一些研究。

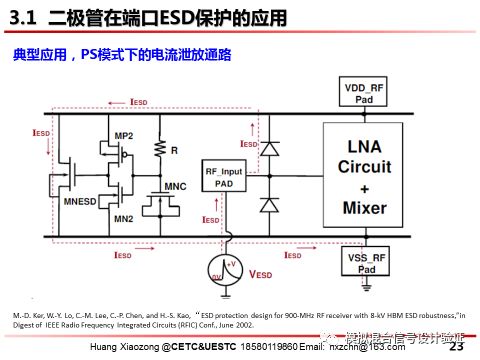

我們首先重溫一下剛才討論到二極管的情況,正向?qū)‥SD保護(hù)能力強(qiáng),開啟電壓低;每一個(gè)端口都有對(duì)電源軌、其他端口的ESD沖擊模式。這里針對(duì)實(shí)際電路說明泄放通路。PS:反向二極管不易導(dǎo)通,那么正向二極管與電源軌之間的保護(hù)形成通道。

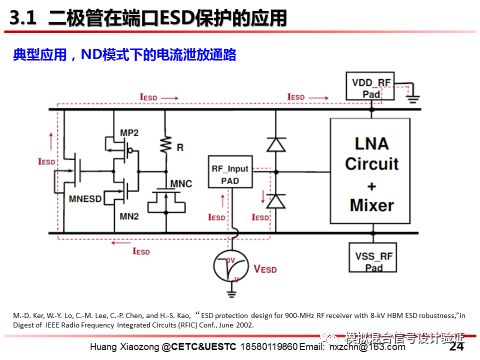

這是ND模式,對(duì)電源進(jìn)行負(fù)壓沖擊,也有類似的電流泄放通路。

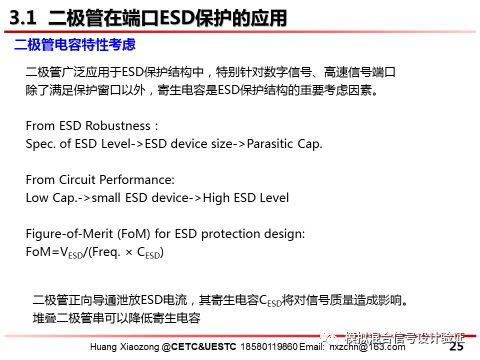

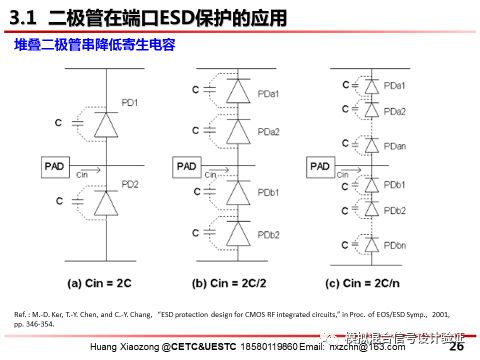

二極管結(jié)構(gòu)簡單,易于使用,廣泛應(yīng)用于ESD保護(hù)結(jié)構(gòu)中,特別針對(duì)數(shù)字信號(hào)、高速信號(hào)端口。除了滿足保護(hù)窗口以外,寄生電容是ESD保護(hù)結(jié)構(gòu)的重要考慮因素。這里主要針對(duì)堆疊器件做一個(gè)說明。

可以看出,串聯(lián)二極管的寄生電容隨著串聯(lián)數(shù)量增加而成比例減小,這對(duì)于高速信號(hào)端口來說是極其重要的特性,但是串聯(lián)數(shù)量越多,也會(huì)導(dǎo)致其開啟電壓越高,導(dǎo)通電阻越大,會(huì)影響ESD保護(hù)性能。

這是一個(gè)常規(guī)二極管的Layout,下面將針對(duì)堆疊二極管的版圖優(yōu)化進(jìn)行介紹,說明Layout對(duì)ESD能力的影響。

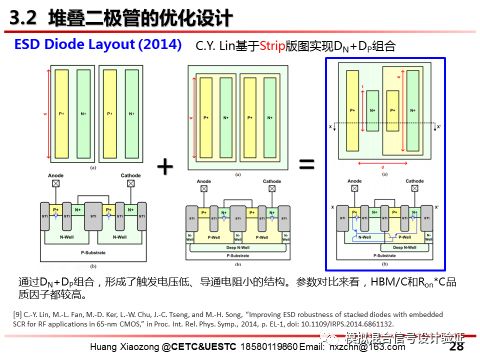

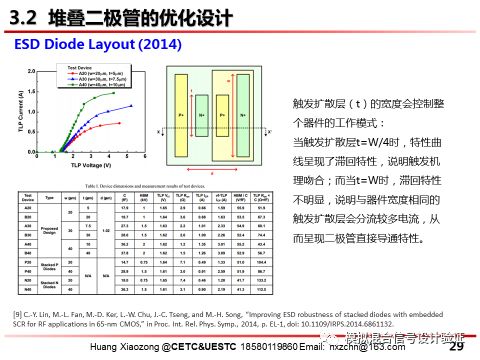

我們通常看到的二極管就是兩個(gè)相同二極管的堆疊,例如P+/Nwell或者N+/Pwell,但是只要將兩種器件混合,就會(huì)出現(xiàn)新的機(jī)理,如右圖的結(jié)構(gòu),形成了PNPN的SCR通路,而觸發(fā)則是由二極管實(shí)現(xiàn),具有低觸發(fā)電壓的特點(diǎn)。

從測(cè)試的TLP特性可以看出,觸發(fā)擴(kuò)散層(t)的寬度會(huì)控制整個(gè)器件的工作模式:當(dāng)觸發(fā)擴(kuò)散層t=W/4時(shí),特性曲線呈現(xiàn)了滯回特性,這與SCR觸發(fā)機(jī)理吻合,當(dāng)t較小時(shí),串聯(lián)二極管上分流電流較少,剩余的電流將觸發(fā)寄生的SCR通路;而當(dāng)t=W時(shí),滯回特性不明顯,說明與器件寬度相同的觸發(fā)擴(kuò)散層會(huì)分流較多電流,從而呈現(xiàn)二極管直接導(dǎo)通特性。

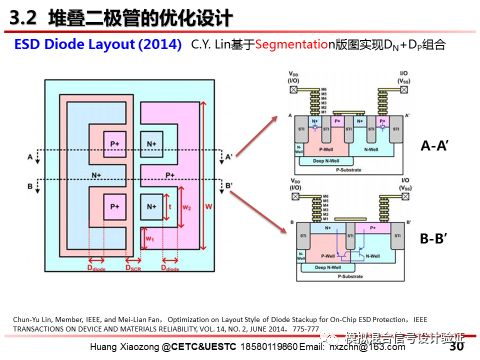

在同一年,該研究對(duì)版圖進(jìn)行優(yōu)化,利用分割的方式實(shí)現(xiàn)了Dn+Dp的組合,從AA’和BB’截面可以看出,該器件具有兩種路徑,一種是串聯(lián)的二極管,另一種是SCR通路。

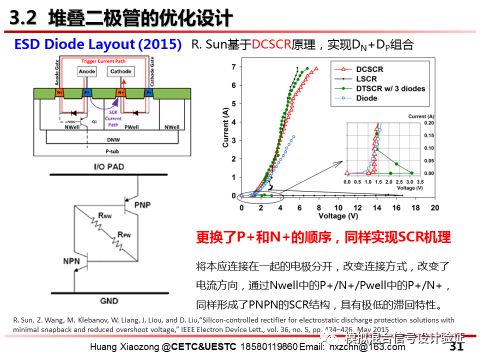

2015年這個(gè)結(jié)構(gòu)將本應(yīng)連接在一起的電極分開,改變連接方式,改變了電流方向,通過Nwell中的P+/N+/Pwell中的P+/N+,同樣形成了PNPN的SCR結(jié)構(gòu),具有極低的滯回特性。

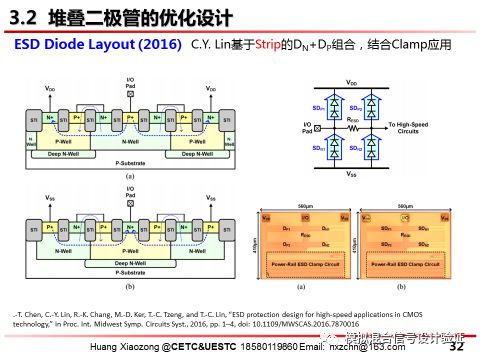

這里將前面的版圖優(yōu)化結(jié)構(gòu)進(jìn)行了工程應(yīng)用,配合Power Clamp實(shí)現(xiàn)電路的保護(hù),并對(duì)全芯片保護(hù)的特性進(jìn)行了分析。

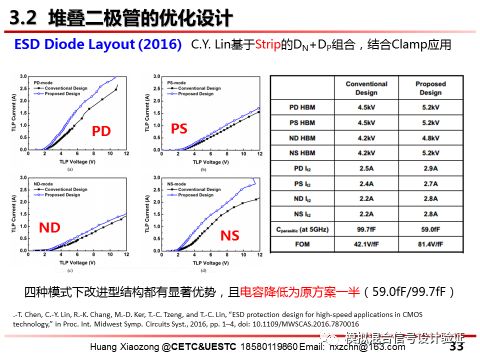

可以看出,在不同的沖擊模式下,和傳統(tǒng)的堆疊器件(傳統(tǒng)器件就是2Dn或者2Dp)相比都有顯著優(yōu)勢(shì),ESD性能更高,電容降低為原方案一半(59.0fF/99.7fF)。

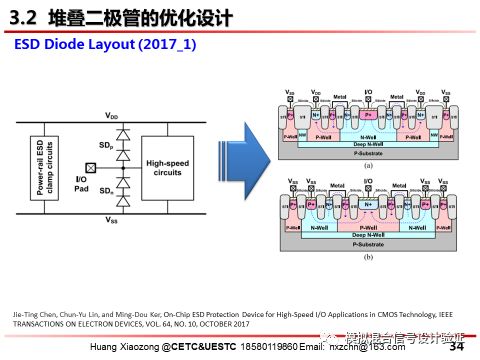

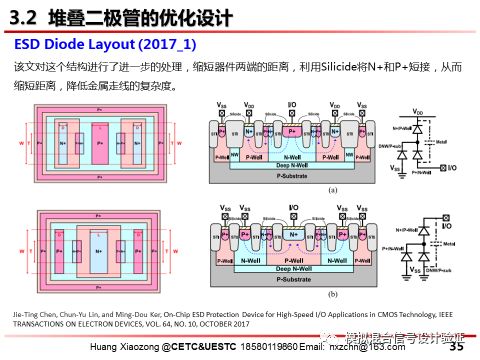

該研究對(duì)Dn+Dp的串聯(lián)形式進(jìn)行了進(jìn)一步的優(yōu)化,利用Silicide將N+和P+短接,從而縮短器件兩端的距離,降低金屬走線的復(fù)雜度。

針對(duì)DCSCR,從A-K(Cathode-Anode),有PN二極管和P+/Nw/Pw/N+形成的SCR,二極管優(yōu)先導(dǎo)通,并觸發(fā)SCR通路,從Nw流出的電流,本質(zhì)上開啟了寄生的PNP晶體管(Nw是PNP的基極);進(jìn)入Pw的電流,本質(zhì)上開啟了寄生的NPN晶體管(Pw是NPN的基極),實(shí)現(xiàn)更強(qiáng)的電流泄放能力,當(dāng)然,這里的特性與二極管非常相似。

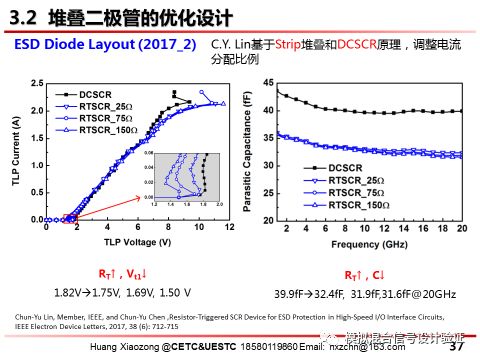

通過不同電阻值的對(duì)比測(cè)試可以看出,當(dāng)串聯(lián)電阻增大時(shí),觸發(fā)電壓Vt1降低。在論文中對(duì)寄生電容進(jìn)行了近似分析,其電容值也隨著串聯(lián)電阻的增大而減小。

SCR是重要的ESD保護(hù)器件,也是ESD研究領(lǐng)域的重要課題,這里簡要介紹采用分割方式提高維持電壓的技術(shù)。

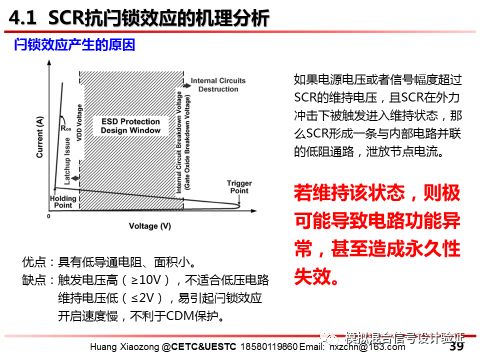

前面已提到,SCR具有低維持電壓的特點(diǎn)。如果電源電壓或者信號(hào)幅度超過SCR的維持電壓,且SCR在外力沖擊下被觸發(fā)進(jìn)入維持狀態(tài),那么SCR形成一條與內(nèi)部電路并聯(lián)的低阻通路,泄放節(jié)點(diǎn)電流。若維持該狀態(tài),則極可能導(dǎo)致電路功能異常,甚至造成永久性失效。

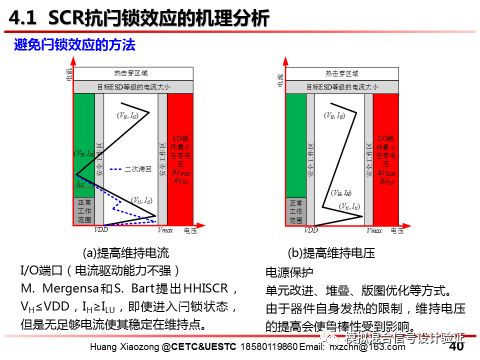

避免閂鎖效應(yīng)的方法之一,是提高維持電流到閂鎖電流之上,這對(duì)電流驅(qū)動(dòng)能力不強(qiáng)的I/O端口來說比較實(shí)用。但對(duì)于電源之間的保護(hù),提高維持電壓是更好的方式,業(yè)界已研究多種方式,但是魯棒性會(huì)受到影響。M. Mergensa和S. Bart等通過增加外部并聯(lián)電阻和版圖優(yōu)化提高維持電流,形成高維持電流SCR(High Holding Current SCR,HHISCR),當(dāng)維持電壓VH≤VDD,但是IH≥ILU,即使進(jìn)入閂鎖狀態(tài),因?yàn)闊o足夠電流使其穩(wěn)定在維持點(diǎn),可使電路脫離閂鎖狀態(tài)。

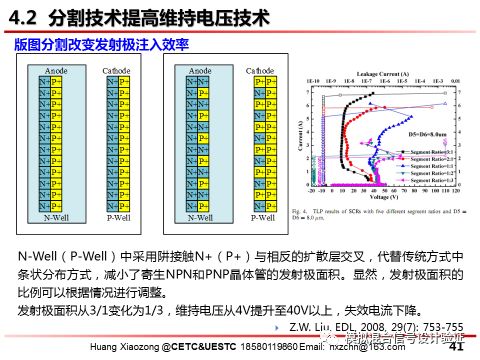

首先是通過版圖分割技術(shù),利用擴(kuò)散層交叉的方式替代條狀分布方式,調(diào)節(jié)發(fā)射極注入效率,可實(shí)現(xiàn)維持電壓提升,但是由于發(fā)射極面積減小,失效電流下降顯著,大家可以參考相應(yīng)的文獻(xiàn)。

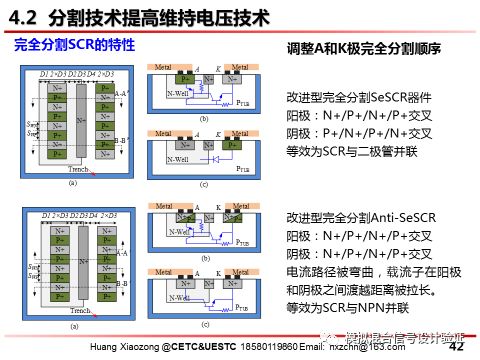

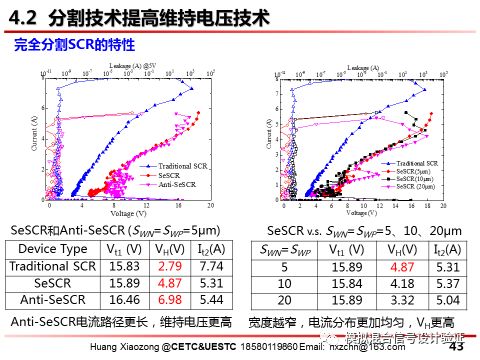

完全分割技術(shù)在單向SCR中可以進(jìn)一步探討,調(diào)整陰極和陽極的分割順序,命名為SeSCR(陽極:N+/P+/N+/P+交叉、陰極:P+/N+/P+/N+交叉,等效為SCR與二極管并聯(lián))和Anti-SeSCR(陽極:N+/P+/N+/P+交叉、陰極:N+/P+/N+/P+交叉;電流路徑被彎曲,載流子在陽極和陰極之間渡越距離被拉長。等效為SCR與NPN并聯(lián))。

Anti-SeSCR電流路徑更長,維持電壓可達(dá)到接近7V,SeSCR分割寬度越窄,電流分布更加均勻,所以VH更高。

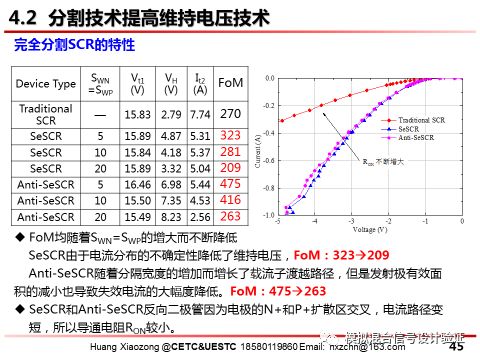

Anti-SeSCR隨著分割寬度增加,維持電壓顯著增加,這是因?yàn)榭昭ㄏ蜿帢ON+擴(kuò)展,不斷復(fù)合,濃度降低,且隨著∠α越大,載流子濃度越低,有效的發(fā)射極寬度為SWN_eff減小。同時(shí)伴隨載流子渡越距離變長,維持電壓就隨之提高。

但是有效發(fā)射極面積減小,導(dǎo)致電流聚集效應(yīng)顯著,It2下降。

這里定義了品質(zhì)因子FoM(VH×It2/Width),F(xiàn)oM均隨著SWN=SWP的增大而不斷降低。因?yàn)橥耆指罱Y(jié)構(gòu),使得反向二極管的電流路徑變短,導(dǎo)通電阻RON更小。

上面的內(nèi)容都是介紹獨(dú)立器件的設(shè)計(jì),單純器件的特性并不一定能夠滿足全芯片ESD保護(hù)的要求,必須匹配相應(yīng)的保護(hù)窗口。下面將對(duì)全芯片ESD保護(hù)設(shè)計(jì)技術(shù)進(jìn)行案例說明。

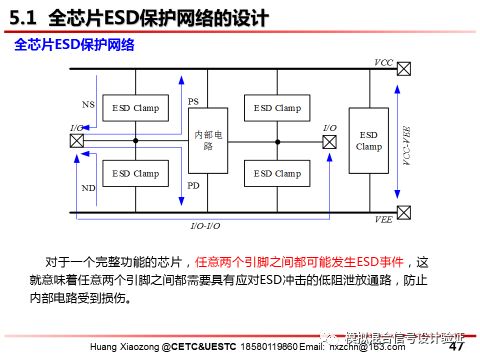

對(duì)于一個(gè)完整功能的芯片,任意兩個(gè)引腳之間都可能發(fā)生ESD事件,需要相應(yīng)的泄放通路。圖中表示了各種沖擊下的電流泄放路徑。

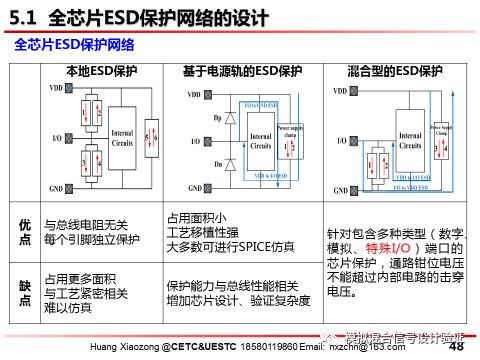

全芯片ESD保護(hù)網(wǎng)絡(luò)通常可以分為以上三種情況,各有優(yōu)缺點(diǎn)。針對(duì)引腳數(shù)量少的模擬電路,可以選用本地ESD保護(hù)網(wǎng)絡(luò),不需要借助總線,每個(gè)引腳均可獨(dú)立實(shí)現(xiàn)保護(hù);基于電源軌的ESD保護(hù)具有占用面積小,工藝移植性強(qiáng)的優(yōu)點(diǎn),但是增加了芯片設(shè)計(jì)和驗(yàn)證的復(fù)雜度;混合型ESD保護(hù)網(wǎng)絡(luò)主要面向多種類型端口的芯片,例如帶有RS485接口的混合信號(hào)IC。

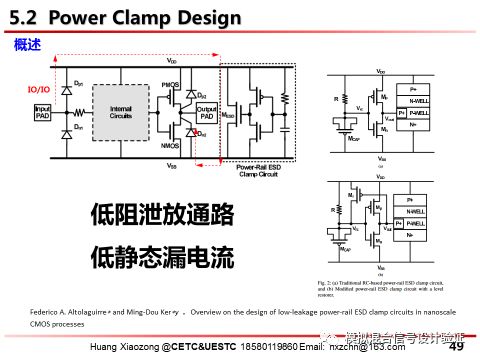

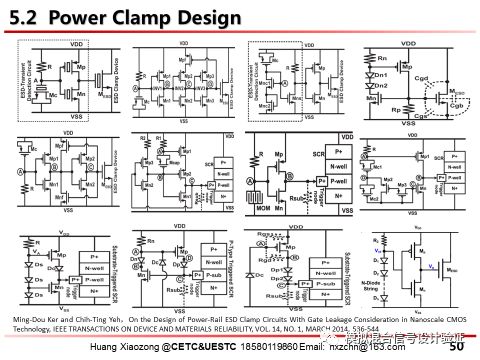

這里說明了PowerClamp在保護(hù)網(wǎng)絡(luò)中的應(yīng)用,對(duì)于基于電源軌的保護(hù)策略來說,Power Clamp的性能極其重要,需要具備低阻泄放通路、低靜態(tài)漏電流等特點(diǎn)。這里僅對(duì)一些典型結(jié)構(gòu)進(jìn)行列舉。

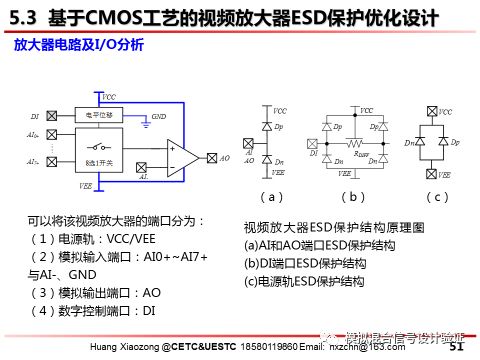

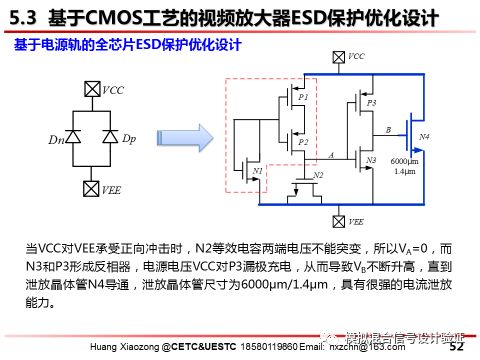

這里以一個(gè)基于CMOS工藝的視頻放大器ESD保護(hù)優(yōu)化設(shè)計(jì)的案例,說明基于電源軌的保護(hù)策略,如何通過優(yōu)化PowerClamp達(dá)到提升整體ESD能力的目的。

原保護(hù)方案采用了左圖反向二極管的方式,在ESD測(cè)試過程中,出現(xiàn)輸出端損傷的情況。經(jīng)過電參數(shù)測(cè)試和失效分析,確定了ESD損傷機(jī)理。更改為右圖的有源泄放結(jié)構(gòu)可以很好實(shí)現(xiàn)電流泄放。下面通過TLP對(duì)比測(cè)試來說明。

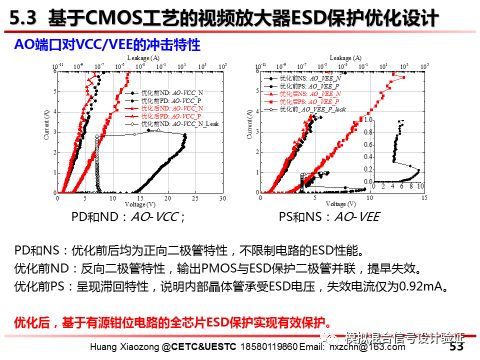

從測(cè)試曲線可以看出,PD和NS在優(yōu)化前后均為正向二極管特性,不限制電路的ESD性能。優(yōu)化前ND:反向二極管特性,輸出PMOS與ESD保護(hù)二極管并聯(lián),提早失效。優(yōu)化前PS:呈現(xiàn)滯回特性,說明內(nèi)部晶體管承受ESD電壓,失效電流僅為0.92mA。優(yōu)化后,基于有源鉗位電路的全芯片ESD保護(hù)實(shí)現(xiàn)有效保護(hù)。

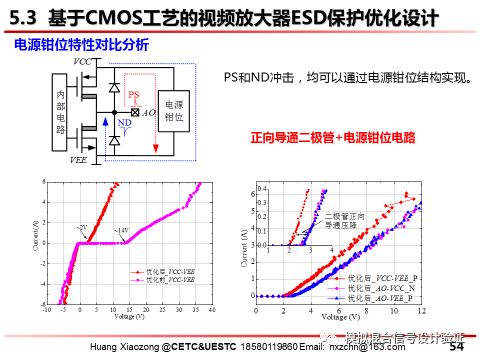

這一頁的測(cè)試結(jié)果驗(yàn)證了有源泄放的Power Clamp作為公共總線泄放PS和ND的ESD沖擊特性,PS和ND的特性均為一個(gè)正向?qū)ǘO管+電源鉗位電路的I-V特性疊加,達(dá)到了提升全芯片ESD保護(hù)能力的目的。

在全芯片ESD保護(hù)的基礎(chǔ)上,我們對(duì)系統(tǒng)級(jí)封裝的ESD保護(hù)進(jìn)行了一定研究,說明片上和板級(jí)的協(xié)同保護(hù)策略。

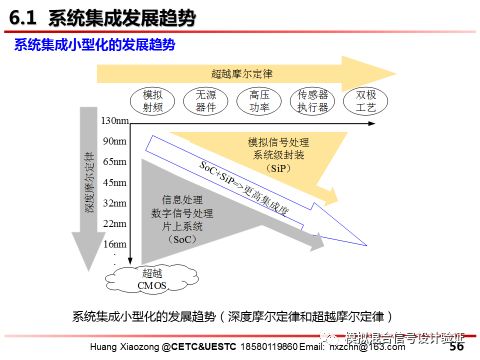

眾所周知,集成電路的小型化發(fā)展沿著More Moore和More than Moore兩個(gè)趨勢(shì)發(fā)展,而隨著More Moore對(duì)于成本要求不斷提高,More than Moore成了重要的解決方案,通過不以小尺寸為目標(biāo)的特種工藝設(shè)計(jì)模擬、射頻和功率器件,通過SiP技術(shù)將不同功能的電路、甚至MEMS等傳感器進(jìn)行系統(tǒng)級(jí)封裝,實(shí)現(xiàn)解決方案的小型化。

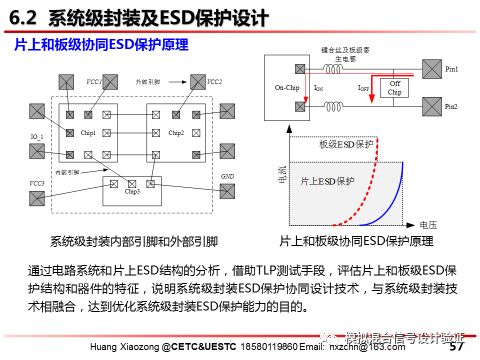

對(duì)于系統(tǒng)級(jí)封裝的ESD保護(hù),首先要區(qū)分封裝內(nèi)部引腳和外部引腳,通過電路系統(tǒng)和片上ESD結(jié)構(gòu)的分析,借助TLP測(cè)試手段,評(píng)估片上和板級(jí)ESD保護(hù)結(jié)構(gòu)和器件的特征,說明系統(tǒng)級(jí)封裝ESD保護(hù)協(xié)同設(shè)計(jì)技術(shù),與系統(tǒng)級(jí)封裝技術(shù)相融合,達(dá)到優(yōu)化系統(tǒng)級(jí)封裝ESD保護(hù)能力的目的。

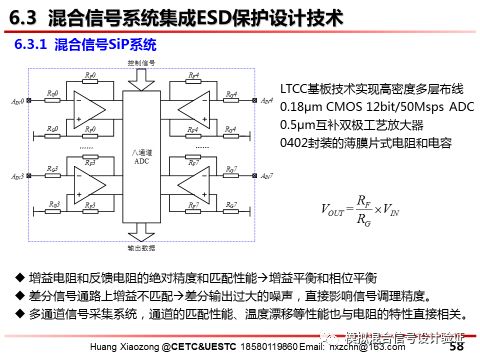

這是一個(gè)混合集成的多通道ADC產(chǎn)品,利用LTCC基板實(shí)現(xiàn)多層高密度布線,集成了不同工藝實(shí)現(xiàn)的芯片和若干電容和電阻,根據(jù)性能要求選擇了低溫度系數(shù)、高精度的薄膜電阻作為增益電阻。

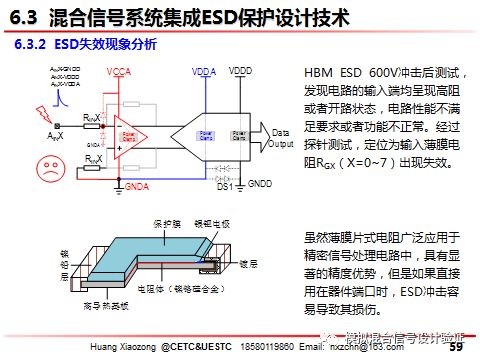

HBM ESD600V沖擊后測(cè)試,發(fā)現(xiàn)電路的輸入端均呈現(xiàn)高阻或者開路狀態(tài),電路性能不滿足要求或者功能不正常。經(jīng)過探針測(cè)試,定位為輸入薄膜電阻RGX(X=0~7)出現(xiàn)失效。我們對(duì)端口的薄膜電阻進(jìn)行了分析,其結(jié)構(gòu)采用了鎳鉻硅合金作為電阻體,具有精度優(yōu)勢(shì),但是其抗ESD沖擊的能力較弱。

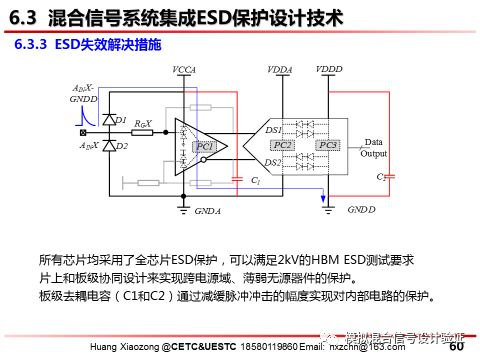

在板上增加D1和D2二極管,配合芯片的Power Clamp,泄放端口沖擊的ESD電流,片上和板級(jí)協(xié)同設(shè)計(jì)來實(shí)現(xiàn)跨電源域、薄弱無源器件的保護(hù)。板級(jí)去耦電容(C1和C2)通過減緩脈沖沖擊的幅度實(shí)現(xiàn)對(duì)內(nèi)部電路的保護(hù),優(yōu)化后的方案可達(dá)到2000V以上。

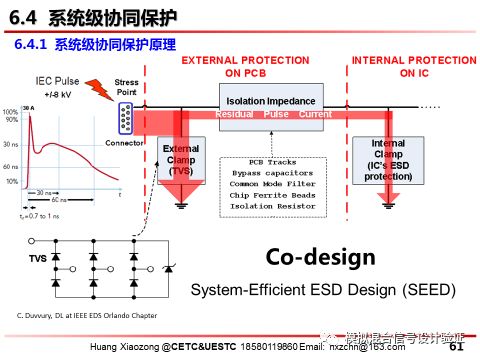

這就說明了片上和板級(jí)協(xié)同保護(hù)的基本原理,利用板級(jí)器件泄放主要的沖擊電流,而片上的保護(hù)結(jié)構(gòu)僅承受少量的殘余沖擊電流即可,從而保護(hù)端口不受損傷。

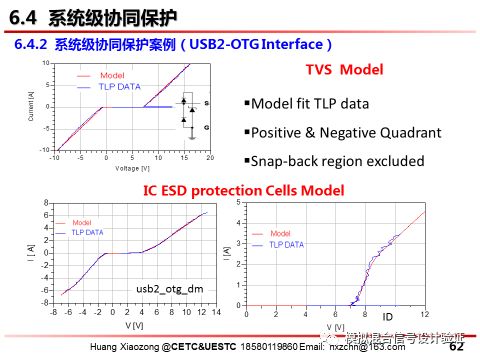

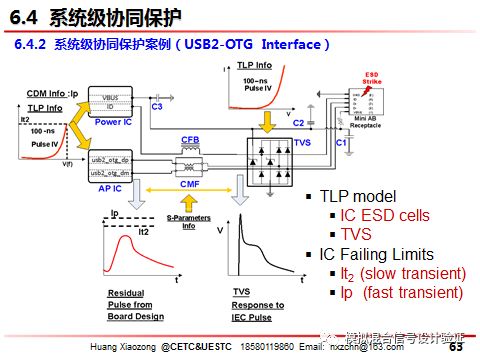

這里說明一個(gè)USB2-OTG接口的保護(hù)案例,首先要對(duì)備選的TVS器件和被保護(hù)芯片進(jìn)行TLP分析和建模,確保兩者的特性匹配,板級(jí)保護(hù)要優(yōu)于片上保護(hù),且優(yōu)先開啟。

這里說明了最終的保護(hù)原理圖,利用了CMF、CFB、TVS等多種器件實(shí)現(xiàn)對(duì)芯片的保護(hù),使其在熱插拔等惡劣條件下具有充分的魯棒性。

最終的方案可以看出,為了保護(hù)一顆芯片,板級(jí)采用了多種類型的保護(hù)器件來實(shí)現(xiàn),這就是大批量、高可靠性產(chǎn)品需要的ESD保護(hù)設(shè)計(jì)。

這里展示了ADI公司的一款典型產(chǎn)品,采用了協(xié)同保護(hù)的理念對(duì)MEMS Switch進(jìn)行了性能優(yōu)化。MEMS靠靜電力驅(qū)動(dòng),但是同時(shí)也要防止RF端口被靜電損傷,間隙火花放電現(xiàn)象是主要的ESD事件。

通過在系統(tǒng)級(jí)封裝中增加ESD外部器件,使得靜電敏感的MEMS器件不受損傷,從而實(shí)現(xiàn)了高性能和高可靠性的創(chuàng)新產(chǎn)品。

感謝各位群友的聆聽和交流,如果有不正確或者不全面的,歡迎大家批評(píng)指正,謝謝。

問答互動(dòng)

模*:您說的薄膜電阻是Thin Film Resisitor么?我查了一下,好像ESD能力確實(shí)比較差,如果做在片內(nèi),并且做在輸入端,這樣還有辦法提

高ESD能力么?

Answer:Thin Film Resisitor ESD能力比較低,在設(shè)計(jì)方面主要通過優(yōu)化電阻的Layout上來實(shí)現(xiàn)。可以在電阻網(wǎng)絡(luò)上增加ESD保護(hù)二極管,這都是在定制電阻網(wǎng)絡(luò)的情況下可以實(shí)現(xiàn)的。剛才報(bào)告里面采用的是分立0402電阻,但是通常的電阻網(wǎng)絡(luò)芯片可以定制,ESD能力取決于版圖寬度和薄膜層厚度,需要工藝廠家一起協(xié)作。

模*:芯片都有ESD保護(hù)電路,這樣Thin Film Resisitor是否在輸入端或者哪里,是否應(yīng)該不會(huì)受到ESD影響?如果有影響運(yùn)放輸入管的柵就很容易損壞了。

Answer:Thin Film Resistor在端口才會(huì)受到ESD沖擊的損傷,內(nèi)部就不用考慮其直接的ESD損傷,但是也要注意,如果該電阻在ESD電流的泄放通路上,也要考慮其承受電流的能力。

陳*:謝謝分享!,請(qǐng)問有低漏電的ESD結(jié)構(gòu)么?

Answer:一般來講,SCR和反向二極管的漏電都比較低,如果采用RC Clamp作為電源鉗位,也有很多結(jié)構(gòu),那一頁P(yáng)PT里面可參考相應(yīng)文獻(xiàn)。

風(fēng)*:ESD性能可以拿器件進(jìn)行Spice 或者Spectre仿真嗎(這樣的仿真準(zhǔn)確嗎)?還是要進(jìn)行專門的建模呢?特別是SCR這種ESD器件。這個(gè)應(yīng)該可以仿真,但是我不會(huì)看,之前見過別人仿真,但是我實(shí)在看不出來,仿真(5v)和實(shí)際如何對(duì)比。

Answer:Modeling是個(gè)重要的課題,有不少人研究,可以用VerilogA寫;SCR需要專門建模,通用器件在大電流下特性也會(huì)變化。ESD如果建模就可以跟電路一起仿真,但是我不太熟悉;ESD器件設(shè)計(jì)時(shí)通常會(huì)使用TCAD等EDA做器件特性仿真,預(yù)測(cè)特性。通用器件的spice仿真有意義,例如二極管、RC Clamp。

松*:CDM保護(hù)的一般結(jié)構(gòu)和HBM有什么異同嗎?

Answer:CDM放電速度遠(yuǎn)快于HBM,其脈沖上升時(shí)間<400ps,而HBM的上升時(shí)間約為10ns,并且CDM模式和封裝尺寸有關(guān),保護(hù)結(jié)構(gòu)需要快速開啟,需要速度快的結(jié)構(gòu)。

孫*:ESD泄放電流都是A級(jí)別的瞬態(tài)電流。Metal的線寬除了滿足走線電阻足夠小的需求,Current Density一般按照什么標(biāo)準(zhǔn)考慮?比如拿泄放電流的5%,10%當(dāng)DC Current算最小Width,有沒有個(gè)經(jīng)驗(yàn)值?

Answer:CurrentDensity有文獻(xiàn)([2010Ebook]_A.Vashchenko_ESD Design for Analog Circuits)給出DC電流40X經(jīng)驗(yàn)值的說法,可以參考。

高*:端口鉗位電壓怎么考慮?

Answer:鉗位電壓保證不超過端口器件的擊穿電壓,同時(shí)高于信號(hào)電壓或者電源電壓(避免閂鎖,也可以提高ESD器件的維持電流來實(shí)現(xiàn))

IC*:高壓60V的ESD如何做…一般Vhold都低

Answer:高壓要參考ESD Window,高Vhold SCR有不少方案,例如發(fā)射極分割,用低維持電壓堆疊等,例如兩個(gè)30V或者三個(gè)20V。

澤*:您剛才說鉗位電壓不超過擊穿電壓,ESD這種瞬時(shí)擊穿電壓,是不是會(huì)比直流擊穿電壓大一些,有這種區(qū)分嗎?

Answer:鉗位電壓不超過器件本身的擊穿電壓,ESD保護(hù)的作用就是把瞬時(shí)沖擊電壓壓縮到安全范圍。

冰*:有Vhold能堆疊,但是Vtrigger不怎么增加的技術(shù)嗎?目前高Vhold ESD主流用的都是發(fā)射極分割的SCR嗎?請(qǐng)問能高到多少V?面積多大呢?

Answer:有結(jié)構(gòu)可以增加Vhold,但是維持Vtrigger不變的研究,通過外部觸發(fā)的機(jī)制,同時(shí)觸發(fā)堆疊的單元。參考”FeiMa, Bin Zhang and Yan Han, High Holding Voltage SCR-LDMOS Stacking StructureWith Ring-Resistance-Triggered Technique IEEE Electron Device Letters, 34(9),2013”。當(dāng)然也有其他的實(shí)現(xiàn)方式。發(fā)射極分割的結(jié)構(gòu)本身不增加版圖面積,與傳統(tǒng)結(jié)構(gòu)相當(dāng)。如果需要更大的維持電壓,那么會(huì)導(dǎo)致單位面積上失效電流減小,需要增加版圖面積提高保護(hù)能力。

Q*:做的高速的ESD可以用網(wǎng)絡(luò)分析儀或者時(shí)域反射計(jì)量電容啊

Answer:這方面我沒有看到太多工程應(yīng)用的案例,僅在有的項(xiàng)目中做過應(yīng)用。

凱*:請(qǐng)教個(gè)問題,在BUCK電路中,仿真時(shí),強(qiáng)驅(qū)動(dòng)下開關(guān)過程會(huì)產(chǎn)生ns級(jí)超過器件耐壓的毛刺;但測(cè)試過程中,從未發(fā)現(xiàn)芯片有因此器件失效的現(xiàn)象,是因?yàn)槊虖腃lamp泄放掉還是短時(shí)毛刺器件不會(huì)損傷呢,Clamp使用GRNMOS。上管是p管,ESD2000V是pass的,器件用的5V,仿真最大有8V。

冰*:上管如果是PMOS不一定會(huì)死,PMOS沒有Snapback特性,不過ESD倒很可能掛。應(yīng)該是沒超過Vtrigger吧。5V器件BV一般有11V以上的,沒到trigger點(diǎn)。

Answer:仿真提示超耐壓應(yīng)該是指超了PDK提供的耐壓,但是是不是器件真實(shí)的耐壓不確定,擊穿通常有一定的余量。要結(jié)合電路結(jié)構(gòu)來分析,最好查foundry的PCM數(shù)據(jù)。

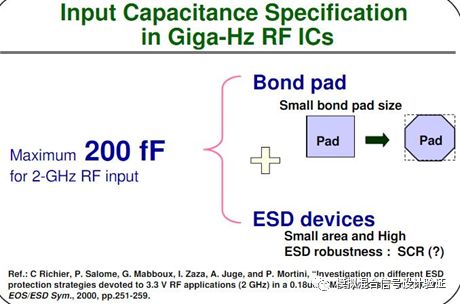

Q*:高速IO的ESD,如果想做8k HBM,你們能做成的ESD的寄生電容最小能達(dá)到多少?300fF?200fF?用于10Gbps的傳輸。

Answer:很抱歉我沒有專門做這種器件,主要還是串聯(lián)二極管,有文獻(xiàn)說明針對(duì)2GHz的高頻端口,可承受的最大寄生電容是200fF。

-

芯片

+關(guān)注

關(guān)注

459文章

52199瀏覽量

436386 -

集成電路

+關(guān)注

關(guān)注

5420文章

11955瀏覽量

367217 -

電路

+關(guān)注

關(guān)注

173文章

6022瀏覽量

174474 -

ESD

+關(guān)注

關(guān)注

49文章

2267瀏覽量

175166

原文標(biāo)題:ADV第十四講課程紀(jì)要 | 談?wù)劶呻娐稥SD保護(hù)的器件和電路

文章出處:【微信號(hào):yaliDV,微信公眾號(hào):模擬混合信號(hào)設(shè)計(jì)驗(yàn)證】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

集成電路繼電保護(hù)(基本電路,距離保護(hù),高頻保護(hù),發(fā)電機(jī)失磁保護(hù),接地保護(hù))

新型互補(bǔ)電容耦合ESD保護(hù)電路的設(shè)計(jì)

如何設(shè)計(jì)ESD保護(hù)電路?

在I/O電路中ESD保護(hù)結(jié)構(gòu)的設(shè)計(jì)要求

如何進(jìn)行雙極型集成電路的ESD保護(hù)?

雙極型集成電路的ESD保護(hù)

ESD引起集成電路損壞原理模式及實(shí)例

集成電路元器件基礎(chǔ)及應(yīng)用

HFTA-16.0:雙極型集成電路的ESD保護(hù)

在靜電保護(hù)電路設(shè)計(jì)中的ESD器件選型

談?wù)劶呻娐稥SD保護(hù)的器件和電路

談?wù)劶呻娐稥SD保護(hù)的器件和電路

評(píng)論