在做項目的過程中,經常遇到乘法計算,乘法器的設計就尤為重要。乘法器決定了最終電路功能能否實現,資源使用量多少以及時序性能優劣等。

乘法計算中,通常會使用 “*” 或者設計乘法器實現。

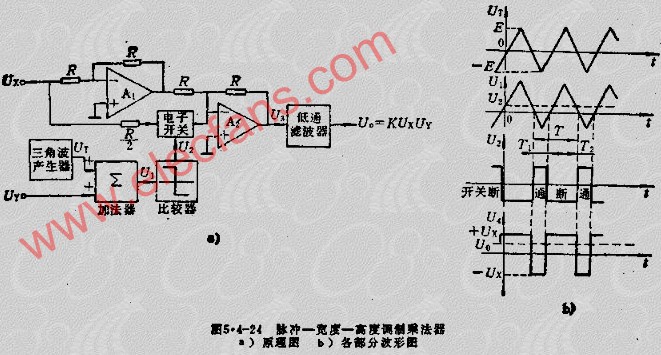

設計乘法器時,通常使用加法樹乘法器,實現流程圖如下:

如a[3:0]與b[3:0]乘法器設計,與分布式算法類似,a*b乘法計算設計如下:a*b[0]<<0 + a*b[1]<<1 + a*b[2]<<2 + a*b[3]<<3,通過移位和加法運算實現最終功能。結構框圖如上。

設計中,上述邏輯存在大量組合邏輯,延時大,當時序要求不高的情況下,可以使用,當時序要求很高時,此電路會產生時序違規。要想提高電路時序性能,需要在x、y、z三處選一處、兩處或者三處加入觸發器流水邏輯,提高電路時序性能,但其結果會使輸出延遲幾個時鐘周期,設計時應該考慮這一情況。

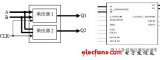

當使用 “*” 做乘法運算時,一般綜合工具都會直接調用FPGA片上集成的硬核乘法器,而不再使用邏輯單元搭建乘法器。設計結構圖如下:

為利用FPGA片上乘法器實現最終乘法。為了提高時序性能,可在w處加入寄存器流水線。

上述設計速度明顯優于第一種設計,但會消耗大量的片上硬核乘法器。

上述兩種設計各有其優勢,在使用中請根據實際設計電路采用合理的方案。

在前述文章中,設計FFT和IFFT,乘法設計采用第二種方案,提高電路速度。如果采用第一種方案,將會增加流水線程度,增大FFT以及IFFT的計算周期。

而在簡單和低速的乘法計算中使用第一種方案是一種比較良好的選擇。

-

FPGA

+關注

關注

1643文章

21952瀏覽量

613789 -

乘法器

+關注

關注

9文章

211瀏覽量

37796

原文標題:淺談乘法器的用法

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

怎么設計基于FPGA的WALLACETREE乘法器?

模擬乘法器AD834的原理與應用

乘法器對數運算電路應用

脈沖-寬度-高度調制乘法器

基于IP核的乘法器設計

基于CMOS工藝下的Gillbert單元乘法器的研究

使用verilogHDL實現乘法器

乘法器原理_乘法器的作用

采用Gillbert單元如何實現CMOS模擬乘法器的應用設計

乘法器的使用方法你知道哪些?

乘法器的使用方法你知道哪些?

評論