設(shè)計(jì)背景:

ROM是只讀存儲(chǔ)器(Read-Only Memory)的簡(jiǎn)稱,是一種只能讀出事先所存數(shù)據(jù)的固態(tài)半導(dǎo)體存儲(chǔ)器。其特性是一旦儲(chǔ)存資料就無(wú)法再將之改變或刪除。通常用在不需經(jīng)常變更資料的電子或電腦系統(tǒng)中,并且資料不會(huì)因?yàn)?a target="_blank">電源關(guān)閉而消失。

ROM是由英文Read only Memory的首字母構(gòu)成的,意為只讀存儲(chǔ)器。顧名思義,就是這樣的存儲(chǔ)器只能讀,不能像RAM一樣可以隨時(shí)讀和寫。它只允許在生產(chǎn)出來(lái)之后有一次寫的機(jī)會(huì),數(shù)據(jù)一旦寫入則不可更改。它另外一個(gè)特點(diǎn)是存儲(chǔ)器掉電后里面的數(shù)據(jù)不丟失,可以存放成百上千年。此類存儲(chǔ)器多用來(lái)存放固件,比如計(jì)算機(jī)啟動(dòng)的引導(dǎo)程序,手機(jī)、MP3、MP4、數(shù)碼相機(jī)等一些電子產(chǎn)品的相應(yīng)的程序代碼。

設(shè)計(jì)原理:

我們的設(shè)計(jì)是讀ROM的數(shù)據(jù),然后讀到最后一個(gè)數(shù)據(jù)的時(shí)候,然后又從最后的地址往回讀數(shù)據(jù),來(lái)實(shí)現(xiàn)循環(huán)讀數(shù)。

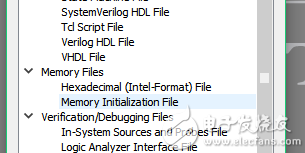

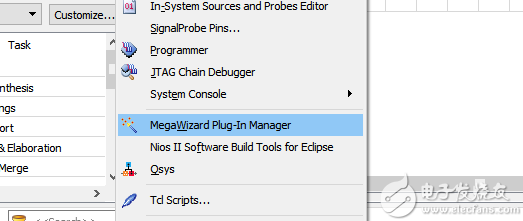

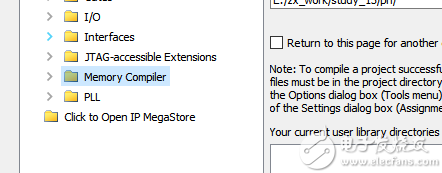

首先我們先創(chuàng)建一個(gè).mif文件,然后給對(duì)應(yīng)的地址中寫如數(shù)據(jù),然后設(shè)計(jì)一個(gè)IP核,之后通過(guò)讀ROM的地址,來(lái)讀出ROM中存在的數(shù)據(jù),具體的操作如下面的操作。

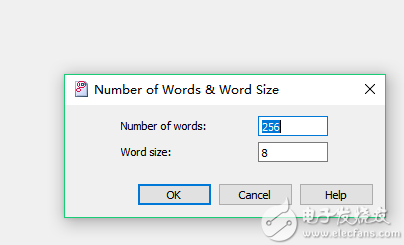

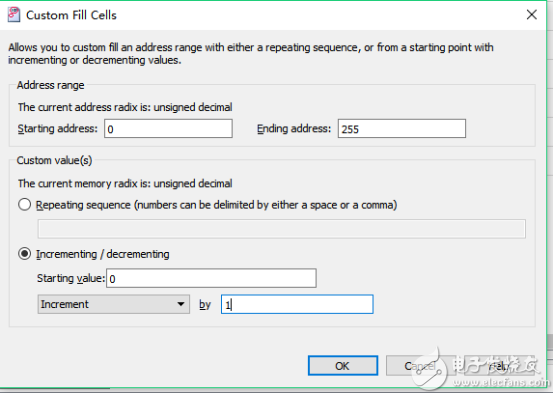

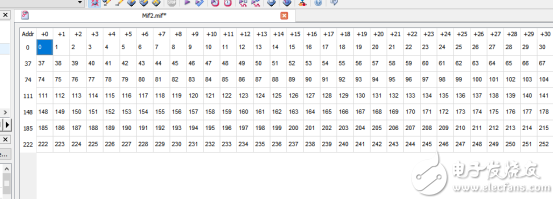

下一步,建立一個(gè)深度256,位寬為8的 .mif。

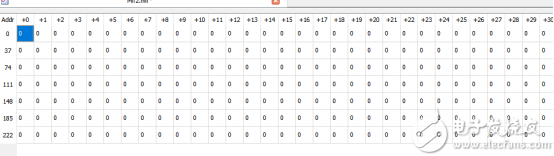

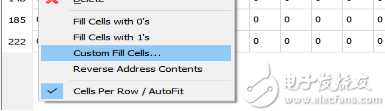

然后在第一個(gè)地址右鍵。

填寫開始地址以及結(jié)束地址,我們給每一位的地址位寫上和地址一樣的數(shù)據(jù),那么就是數(shù)據(jù)從0開始,步進(jìn)為1,如下,然后然后完成,保存。

這樣我們寫好我們.mif文件,然后進(jìn)行下面的步驟。

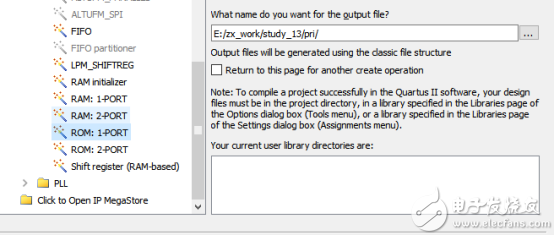

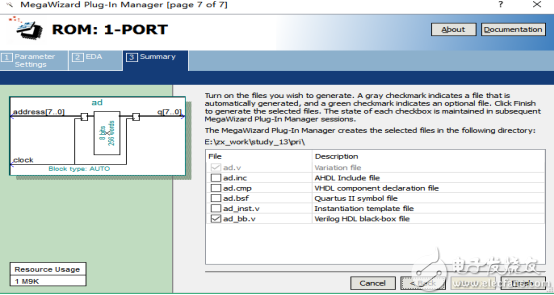

選擇我們所選的硬件描述語(yǔ)言,我們都是verilog HDL,然后選擇我們文件生成的路徑,下一步。

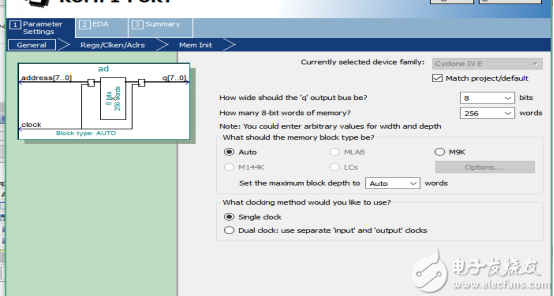

設(shè)置我們的輸出的位寬,和深度,我們的深度256,位寬8,下一步。

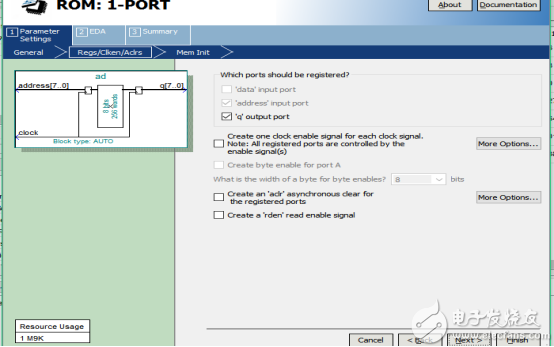

去掉輸出是否有寄存器的對(duì)勾,如果選了輸出會(huì)晚一拍,因?yàn)榧恿艘粋€(gè)輸出寄存器。

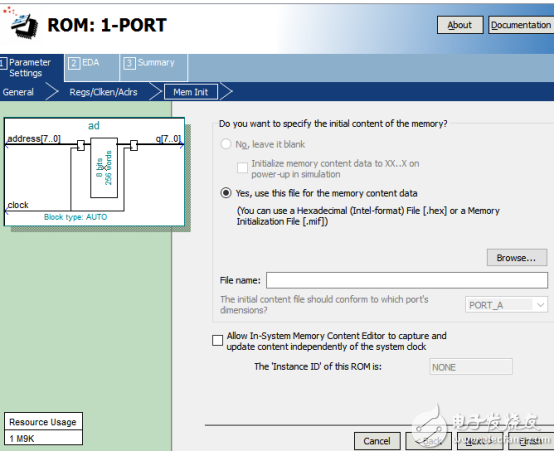

然后出現(xiàn)下面的界面,點(diǎn)擊 ,選擇我們生成的.mif文件,添加進(jìn)來(lái),然后下一步,下一步完成。

,選擇我們生成的.mif文件,添加進(jìn)來(lái),然后下一步,下一步完成。

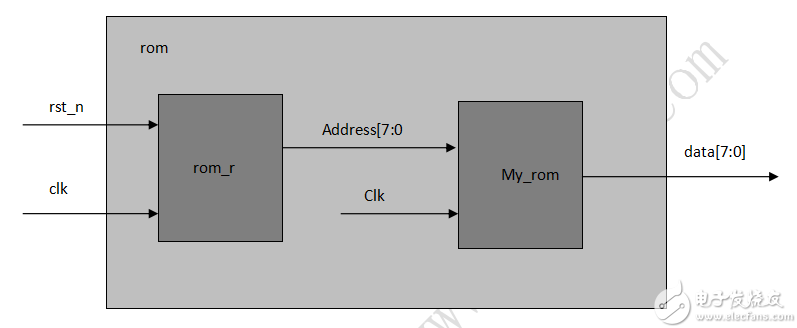

設(shè)計(jì)架構(gòu)圖:

設(shè)計(jì)代碼:

頂層模塊

0modulerom(clk,rst_n,data);

1 inputclk;

2 inputrst_n;

3

4 output[7:0]data;

5

6 wire[7:0]address;

7

8 rom_r rom_r ( //例化ROM控制器模塊

9 .clk(clk),

10 .rst_n(rst_n),

11 .address(address)

12 );

13

14 my_rom my_rom_inst (//例化IP核模塊

15 .address (address ),

16 .clock (clk ),

17 .q (data )

18 );

19

20endmodule

設(shè)計(jì)模塊

0modulerom_r(clk,rst_n,address);

1

2 inputclk;

3 inputrst_n;

4

5 outputreg[7:0]address;

6

7 reg[1:0]state;

8 always@(posedgeclk ornegedgerst_n)

9 if(!rst_n)

10 begin

11 address <=?1'b0;

12 state <=?1'b0;

13 end

14 else

15 begin

16 case(state)

17 0:begin

18 if(address

19 begin

20 address <=?address +?1'b1;?//地址激增

21 end

22 else

23 begin

24 if(address ==255)//判斷是否讀完

25 begin

26 address <=?address -?1'b1;?

27 state <=?1;

28 end

29

30 end

31 end

32 1:begin

33 if(address >0)//讀完就跳轉(zhuǎn)一狀態(tài)后讓地址減1

34 begin

35 address <=?address -?1'b1;

36 end

37 else

38 begin

39 address <=?address +?1'b1;

40 state <=?0;

41 end

42 end

43 default:state <=?0;

44 endcase

45 end

46endmodule

測(cè)試模塊

0`timescale1ns/1ps

1

2modulerom_tb();

3

4 regclk;

5 regrst_n;

6

7 wire[7:0]data;

8

9 initialbegin

10 clk =1'b1;

11 rst_n =1'b0;

12

13 #100.1rst_n =1'b1;

14

15 #20000$stop;//20000NS后停止仿真

16

17 end

18

19 always#10clk =~clk;//產(chǎn)生50M時(shí)鐘

20

21 rom rom_dut ( //例化頂層模塊

22 .clk(clk),

23 .rst_n(rst_n),

24 .data(data)

25 );

26endmodule

仿真圖:

仿真中我們可以看到和我們的設(shè)計(jì)一樣,我們先從0地址讀數(shù)據(jù),當(dāng)讀到最后一個(gè)數(shù)后,然后返回來(lái)從最后一個(gè)地址開始讀數(shù)。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21967瀏覽量

614188

發(fā)布評(píng)論請(qǐng)先 登錄

至芯昭哥帶你學(xué)FPGA之FPGA_100天之旅_rom控制器的設(shè)計(jì)

FPGA零基礎(chǔ)學(xué)習(xí):IP CORE 之 ROM設(shè)計(jì)

基于DSP與FPGA的運(yùn)動(dòng)控制器研究

基于XILINX的XC3系列FPGA的VGA控制器的VHDL源程

基于FPGA的LED屏控制器設(shè)計(jì)

基于FPGA的VGA圖像控制器的設(shè)計(jì)與實(shí)現(xiàn)

高性能16位XA微控制器系列

Virtex-7 FPGA系列的內(nèi)存控制器介紹

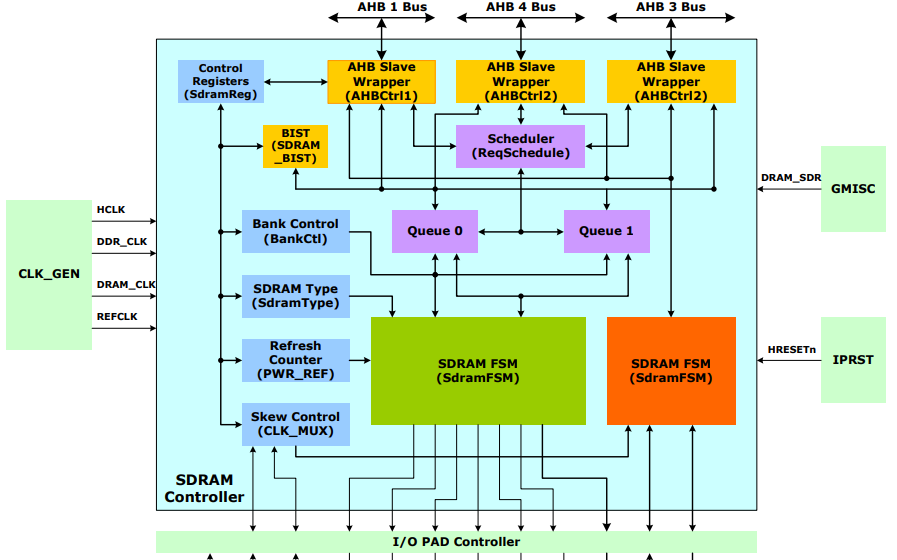

學(xué)習(xí)SDRAM控制器設(shè)計(jì) 能讓你掌握很多FPGA知識(shí)

NUC970工業(yè)控制系列微控制器的數(shù)據(jù)手冊(cè)免費(fèi)下載

如何使用FPGA內(nèi)部的ROM以及程序?qū)υ?b class='flag-5'>ROM的數(shù)據(jù)讀操作

AN5354_STM32H7系列微控制器16位ADC的應(yīng)用手冊(cè)

FPGA學(xué)習(xí)筆記:ROM IP核的使用方法

FPGA學(xué)習(xí)系列:16. rom控制器設(shè)計(jì)

FPGA學(xué)習(xí)系列:16. rom控制器設(shè)計(jì)

評(píng)論