半導體傳統(tǒng)封裝與先進封裝的分類及特點

一、傳統(tǒng)封裝技術(shù)(成熟工藝,結(jié)構(gòu)相對簡單)

1、雙列直插封裝(DIP,Dual In-line Package)

?特點:引腳從封裝兩側(cè)直插而出,便于手工焊接和維修,成本低;但引腳間距大(如 2.54mm),集成度低,占用 PCB 面積大。

?應(yīng)用:早期邏輯芯片、存儲器、中小規(guī)模集成電路。

2、小外形封裝(SOP,Small Outline Package)

?特點:封裝體薄,引腳呈 “L” 型向外延伸,體積比 DIP 小,引腳間距縮小至 1.27mm 或更小,集成度提升。

?衍生類型:

?薄型小外形封裝(TSOP,Thin SOP):厚度更薄,適用于內(nèi)存芯片(如 DRAM)。

?收縮型小外形封裝(SSOP,Shrink SOP):引腳間距更小(如 0.65mm),進一步縮小體積。

3、四面貼裝封裝(QFP,Quad Flat Package)

?特點:四邊均有引腳,呈 “翼型” 向外展開,引腳數(shù)量可達數(shù)百個,集成度較高,適用于高性能芯片。

?衍生類型:

?薄型 QFP(TQFP):厚度減薄至 1.0mm 以下。

?塑料 QFP(PQFP):采用塑料封裝,成本更低。

?應(yīng)用:早期微處理器、ASIC 芯片、數(shù)字信號處理器(DSP)。

4、針柵陣列封裝(PGA,Pin Grid Array)

?特點:引腳以陣列形式分布在封裝底部,呈針狀插入 PCB 插座,引腳數(shù)量多(如數(shù)百至數(shù)千),散熱和電氣性能較好。

?應(yīng)用:早期高性能處理器(如 Intel Pentium 系列)、大型計算機芯片。

真空壓力除泡系統(tǒng)

二、先進封裝技術(shù)(高集成度、三維互連、異構(gòu)集成)

1、倒裝芯片封裝(Flip-Chip)

?特點:芯片面朝下,通過凸點(Bump)直接焊接到基板上,互連距離短,信號傳輸速度快,熱性能好,集成密度高。

?關(guān)鍵工藝:底部填充(Underfill)用于緩解芯片與基板的熱應(yīng)力差異,提高可靠性。

?應(yīng)用:高端處理器(如 CPU、GPU)、射頻芯片、圖像傳感器。

2、球柵陣列封裝(BGA,Ball Grid Array)

?特點:封裝底部以焊球陣列代替引腳,焊點分布更均勻,可承載更多 I/O 接口,電路板布局密度高,信號完整性好。

?衍生類型:

?倒裝 BGA(FC-BGA):結(jié)合倒裝芯片技術(shù),進一步縮短互連距離。

?陶瓷 BGA(CBGA):散熱性能優(yōu)異,適用于高可靠性場景。

?應(yīng)用:智能手機處理器、網(wǎng)絡(luò)芯片、FPGA。

3、晶圓級封裝(WLP,Wafer Level Package)

?特點:在晶圓切割前完成封裝,封裝尺寸與芯片尺寸接近(Fan-in WLP)或超出(Fan-out WLP),實現(xiàn) “芯片即封裝”,成本低、體積小。

?類型:

?扇入型 WLP(Fan-in WLP):封裝尺寸≤芯片尺寸,適用于 I/O 較少的芯片(如傳感器、射頻芯片)。

?扇出型 WLP(Fan-out WLP):通過重布線技術(shù)擴展 I/O,封裝尺寸 > 芯片尺寸,適用于邏輯芯片、存儲器。

4、三維封裝(3D Packaging)

?特點:通過垂直堆疊芯片,利用 TSV(硅通孔)、微凸點等技術(shù)實現(xiàn)層間互連,集成度極高,功耗和延遲降低。

?類型:

?芯片堆疊(Chip Stacking):同類型芯片堆疊(如存儲器堆疊)。

?混合鍵合(Hybrid Bonding):結(jié)合銅 - 銅鍵合與介質(zhì)鍵合,實現(xiàn)高密度互連。

?應(yīng)用:高帶寬存儲器(HBM)、AI 芯片、圖像處理芯片。

5、系統(tǒng)級封裝(SiP,System in Package)

?特點:在單一封裝內(nèi)集成多個芯片(如 CPU、GPU、存儲器、射頻芯片等)和無源器件,實現(xiàn)系統(tǒng)級功能,減小整機體積。

?技術(shù)亮點:異構(gòu)集成(不同工藝芯片混合封裝)、埋置技術(shù)(將芯片嵌入基板)。

?應(yīng)用:物聯(lián)網(wǎng)模塊、穿戴設(shè)備芯片、汽車電子控制單元(ECU)。

6、Chiplet(芯粒)封裝

?特點:將復(fù)雜芯片拆分為多個功能模塊(芯粒),通過先進封裝技術(shù)(如 EMIB、CoWoS)互連,降低設(shè)計成本,提升良率。

?應(yīng)用:高性能計算芯片(如 AMD EPYC、Intel Xeon)、AI 加速器。

7、2.5D 封裝

?特點:通過中介層(Interposer)連接多個芯片,實現(xiàn)水平方向高密度互連,典型如 TSMC CoWoS(Chip on Wafer on Substrate)、Intel EMIB(Embedded Multi-die Interconnect Bridge)。

?應(yīng)用:高端 AI 芯片、數(shù)據(jù)中心 GPU(如 NVIDIA H100、AMD MI300)。

晶圓級真空貼壓膜系統(tǒng)

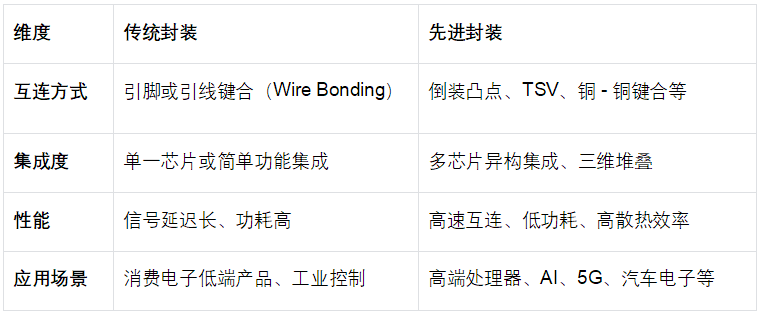

三、傳統(tǒng)封裝與先進封裝的核心區(qū)別

先進封裝通過三維結(jié)構(gòu)、異構(gòu)集成和高密度互連技術(shù),突破了傳統(tǒng)封裝在性能和集成度上的限制,成為半導體行業(yè)應(yīng)對 “摩爾定律放緩” 的關(guān)鍵技術(shù)方向。

審核編輯 黃宇

-

半導體

+關(guān)注

關(guān)注

335文章

29017瀏覽量

239644 -

先進封裝

+關(guān)注

關(guān)注

2文章

478瀏覽量

659

發(fā)布評論請先 登錄

瑞沃微先進封裝:突破摩爾定律枷鎖,助力半導體新飛躍

芯和半導體將參加重慶半導體制造與先進封測產(chǎn)業(yè)發(fā)展論壇

半導體封裝的主要類型和制造方法

傳統(tǒng)封裝你了解多少,小白快捷學習 | 第1集 #傳統(tǒng)封裝 #先進封裝 #芯片封裝 #華芯邦 #

技術(shù)前沿:半導體先進封裝從2D到3D的關(guān)鍵

倒裝封裝(Flip Chip)工藝:半導體封裝的璀璨明星!

先進封裝技術(shù)推動半導體行業(yè)繼續(xù)前行的關(guān)鍵力量

人工智能半導體及先進封裝技術(shù)發(fā)展趨勢

先進封裝的技術(shù)趨勢

先進封裝技術(shù)的類型簡述

半導體封裝技術(shù)的類型和區(qū)別

led封裝和半導體封裝的區(qū)別

晶圓廠與封測廠攜手,共筑先進封裝新未來

半導體封裝材料全解析:分類、應(yīng)用與發(fā)展趨勢!

半導體傳統(tǒng)封裝與先進封裝的對比與發(fā)展

半導體傳統(tǒng)封裝與先進封裝的對比與發(fā)展

評論