AI 時代的數據洪流與算力瓶頸

從日常生活中的語音助手和自動駕駛,到工業上的全自動工廠和 AI 輔助設計,人工智能技術正在為我們的世界帶來革命性的變化。在人工智能的應用中,無論是文字、語音、還是視頻,都需要被轉化為一串串的基本的數據單元,以供 AI 處理器識別并進行運算處理。這些單元被稱之為 token。

現代的 AI 系統往往要面臨同時產生的海量 token 輸入,并且需要在一秒內完成十億甚至百億數量級的 token 處理。這種高并發、高帶寬的需求對計算機架構和芯片的設計提出的新的挑戰:在搭載于傳統的二維芯片上,尤其是使用馮·諾伊曼結構的計算機中,處理器與內存之間的總線好比鄉間雙向二車道的小路,數據傳輸速率和帶寬十分有限,已經遠不能承載 AI 時代的數據洪流。數據顯示,當前 AI 芯片的算力利用率通常低于 30%,其主要原因正是處理器與內存之間數據傳輸速率與帶寬跟不上處理器的運算速度。這種被稱為“內存墻”的現象已經成為了限制 AI 系統性能的瓶頸。

3D-IC——突破維度的技術革命

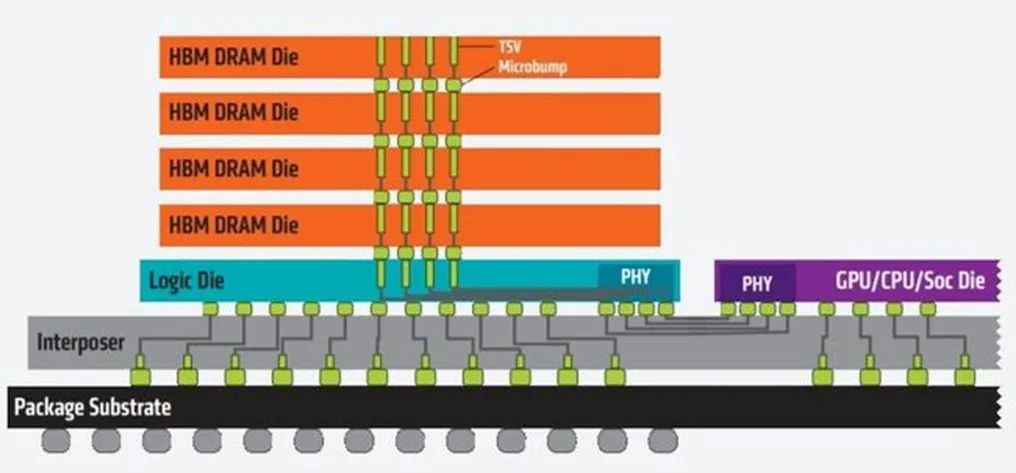

為了解決“內存墻”對 AI 系統的桎梏,當今主流的 AI 芯片大多采用了2.5D 的方式設計制造。2.5D 就是將存儲和運算芯片擺放在同一平面上,借助平面下方的中介層傳輸芯片來實現千和萬數量級的連接,初步解決了存儲和運算之間數據通路擁塞的問題。

此外,將傳統的大芯片切分為更小的存儲和運算芯片后,良品率也能得以大幅提升。但如果要滿足更嚴苛的高并發、高帶寬的需求,我們就需要升級到 3D 的設計,將存儲芯片直接堆疊在運算芯片之上。

在 3D-IC 的工藝中,金屬微凸塊(micro bump)或復合鍵(hybrid bonding)可以將上下堆疊的兩個芯片直接連接。如有信號需要穿過整層芯片,則可以通過硅通孔(TSV)穿過芯片的硅襯底、器件層、甚至金屬層。3D-IC 結構下的芯片間垂直互連進一步縮短了數據傳輸距離,從而提高了數據傳輸速率,減小了傳輸功耗。由于芯片的整個接觸面都可以擺放連接接口,芯片間并行連接的數量得以有極大的增加,帶寬可由此得到若干個數量級的提高。以上將內存和運算放在一起的結構被稱為近存運算,是當前打破“內存墻”的重要手段。

最先進的芯片設計者甚至會在面對不同運算需求時,平衡運算性能和設計制造成本,同時采用 2.5D 和 3D 的連接技術,即 3.5D 芯片。3.5D 的設計可以更好地支持異構運算以及處理海量數據。

Cadence Integrity 3D-IC——全流程設計平臺

3D-IC 的設計不同于傳統的封裝設計和芯片設計,需要創新的設計方法學和工具的支持。傳統的先進封裝流程會先由封裝決定每個芯粒的接口,之后將設計目標拆分給芯片設計團隊。然而這樣的流程無法實現跨芯片、芯片與封裝之間的系統級優化。3D-IC 的設計需要把傳統 2D 芯片中的性能、功耗、面積、成本(PPAC)指標驅動的設計拓展到整個 3D 系統中。

Cadence 致力于提供軟件、硬件和 IP 產品,助力電子設計概念稱為現實。基于此,Cadence 率先推出了能在在單一平臺上實現 3D-IC 全流程的 EDA 軟件——Integrity 3D-IC,給業界提供了一套完整的 3D-IC 解決方案。該方案支持所有 3D-IC 設計類型和各種工藝節點,并讓 3D-IC 設計的各個部門通過 Cadence 的數字設計平臺Innovus、模擬及定制化設計平臺Virtuoso和封裝與板級設計平臺Allegro實現全系統跨平臺的無縫協作。為了達到更好的 3D 系統的設計效果,Integrity 3D-IC 將 3D-IC 的設計流程拆分為:

早期架構探索– 探索分析不同的 3D 堆疊架構,快速進行方案迭代。優化 bump 和 TSV 的規劃與擺放。

中期設計實現– 3D 系統的 partition 與floorplanning,3D placement、CTS、routing 及優化,跨芯片的靜態時序分析與收斂。

后期多物理場簽核– 包括對 3D-IC 簽核至關重要的系統級熱分析、電源分配網絡分析,3D 系統的信號完整性與電源完整性,3D 靜態時序分析等多物理場的簽核,系統級的 LVS 和 DRC。

從而使 3D-IC 芯片的堆疊、互聯以及各芯粒都能根據全系統 PPAC 的最優或次優解完成規劃與實現,讓芯片公司設計出更有競爭力的 3D-IC 產品。

未來展望:3.5D 異構集成時代

在半導體產業邁向新征程的關鍵節點,Cadence 始終以創新者的姿態深耕行業前沿。面向未來,Cadence 滿懷熱忱與期待,愿與行業合作伙伴同心同行,共同推動下一代 3.5D 的技術創新。這不僅是技術參數上的迭代升級,更是對芯片設計方法學的深度重塑,力求為行業發展注入新動能。

Unleash your imagination,與 Cadence攜手,將創意變成現實!

-

芯片

+關注

關注

460文章

52568瀏覽量

441979 -

IC

+關注

關注

36文章

6134瀏覽量

179717 -

Cadence

+關注

關注

67文章

977瀏覽量

144527 -

AI

+關注

關注

88文章

35319瀏覽量

280777

原文標題:破局 AI 算力困局:3D-IC 技術架構的顛覆性變革

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

“四算合一”算力平臺,芯片國產化率超九成,兼容8種國產AI芯片

Cadence攜手臺積公司,推出經過其A16和N2P工藝技術認證的設計解決方案,推動 AI 和 3D-IC芯片設計發展

摩爾線程與AI算力平臺AutoDL達成深度合作

DeepSeek推動AI算力需求:800G光模塊的關鍵作用

基于TSV的3D-IC關鍵集成技術

Cadence Integrity 3D-IC平臺解決AI算力困局

Cadence Integrity 3D-IC平臺解決AI算力困局

評論