差分晶振在高速 FPGA 設計中具有非常重要的應用,尤其是在對時鐘精度、抗干擾能力、信號完整性要求高的系統中,比如:

· 高速串行接口(PCIe、SFP+/QSFP、10G Ethernet、DDR4/DDR5)

· 多通道數據采集系

· 高速通信系統(SerDes)

一、什么是差分晶振?

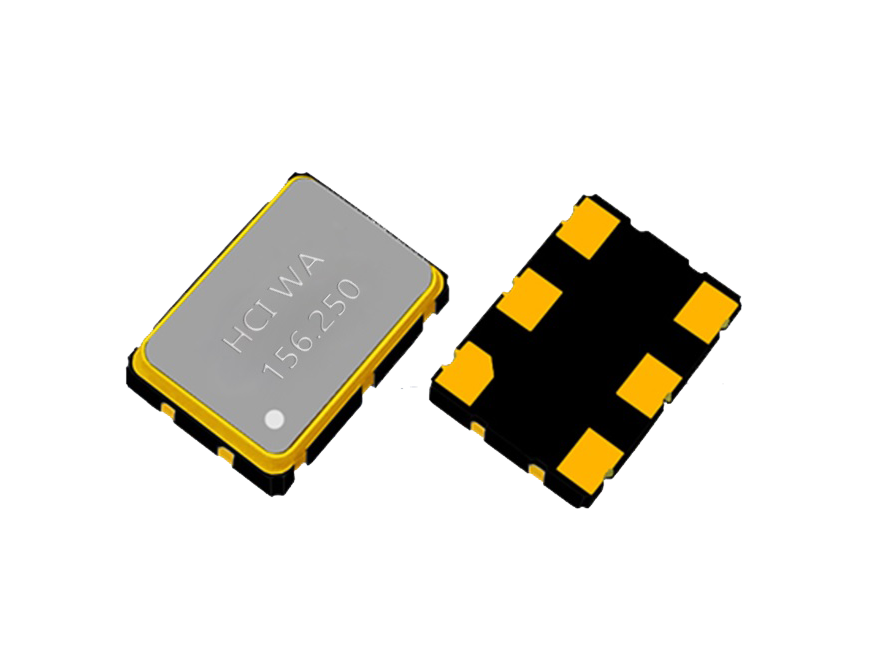

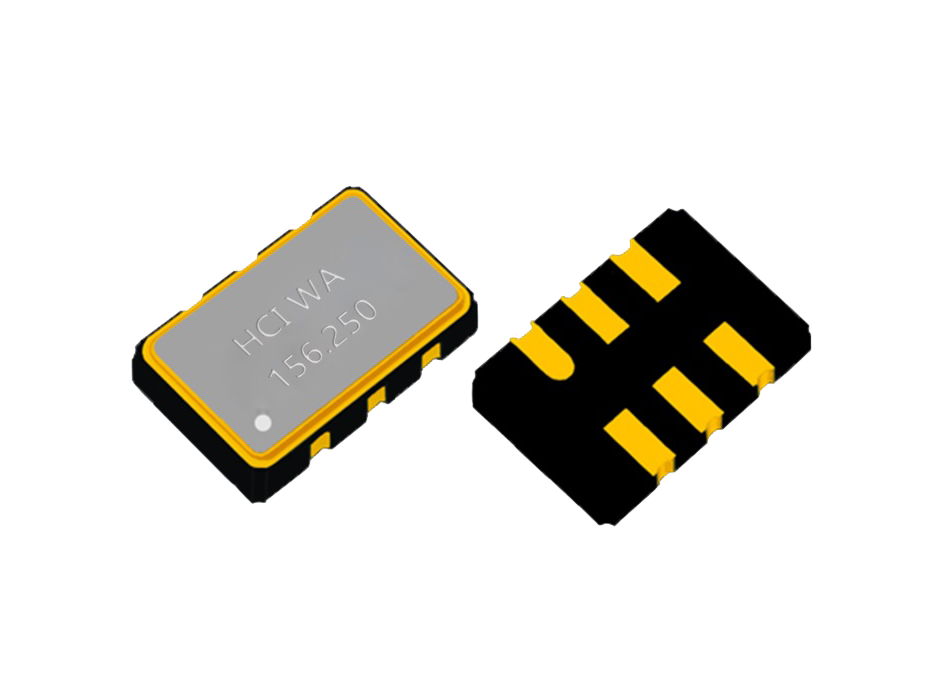

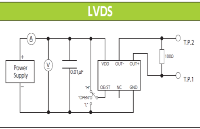

差分晶振(Differential Oscillator)是一種輸出差分信號(如 LVDS、LVPECL、HCSL)的有源晶體振蕩器,其輸出兩個互為反相的時鐘信號(CLK+ 和 CLK?)。它不同于傳統的單端晶振(如 CMOS 輸出的 Oscillator)。

二、差分信號的優勢:

| 特性 | 差分信號 | 單端信號 |

|---|---|---|

| 抗干擾能力 | 強(共模噪聲抵消) | 弱 |

| 信號完整性 | 好,易于傳輸高速信號 | 差 |

| 驅動能力 | 高,適合遠距離/高速傳輸 | 低 |

| 抖動性能 | 更低 | 相對較高 |

三、差分晶振在高速 FPGA 上的應用

1. 作為高速接口參考時鐘

PCIe、10G/25G Ethernet、SATA 等高速接口必須使用差分參考時鐘;

通常使用 100 MHz 或 156.25 MHz 差分晶振(如 HCSL/LVDS 輸出);

FPGA 內部的 GTX/GTH/GTP 等高速收發器模塊(Transceivers) 需要這些差分參考時鐘。

典型連接:

差分晶振 → FPGA GTREFCLK0/1 (高速收發器參考時鐘引腳)

2. 時鐘樹的核心時鐘源

多通道高速系統中,使用差分晶振驅動一個時鐘分配芯片(如 SI5341/AD9528),再輸出多個同步時鐘;

適用于多 ADC、DAC、FPGA 通信時鐘對齊。

結構示意:

差分晶振 → 時鐘管理芯片 (如 PLL / Fanout Buffer)

↓

多個同步時鐘→ FPGA/ADC/DAC

3. 驅動 FPGA 內部 PLL/MMCM

差分晶振可用于提供高品質時鐘輸入(如通過 IBUFDS 接口進入 FPGA),再由內部 PLL/MMCM 輸出系統各模塊時鐘;提升時鐘質量,降低整體系統時鐘抖動。

常見差分輸出類型與 FPGA 兼容性

| 輸出類型 | 典型應用 | FPGA 接口兼容性 |

|---|---|---|

| LVDS | 通用差分晶振輸出類型 | 所有主流FPGA 支持(GTX/GTH 輸入) |

| HCSL | PCIe、服務器主板用 | 直接支持(如Xilinx PCIe IP 核) |

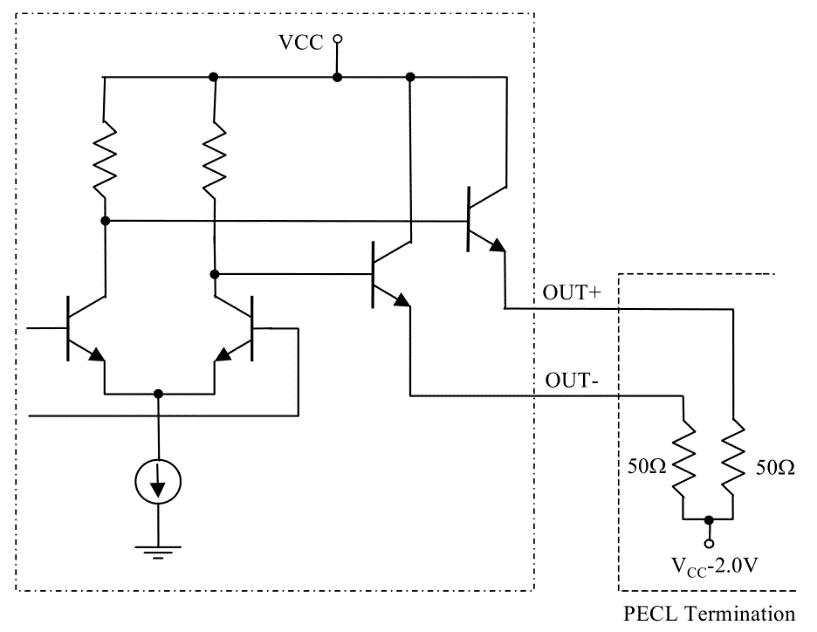

| LVPECL | 高頻、高擺幅應用 | 需要外部終端匹配和偏置電阻 |

| CML | 超高速鏈路(>10 Gbps) | 高端FPGA 收發器支持 |

? 建議根據 FPGA 廠商推薦使用匹配的差分輸出類型。

四、差分晶振選型建議

| 參數 | 建議值 |

|---|---|

| 頻率穩定度 | ±25 ppm 或更優 |

| 相位抖動(12kHz–20MHz) | < 1ps RMS(高速接口要求) |

| 輸出類型 | LVDS/HCSL 優先,取決于 FPGA 兼容性 |

| 負載能力 | 驅動能力≥ 15pF 或與時鐘芯片匹配 |

| 溫度范圍 | 工業級(-40°C ~ +85°C)或更寬 |

優先選擇協議推薦頻率:

PCIe:100 MHz;

SFP+/10G Ethernet:156.25 MHz;

25G/40G Ethernet:312.5 MHz;

JESD204B/C:250 MHz、312.5 MHz、625 MHz 等。

參考 FPGA 官方文檔推薦時鐘范圍;

抖動指標要低:

特別重要于 PCIe、JESD204C、10G/25G Ethernet。

五、差分晶振在高速 FPGA 上的常用頻率

| 頻率(MHz) | 應用場景 | 備注 |

|---|---|---|

| 100 MHz | PCIe Gen1/Gen2;通用高速邏輯系統 | 非常常見,支持HCSL/LVDS |

| 125 MHz | Gigabit Ethernet(千兆網) | 適用于GMII、SGMII 等接口 |

| 156.25 MHz | 10G Ethernet(10GBASE-R/XAUI)、SFP+、QSFP、CEI 接口等 | 高速串行通信標準頻率 |

| 200 MHz | DDR4 時鐘、多速率收發器參考頻率 | 通常用于倍頻生成更高時鐘 |

| 212.5 MHz | JESD204B/C 數據轉換鏈路 | 高頻采集通信接口標準頻率 |

| 250 MHz | 高速ADC/DAC 系統、部分 JESD204C 系統 | 抖動要求更嚴格 |

| 312.5 MHz | 25G Ethernet(25GBASE-R)、高速光通信系統 | 差分輸出常為CML/LVPECL |

| 322.265625 MHz | CPRI(6.144 Gbps)參考時鐘 | 通信基站FPGA 用 |

| 644.53125 MHz | CPRI(12.288 Gbps)、JESD204C 高速鏈路 | 極高速接口,需要極低抖動晶振 |

| Others(用戶自定義) | 特定頻率輸入給PLL,再生成目標頻率 | 需確認PLL 支持倍頻因子 |

? 具體型號建議聯系杭晶銷售或技術工程師推薦使用匹配的差分輸出類型。

六、總結

| 項目 | 差分晶振的優勢 |

|---|---|

| 精度 | 抖動低,頻率穩定 |

| 抗干擾 | 強,共模噪聲抑制好 |

| 速度 | 支持GHz 級高速傳輸 |

| 應用 | PCIe、SFP、DDR4/5、ADC、DAC、同步系統等 |

差分晶振在現代高速 FPGA 系統中幾乎是標配,是確保系統高速通信與同步性能的關鍵器件。

如果你有具體的 FPGA 型號 (如 Xilinx Zynq Ultrascale+、Intel Stratix 10)、差分晶振型號,或通信接口需求(如 PCIe Gen3/SFP+),蘇州杭晶可以幫你推薦最合適的時鐘配置方案與原理圖連接設計。

審核編輯 黃宇

-

FPGA

+關注

關注

1645文章

22040瀏覽量

618157 -

晶振

+關注

關注

35文章

3261瀏覽量

70089 -

差分晶振

+關注

關注

0文章

146瀏覽量

733

發布評論請先 登錄

一探究竟差分晶振

MG7050EAN存儲器6G應用晶振,X1M0004110020,EPSON差分晶振

愛普生差分晶振SG2520EGN(X1G005881)在高速光模塊通信中的應用

愛普生差分晶振SG2016EHN(X1G006141)在高速通信網絡中的應用

差分晶振在高速 FPGA 上的應用

差分晶振在高速 FPGA 上的應用

評論