ADS129x設備SPI 時鐘極性CPOL和時鐘相位 CPHA的正確設置

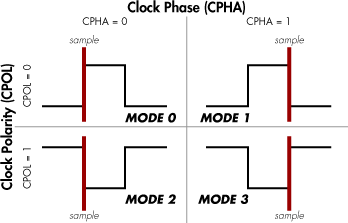

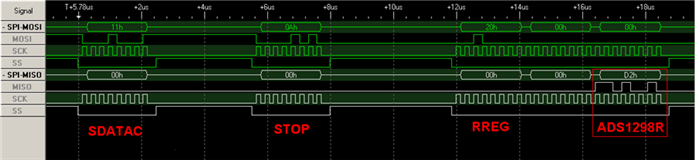

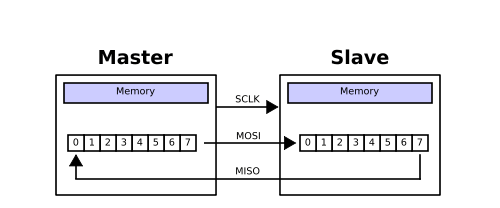

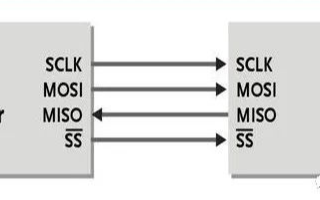

bio-potential系列中的大多數設備(除了ADS1293)都使用SPI Mode 1。這意味著時鐘極性(CPOL)=0,時鐘相位(CPHA)=1。主機MCU作為主控制器,ADS129x設備作為從機。SCLK的上升沿用于移動數據,下降沿用于鎖定數據。當我們不與從機通信時,我們希望SCLK空閑時在低電平。

ADS1293使用的接口與其他ADS129x系列不同。對于ADS1293,數據在SCLK下降沿改變,在上升沿鎖存。這對應于SPI Mode 0,這意味著CPOL=0和CPHA=0。

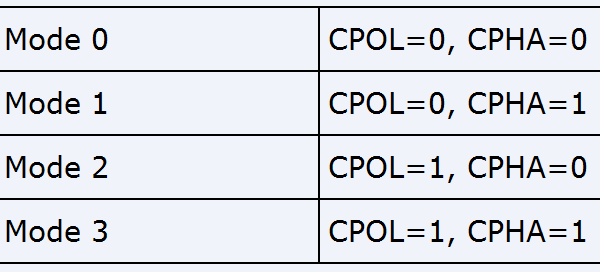

下圖總結了四種SPI模式,供您參考:

本方案適用于:

適用于:

ADS1191, ADS1192, ADS1291, ADS1292, ADS1292R,ADS1293, ADS1294, ADS1294R, ADS1296, ADS1296R, ADS1298, ADS1298R,ADS1299-4, ADS1299-6, and ADS1299.

TI ADS1299數據手冊免費下載

*附件:ads1299.pdf

TI ADS1299器件的應用手冊

*附件:ADC 中的數字濾波器類型.pdf

**ADS1299的 **EDA模型免費下載

http://www.asorrir.com/p/eda-t0-p0.html?title=ADS1299

-

ti

+關注

關注

113文章

8025瀏覽量

214470 -

時鐘

+關注

關注

11文章

1887瀏覽量

132933 -

SPI

+關注

關注

17文章

1786瀏覽量

94977 -

CPHA

+關注

關注

0文章

9瀏覽量

9498 -

ADS1299

+關注

關注

1文章

8瀏覽量

8457

發布評論請先 登錄

TI的ADS129x器件SPI 時鐘極性CPOL和時鐘相位 CPHA的正確設置模式

TI的ADS129x器件SPI 時鐘極性CPOL和時鐘相位 CPHA的正確設置模式

評論