1 實驗測量

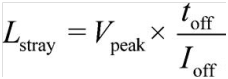

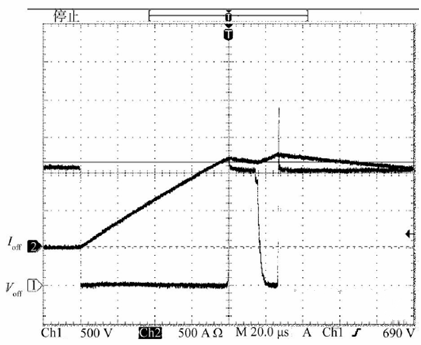

測量回路雜散電感常用方法有雙脈沖法、短路法及諧振法。雙脈沖法通過測量獲取IGBT關斷時的尖峰電壓Vpeak和電流變化率,利用公式來計算雜散電感Lstray;短路法通過測量IGBT短路開通時的下降電壓和電流變化率之比,經計算獲取Lstray值;諧振法通過測量靜態電路諧振頻率,再使用諧振公式求取Lstray值。實踐中,最常使用的測量方法是雙脈沖法。

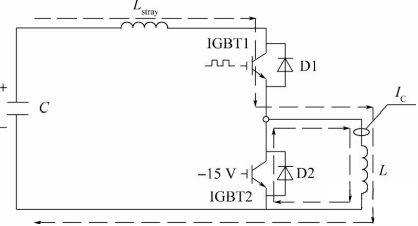

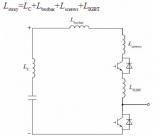

雙脈沖試驗的原理如圖1 所示,半橋電路的上管IGBT1 用于開關斬波;下管IGBT2 用于偏置,始終關斷。第一個導通脈沖信號使IGBT1 導通,直流電壓施于感性負載L,負載電流線性增長;當負載電流達到一定值時,IGBT1關斷,負載電流通過IGBT2的反并聯二極管D2 續流。經過一個時間間隔tp 后,第二個導通脈沖信號到來,IGBT1再次導通;當IGBT1達到最大關斷電流值Ioff 時,驅動器啟動過流保護電路,IGBT1 關斷保護,此時IGBT1 將承受由回路雜散電感Lstray 引起的過電壓Vpeak。

圖1 雙脈沖試驗原理圖

圖2 示出雙脈沖試驗波形。由圖可知,IGBT最大關斷電流Ioff=1 250 A,關斷尖峰電壓Vpeak=800 V,關斷時間toff=120 ns。回路雜散電感計算如下:

圖2 雙脈沖試驗波形圖

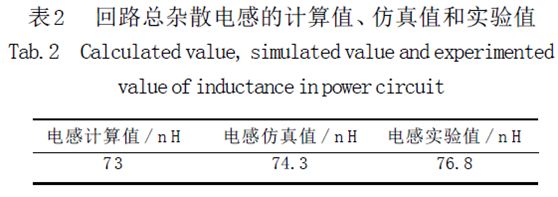

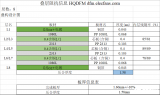

表2 示出回路總雜散電感的計算值、仿真值和實驗值,可以看出,三值非常相近。采用低感母排設計后,回路的雜散電感約為75 nH左右,而采用傳統母線連接的回路其寄生電感在200 nH以上。

2 低感母排的EMC 優化設計

電感值是低感母排EMC性能的重要指標。低電感和低阻抗特性可使系統獲得較好的噪聲抑制效果。在進行低感母排的EMC優化設計時應考慮以下幾點:

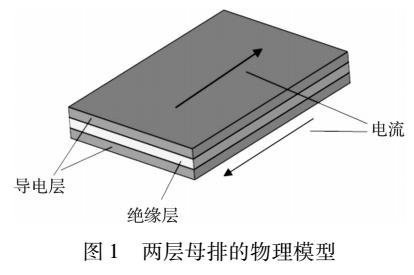

(1)母排結構

正、負母排應平行且重疊于絕緣層的兩側。有研究表明,1 c m2 的剩余環路面積累積的磁鏈會導致大約10 nH的雜散電感。平行且重疊的結構可使正、負母排電流路徑的重疊面積達到最大,電流剩余環路面積最小,由此產生的磁通空間分離最小。

(2)絕緣層厚度

電感值隨絕緣層厚度的減小而減小。理論上,正、負母排的間距越小,鏡像電流產生的磁鏈越能相互抵消,母排的雜散電感能得到充分抑制。

(3)母排寬度

母排阻抗隨母排寬度的增大而減小。母排越寬,高頻狀態下的集膚效應越顯著,正、負母排的鏡像電流等效地獲得了極小的剩余環路面積,從而使分布電感得到抑制。值得指出的是,如果正、負母排完全平行而沒有剩余環路,那么增加母排的寬度對電感變化影響將會很小。

(4)安裝孔位置

合理設計母排上電容器安裝孔的位置。連接電容器的直流母排應盡量采用對稱設計,開孔位置應使IGBT盡量靠近直流側支撐電容器。

3 結語

變流器采用低感母排設計能有效降低回路雜散電感值,使IGBT的開關損耗更小,同時換流回路的過電壓和系統EMI噪聲得到抑制,提高了IGBT運行的安全性。合理的疊層母排設計可以提高變流器的空間利用率,使變流器系統結構設計更加緊湊,有利于提高變流器系統的集成度和功率密度,提高系統的可靠性。

-

二極管

+關注

關注

148文章

10059瀏覽量

170622 -

IGBT

+關注

關注

1278文章

4036瀏覽量

253699 -

變流器

+關注

關注

7文章

293瀏覽量

33594 -

疊層母排

+關注

關注

0文章

5瀏覽量

1351

原文標題:IGBT變流器用低感母排技術(3)

文章出處:【微信號:JNsemi,微信公眾號:青島佳恩半導體有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

疊層母排在IGBT變流器中的應用(2)

DDR電路的疊層與阻抗設計

DDR電路的疊層與阻抗設計!

電子元器件:“疊層電感”的認識

疊層電感-疊層陶瓷電感-貼片疊層電感-片式疊層電感

原創|PCB設計中疊層結構的設計建議

PCB疊層的幾種不同變體

疊層電感的優點和應用

疊層母排在IGBT變流器中的應用(3)

疊層母排在IGBT變流器中的應用(3)

評論