在現(xiàn)代電子系統(tǒng)中,數(shù)據(jù)傳輸速度的快速增長帶來了諸多挑戰(zhàn)。當(dāng)信號(hào)頻率達(dá)到幾百兆赫茲甚至數(shù)千兆赫茲時(shí),傳統(tǒng)的單端信號(hào)傳輸方式面臨著信號(hào)完整性惡化、電磁干擾增強(qiáng)、功耗增加等問題。差分信號(hào)傳輸技術(shù)通過使用一對(duì)互補(bǔ)信號(hào)來傳遞信息,有效解決了這些高頻應(yīng)用中的關(guān)鍵問題。

差分設(shè)計(jì)不僅在高速數(shù)字通信、射頻系統(tǒng)、高速ADC/DAC等領(lǐng)域得到廣泛應(yīng)用,還成為了現(xiàn)代高速接口標(biāo)準(zhǔn)(如USB 3.0、PCIe、SATA、DDR等)的核心技術(shù)。深入理解差分設(shè)計(jì)原理和掌握相關(guān)設(shè)計(jì)技術(shù),對(duì)于現(xiàn)代電子工程師具有重要意義。

差分信號(hào)定義

差分信號(hào)是指用一對(duì)導(dǎo)線傳輸信號(hào),其中一根傳輸原始信號(hào),另一根傳輸與原始信號(hào)極性相反、幅度相等的信號(hào)。接收端通過檢測(cè)這兩個(gè)信號(hào)的差值來還原原始信息。在理想情況下,這兩個(gè)信號(hào)的幅度相等但極性相反,其差值為原始信號(hào)的兩倍。

差分信號(hào)的優(yōu)勢(shì)

抗噪聲能力強(qiáng):由于差分信號(hào)受到的共模噪聲在兩根導(dǎo)線上基本相同,通過差分檢測(cè)可以有效抑制共模噪聲。理論上,完全對(duì)稱的差分系統(tǒng)可以完全消除共模干擾。

電磁干擾小:差分信號(hào)對(duì)產(chǎn)生的電磁場(chǎng)相互抵消,減少了對(duì)外部的電磁干擾。同時(shí),差分結(jié)構(gòu)對(duì)外部電磁場(chǎng)的敏感性也較低。

信號(hào)完整性好:差分傳輸可以提供更好的信號(hào)完整性,特別是在高頻應(yīng)用中,差分走線的串?dāng)_和反射問題相對(duì)較小。

功耗優(yōu)化:在相同的信噪比要求下,差分信號(hào)可以使用較低的擺幅,從而降低功耗。

差分信號(hào)的應(yīng)用

差分信號(hào)廣泛用于以下應(yīng)用:

?USB,12 MB/s

?火線(IEEE-1394),100/200/400 MB/s

?LVDS,> 400 MB/s

?以太網(wǎng),10 MB/s,100 MB/s,1 GB/s

?光纖通道,1.0625 GB/s

?OC48,2.4 GB/s

?平板顯示器接口

?背板

除了背板信號(hào)傳輸之外,所有的應(yīng)用都具有一個(gè)共同特點(diǎn),即需要使用外部電路來實(shí)現(xiàn)數(shù)據(jù)傳輸,且這些傳輸速率必須保持在較高水平。

這些電路設(shè)計(jì)用于最小化輻射噪聲,減少更大距離上的損失。電路的數(shù)據(jù)速率范圍從10 Mb/s到2.4 Gb/s及以上,頻率達(dá)到1.2 GHz。所有這些都可以使用傳統(tǒng)制造技術(shù)在FR4基板材料上實(shí)現(xiàn)。如前所述,在先進(jìn)設(shè)計(jì)中采用差分信號(hào)傳輸有多種原因。噪聲抑制和更高的有效信號(hào)電平都提高了有效的信號(hào)與噪聲的比值,并降低錯(cuò)誤率。

布線設(shè)計(jì)規(guī)則

長度匹配:差分對(duì)內(nèi)的長度差異應(yīng)控制在很小的范圍內(nèi),通常要求在5-10密耳(mil)以內(nèi)。長度不匹配會(huì)導(dǎo)致時(shí)序偏移,或影響信號(hào)質(zhì)量。

間距控制:差分對(duì)內(nèi)導(dǎo)線之間的間距應(yīng)保持一致,通常間距與線寬的比例在1:1到3:1之間。間距過小會(huì)增加制造難度,過大會(huì)降低差分耦合效果。

對(duì)稱性設(shè)計(jì):差分對(duì)應(yīng)盡可能保持對(duì)稱,包括幾何對(duì)稱和電氣對(duì)稱。任何不對(duì)稱都會(huì)破壞差分結(jié)構(gòu),降低系統(tǒng)性能。

層疊設(shè)計(jì)考慮

參考平面選擇:差分走線應(yīng)有良好的參考平面,通常選擇完整的地平面或電源平面。參考平面的完整性直接影響信號(hào)完整性。

層間距離優(yōu)化:信號(hào)層與參考平面之間的距離影響特征阻抗和信號(hào)完整性。距離過近會(huì)增加寄生電容,過遠(yuǎn)會(huì)增加環(huán)路電感。

多層板設(shè)計(jì):在多層PCB設(shè)計(jì)中,應(yīng)合理規(guī)劃差分信號(hào)的走線層,避免跨越不連續(xù)的參考平面。

差分布局與布線

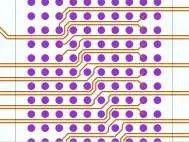

BGA案例

圖中展示了在墊層技術(shù)中使用uvia實(shí)現(xiàn)的BGA差分避讓布線特性。

外側(cè)的“避讓”區(qū)域位于頂部,而內(nèi)側(cè)的區(qū)域則位于第一層的內(nèi)側(cè)區(qū)域。

在電路上盡量減少端接電阻以及測(cè)試點(diǎn)的設(shè)置。

在整個(gè)電路板上采用一致的間距進(jìn)行布線,以最大限度地增加布線“通道”的數(shù)量。

通道內(nèi)的多層差分布線

通過保持在通道內(nèi)布線可以實(shí)現(xiàn)最大密度和最小的對(duì)間串?dāng)_:

- 將走線定位在過孔陣列所定義的水平和垂直布線"通道"內(nèi)。

- 優(yōu)先布線水平或垂直分量最少的差分對(duì)。

使用引導(dǎo)線的曼哈頓距離來確定給定層內(nèi)點(diǎn)對(duì)點(diǎn)連接的布線順序。

單層差分扇出和布線

使用單層差分扇出和布線,減小導(dǎo)體寬度以允許進(jìn)入和退出頂層上的BGA焊盤。

相鄰層上的差分布線

- 當(dāng)在相鄰層上布線差分對(duì)時(shí),交叉處應(yīng)該保持90°角。

- 這有助于提高密度,如上述示例所示,在網(wǎng)絡(luò)交換卡中,時(shí)鐘信號(hào)必須在相鄰的信號(hào)布線層上進(jìn)行布線。

分離差分對(duì)導(dǎo)體

平衡對(duì)可以短距離分離以增加通道布線密度,而不會(huì)大幅降低所需的差分耦合。

這個(gè)10Gbit網(wǎng)絡(luò)交換機(jī)背板的密度要求對(duì)耦合線進(jìn)行一些分離,部分原因是向后兼容連接器的引腳排列。

在圖片中,注意連接器引腳間距僅支持對(duì)角引腳之間45°角的"三線間隔"布線,這就必須進(jìn)行分離。

隨著系統(tǒng)性能要求的提升,差分設(shè)計(jì)需要支持更高的工作頻率,這對(duì)電路設(shè)計(jì)和工藝技術(shù)提出了更高要求。在移動(dòng)和便攜式應(yīng)用中,低功耗差分設(shè)計(jì)成為重要發(fā)展方向。片上差分系統(tǒng)的集成度不斷提高,需要解決器件匹配、熱管理等問題。

如今出現(xiàn)了不少的新興技術(shù),比如自適應(yīng)差分系統(tǒng):利用數(shù)字信號(hào)處理技術(shù)實(shí)現(xiàn)自適應(yīng)均衡和失配校正。人工智能輔助設(shè)計(jì):使用機(jī)器學(xué)習(xí)算法優(yōu)化差分電路參數(shù)和布局。新材料應(yīng)用:采用新型半導(dǎo)體材料和互連材料改善差分電路性能。

-

差分信號(hào)

+關(guān)注

關(guān)注

4文章

393瀏覽量

28231 -

信號(hào)傳輸

+關(guān)注

關(guān)注

4文章

453瀏覽量

20619

發(fā)布評(píng)論請(qǐng)先 登錄

如何實(shí)現(xiàn)高速時(shí)鐘信號(hào)的差分布線

LM4890采用差分設(shè)計(jì)方案,為什么沒有聲音?怎么解決?

ORCAD PCB 差分設(shè)置

空分設(shè)備的清洗

高速差分過孔的仿真分析

(Xilinx)FPGA中LVDS差分高速傳輸?shù)膶?shí)現(xiàn)

詳解差分信號(hào)及PCB差分設(shè)計(jì)中幾個(gè)誤區(qū)

高速應(yīng)用的差分設(shè)計(jì)

高速應(yīng)用的差分設(shè)計(jì)

評(píng)論