IP授權公司安謀(Arm)于 4 日宣布,旗下 Arm Artisan 物理 IP 將使用臺積電針對 Arm 架構開發(fā)的單芯片處理器(SoC),并用于 22 納米超低功耗(ultra-low power,ULP)與超低漏電(ultra-low leakage,ULL)的產品平臺。

Arm 指出,臺積電 22 納米 ULP / ULL 制程是針對主流行動與物聯網設備進行最佳化設計。不僅能提升基于 Arm 架構的 SoC 效能,與臺積電前一代 28 納米 HPC+ 制程平臺相較,更可顯著降低功耗及芯片面積。

Arm 物理設計事業(yè)群總經理 Gus Yeung 表示,這項次世代制程技術能在更低功耗和更小面積下加入更多功能,且結合 Artisan 物理 IP 及臺積電的 22 納米 ULP / ULL 制程平臺,在設計與制造成本方面有優(yōu)勢。雙方將為彼此的合作伙伴,提供立即顯現的每毫瓦運算效能,以及節(jié)省芯片面積方面的利益。

Arm 進一步指出,采用臺積電 22 納米 ULP / ULL 制程技術的 Artisan 物理 IP,包含晶圓廠贊助提供的內存編譯器,針對次世代網路終端運算設備在低漏電與低功耗的需求達到最佳化狀態(tài)。這些編譯器還附有超高密度與高效能物理 IP 標準元件庫,其中包含功耗管理套件、厚閘極氧化層元件庫等,協助優(yōu)化低漏電功耗。另外,還提供泛用型 I/O 解決方案,確保達成最大程度的效能、功耗、以及面積(PPA)最佳化。

臺積電設計建構行銷事業(yè)處資深處長 Suk Lee 指出,Artisan 物理 IP 讓臺積電加速設計定案(tape-out)時程,瞄準主流物聯網與行動設備,加快這些引領業(yè)界的 SoC 上市。延續(xù)臺積電與 Arm 在 28 納米 HPC+ 平臺成功合作的基礎,臺積電與 Arm 攜手大幅降低功耗與面積,為彼此共同的芯片設計伙伴提供許多機會,在更多設備呈現更完善的終端運算經驗。

Arm 指出,與臺積電 22 納米 ULP / ULL 制程技術的積極整合時程下,確保滿足 Arm 與臺積電共同的芯片設計伙伴可在 2018 下半年完成相關設計定案。

-

ARM

+關注

關注

134文章

9290瀏覽量

374739 -

臺積電

+關注

關注

44文章

5738瀏覽量

168852

發(fā)布評論請先 登錄

臺積電拒絕為三星代工Exynos芯片

臺積電計劃在美生產BLACKWELL芯片

蘋果加速M5芯片研發(fā),爭奪AI PC市場,臺積電先進制程訂單激增

谷歌Tensor G系列芯片代工轉向臺積電

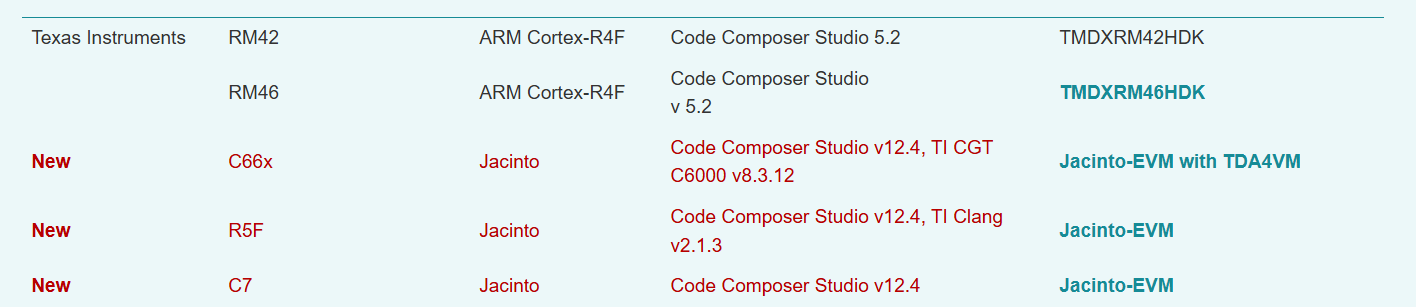

針對TI汽車處理器新的SAFERTOS庫評估包

ARM處理器的尋址方式

ARM處理器和CPU有什么區(qū)別

ARM處理器的工作模式和特點

ARM處理器和CISC處理器的區(qū)別

ARM處理器的結構和特點

ARM處理器概述和發(fā)展歷程

什么是ARM處理器?與x86的比較及其優(yōu)缺點

臺積電攜手創(chuàng)意電子斬獲HBM4關鍵界面芯片大單

MT6775|Helio P70芯片參數_MTK6775處理器參數配置

ARM將使用臺積電針對其構架開發(fā)的單芯片處理器

ARM將使用臺積電針對其構架開發(fā)的單芯片處理器

評論