AMD 自適應計算文檔按一組標準設計進程進行組織,以便幫助您查找當前開發任務相關的內容。您可以在設計中心頁面上訪問 AMD Versal 自適應 SoC 設計進程。您還可以使用設計流程助手來更深入了解設計流程,并找到特定于預期設計需求的內容。本文檔涵蓋了以下設計進程:

硬件、IP 和平臺開發:為硬件平臺創建 PL IP 塊、創建 PL 內核、功能仿真以及評估 AMD Vivado 時序收斂、資源使用情況和功耗收斂。還涉及為系統集成開發硬件平臺。本文檔中適用于此設計進程的主題包括:

端口描述

寄存器空間

時鐘設置

復位

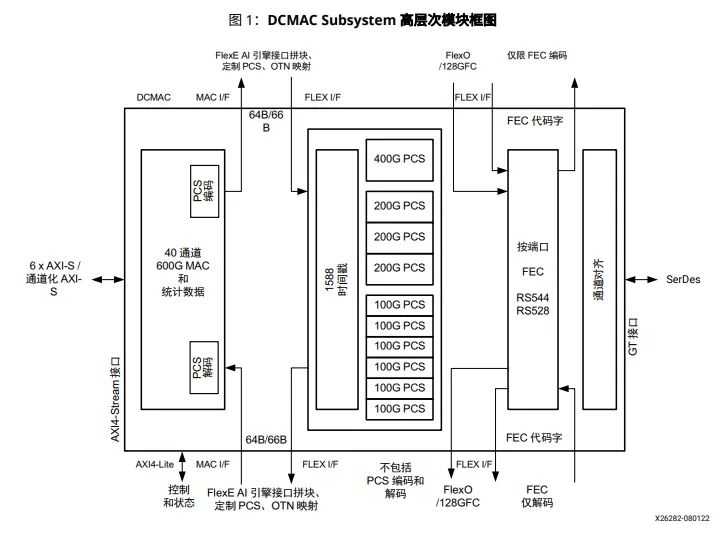

該AMD Adaptive SoC 600G Channelized Multirate Ethernet Subsystem( DCMAC Subsystem )屬于高性能、自適應、以太網集成硬核 IP,適用于多種客戶聯網應用。此塊可配置為最多 6 個端口,這些端口含獨立 MAC 和 PHY 功能,符合 IEEE 標準 MAC 速率(從 100GE 到 400GE ),并且總體最大帶寬達 600 Gb/s。此 IP 支持各種 FEC 和《 IEEE 1588 網絡測量和控制系統的精密時鐘同步協議標準》( IEEE 1588 )硬件時間戳。此外,此 IP 還可配置為提供 600 Gb/s 的 MAC 處理能力,適用于最多 40 條用戶定義帶寬的通道。

功能特性

支持 1 x 400GE、3 x 200GE、6 x 100GE 或者 100 Gb/s、200 Gb/s 與 400 Gb/s 組合(總計最高 600 Gb/s )

用戶側分段式 AXI4-Stream 接口,AXI4-Stream 時鐘頻率為 390.625 MHz

40 通道 Time-Sliced MAC,支持 600 Gb/s 運行

適用于時間分片式( time?sliced )應用的通道化選項

支持最多 40 條通道

用戶定義的帶寬分配粒度

80 位、160 位或 320 位接口,連接至串行收發器

《 IEEE 1588 網絡測量和控制系統的精密時鐘同步協議標準》( IEEE 1588 ):在入口和出口處添加完整位寬的單步和雙步硬件時間戳

暫停幀處理,包括基于優先級的流量控制

可選內置 RS?FEC 功能

子系統概述

本文檔描述了 AMD Versal Adaptive SoC 600G Channelized Multirate Ethernet Subsystem( DCMAC Subsystem )的功能和操作,包括如何設計、定制和實現 DCMAC Subsystem。

DCMAC Subsystem 能處理 Ethernet MAC、PCS 和 FEC 的所有協議相關功能,包括握手、同步和檢錯。它還提供分段式 AXI4-Stream 接口用于處理包數據,并提供 AXI4-Lite 接口用于統計數據和管理。

該子系統可以提供最多 6 個獨立以太網端口,專為在多種不同應用內靈活使用而設計。為降低時延,數據路徑僅執行必要操作所需的流水打拍,不執行任何其他緩沖操作。接收數據以直通方式直接傳遞到用戶接口,以便靈活實現任何所需的緩沖方案。同樣,發射路徑包含提供可靠的直通傳遞操作所需的最低限度流水打拍和緩沖功能。

DCMAC Subsystem 可配置為包含前向糾錯( FEC )。該子系統還提供一個 40 通道 600 Gb/s Time?Sliced MAC,它具有靈活的、用戶定義的帶寬分配粒度。

該子系統可配置為按如下模式來訪問 40 通道 MAC,即,支持用戶邏輯在一側使用通道化分段式 AXI4-Stream 接口,并在另一側使用通道化 MAC 接口( MAC I/F )。在此工作模式下,該子系統還可通過在一側使用靈活接口( FLEX I/F ),在另一側使用 SerDes 接口,提供用于訪問 PCS 和/或 FEC 的用戶邏輯。

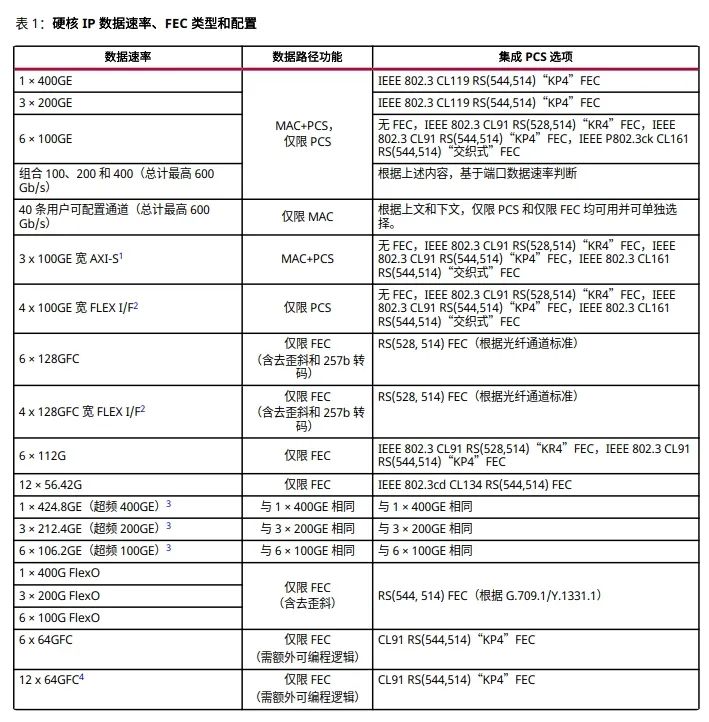

下表列出了硬核 IP 數據速率、FEC 類型和配置。如需了解有關 AMD Vivado 相關 AMD LogiCORE 所啟用的配置的信息,請參閱表 69:Vivado IDE 中 DCMAC IP 支持的配置。

1. 寬 AXI?S 表示分段式 AXI4-Stream 接口寬度翻倍,它對所有器件速度等級(包括 -1LP,僅在 100GE 工作模式下支持)都使用時鐘降頻。

2. 寬 FLEX I/F 將靈活接口寬度增大 25%,并且對于所有器件速度等級(包括 -1LP )都使用時鐘降頻。

3. 較快的器件支持超頻速率,較慢的器件支持標準速率(僅在 100GE 和 128GFC 工作模式下支持)。

4. 僅在較快的器件中受支持。

-

amd

+關注

關注

25文章

5564瀏覽量

135889 -

內核

+關注

關注

3文章

1410瀏覽量

41102 -

soc

+關注

關注

38文章

4341瀏覽量

221713 -

IP

+關注

關注

5文章

1785瀏覽量

151309 -

Versal

+關注

關注

1文章

167瀏覽量

8015

原文標題:Versal 600G DCMAC Subsystem LogiCORE IP 產品指南

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

華為600G高速傳輸光網走向商用

Logicore IP CAN過濾問題

UG157 LogiCORE IP Initiator/Ta

UG157 - LogiCORE IP Initiator,Target v3.1 for PCI 入門指南

全新小米凈水器600G高清圖賞

中興通訊專為DCI研發推出了新一代盒式600G OTN設備

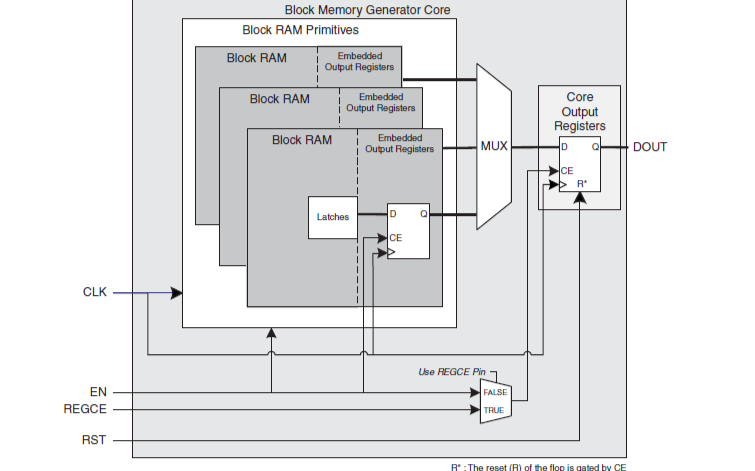

Xilinx LogiCORE IP塊內存生成器的產品指南

Versal ACAP 600G Channelized Multirate Ethernet Subsystem (DCMAC)LogiCORE IP產品指南

40G/50G High Speed Ethernet Subsystem產品指南

QDMA Subsystem for PCI Express產品指南

Versal ACAP收發器向導 LogiCORE IP產品指南

用于PCI Express的Versal ACAP集成塊產品指南

UltraScale FPGA收發器向導v1.7 LogiCORE IP產品指南

Versal 600G DCMAC Subsystem LogiCORE IP產品指南

Versal 600G DCMAC Subsystem LogiCORE IP產品指南

評論