引言

“數(shù)字集成電路(Integrated Circuit,簡稱IC)原理與設(shè)計”是為高等學(xué)校電子、通信、機(jī)電等工科電子類專業(yè)的高年級本科生和碩士生開設(shè)的一門課程,是培養(yǎng)我國急需的、緊缺的IC設(shè)計人才的入門課程。其主要任務(wù)是使學(xué)生能在較為全面地了解IC設(shè)計工藝和掌握IC設(shè)計工具的基礎(chǔ)之上,掌握IC基本單元的設(shè)計,為更復(fù)雜、規(guī)模更大的電路和系統(tǒng)的設(shè)計奠定理論基礎(chǔ),并通過相關(guān)實驗使學(xué)生對微電子技術(shù)產(chǎn)生濃厚的興趣。然而筆者經(jīng)過調(diào)查發(fā)現(xiàn),學(xué)生在學(xué)習(xí)過程中不能系統(tǒng)地了解自己所學(xué)的是什么、具體能干什么,以至于對IC設(shè)計產(chǎn)生不了濃厚的學(xué)習(xí)興趣。實際上,“數(shù)字集成電路原理與設(shè)計”是一門實踐性很強(qiáng)的專業(yè)課程,完全依靠傳統(tǒng)的板書教學(xué)或者多媒體PPT教學(xué)都很難表達(dá)清楚。因此,如何在有限的學(xué)時內(nèi)通過改革教學(xué)方法與教學(xué)手段實現(xiàn)教學(xué)理論與實踐有機(jī)結(jié)合從而提高授課效率是現(xiàn)階段該課程教學(xué)的一個研究重點。對于此問題,電子設(shè)計自動化(EDA)計算機(jī)仿真軟件給IC教學(xué)提供了一個可靠的理論與實踐聯(lián)系的平臺。

目前,IC設(shè)計仿真軟件很多,其中按市場所占份額排行為Cadence、Mentor Graphics和Synopsys。這些工具功能極其強(qiáng)大,涵蓋了IC設(shè)計的整個流程,包括系統(tǒng)級設(shè)計、功能驗證、IC綜合及布局布線、模擬和混合信號及射頻IC設(shè)計、全定制IC設(shè)計、IC物理驗證等。然而由于成本高、適用操作系統(tǒng)環(huán)境有所限制、不適合IC初學(xué)者等劣勢,它們并不十分適合于本科生的教學(xué)工作。相比之下,本文介紹的Mentor收購的Tanner公司開發(fā)的基于Windows平臺的用于IC設(shè)計的工具軟件Tanner EDA更適用于高校進(jìn)行相關(guān)的教學(xué)和科研工作。一放面,Tanner EDA成本低,設(shè)備要求不高,可以在任何個人PC機(jī)上使用。另一方面,該IC設(shè)計工具具有強(qiáng)大的IC設(shè)計、模擬驗證、版圖編輯和自動布局布線等功能,圖形界面友好,編輯功能強(qiáng),易學(xué)易用。

1 利用Tanner EDA進(jìn)行IC設(shè)計的流程

利用Tanner EDA進(jìn)行IC芯片設(shè)計的流程如下:

1.1 編輯原理圖。利用電路圖編輯環(huán)境S-Edit工具,根據(jù)設(shè)計要求編輯合理的電路原理圖,注意在設(shè)計原理圖時要與IC芯片代工廠使用的具體工藝相結(jié)合,設(shè)定器件的工藝參數(shù)。

1.2 模擬仿真。提取電路圖的Spice網(wǎng)表(*.sp),用T-Spice工具模擬仿真電路的邏輯特性、延遲特性等,用W-Edit觀察仿真波形。如果模擬結(jié)果有錯誤,需返回第一步修改原理圖。如果無誤,則以L-Edit進(jìn)行版圖設(shè)計。

1.3 版圖設(shè)計。輸出TPR網(wǎng)表(*.tpr),用L-Edit工具進(jìn)行版圖的編輯和生成,如果采用廠家提供的標(biāo)準(zhǔn)單元,此時可以直接利用L-Edit的自動布局布線SPR功能得到整個IC芯片的版圖,如果是全定制設(shè)計,需事先根據(jù)所用的工藝,進(jìn)行標(biāo)準(zhǔn)單元設(shè)計,注意在版圖設(shè)計過程中要以DRC功能作設(shè)計規(guī)則檢查。如果違反設(shè)計規(guī)則,則修改版圖,直到設(shè)計規(guī)則檢查無錯誤為止。

1.4 版圖驗證。將驗證過的版圖輸出Spice網(wǎng)表(*.spc),使用T-Spice工具進(jìn)行模擬仿真(后仿真),如果波形正確即通過驗證;也可以用LVS工具,來對比版圖和原理圖,若一致,即通過驗證。最終驗證無錯誤后,將L-Edit設(shè)計的版圖輸出成GDSII文件類型,提交給IC芯片代工廠加工生產(chǎn)該IC芯片。

2 應(yīng)用Tanner EDA設(shè)計5位同步加法計數(shù)器芯片的實例

2.1 用S-Edit編輯電路原理圖

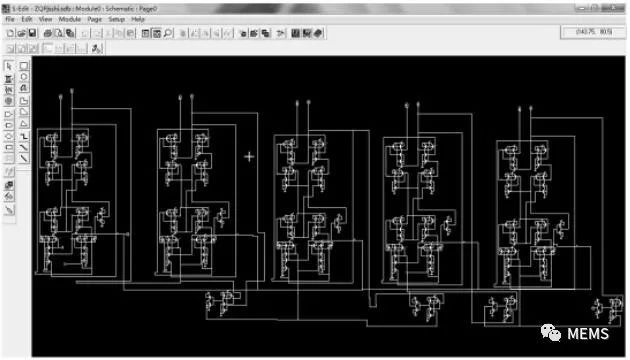

S-Edit工具簡單易用,與Protel、Multisim、protues等常用的原理圖編輯工具相比使用起來并不復(fù)雜,它可以設(shè)計特定功能的電路模塊。圖1是我們在S-Edit工具中利用element庫中NMOS,PMOS等元器件得到的5位二進(jìn)制同步加法計數(shù)器電路模塊的原理圖。該計數(shù)器采用5個邊沿JK觸發(fā)器串行連接而成,每個觸發(fā)器均連成T觸發(fā)器,再由4個2輸入端與非門連接。S-Edit電路圖編輯器可以把當(dāng)前模塊的電路圖轉(zhuǎn)化為不同的網(wǎng)表。這些網(wǎng)表主要是用于T-Spice電路模擬器的Spice網(wǎng)表,用于L-Edit版圖編輯器中的標(biāo)準(zhǔn)單元自動布圖布線的TPR網(wǎng)表、VHDL網(wǎng)表、NeTran網(wǎng)表以及EDIF網(wǎng)表。

圖1 5位二進(jìn)制同步加法計數(shù)器的原理圖

2.2 用T-Spice進(jìn)行模擬仿真

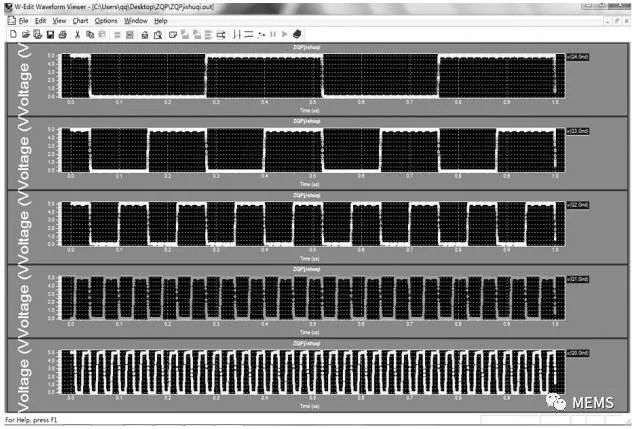

編輯好計數(shù)器的電路原理圖后,為確認(rèn)該電路功能正確,需要利用電路模擬工具T-Spice進(jìn)行仿真,但該工具不能直接對原理圖進(jìn)行仿真,因此在仿真之前需從原理圖輸出Spice網(wǎng)表(*.sp),該網(wǎng)表文件以節(jié)點的形式描述了電路的拓?fù)浣Y(jié)構(gòu)和元器件的工藝參數(shù)。而在輸出網(wǎng)表之后,必須加入工藝庫模型文件、設(shè)定各種仿真必要的參數(shù)、確定分析電路特性所需的分析內(nèi)容和分析類型等。根據(jù)T-Spice的格式要求得到*.sp網(wǎng)表文件之后,可以在T-Spice工具下進(jìn)行電路的功能仿真。圖2是從W-Edit觀察到的5位二進(jìn)制同步加法計數(shù)器的仿真波形圖。

圖2 5位二進(jìn)制同步加法計數(shù)器的仿真波形圖

2.3 用L-Edit進(jìn)行版圖設(shè)計

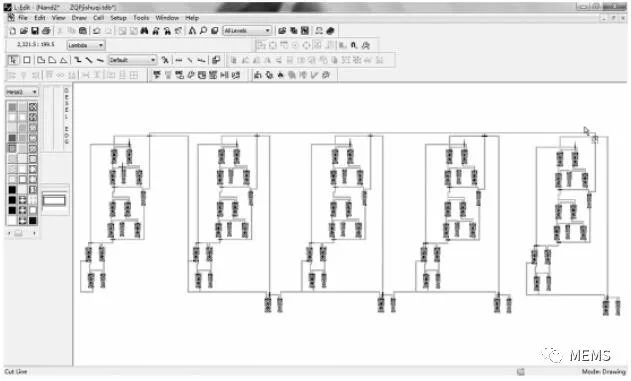

圖3 5位二進(jìn)制同步加法計數(shù)器芯片的版圖

計數(shù)器電路的功能仿真正確后,需要利用L-Edit進(jìn)行版圖設(shè)計。根據(jù)事先應(yīng)用特定工藝建立好的標(biāo)準(zhǔn)單元庫 (反相器、與非門、或非門、異或門、同或門等),在L-Edit工具中利用電路圖驅(qū)動版圖技術(shù)(SDL)來進(jìn)行計數(shù)器的版圖設(shè)計。SDL能根據(jù)電路原理圖轉(zhuǎn)換的TPR網(wǎng)表(*. tpr)自動生成計數(shù)器電路中各個MOS管的版圖,我們只需對這些MOS版圖進(jìn)行金屬互連。值得注意的是,在MOS版圖金屬互連過程中,一定要進(jìn)行設(shè)計規(guī)則檢查(DRC),看是否符合事先設(shè)定的工藝設(shè)計規(guī)則,如果正確,下一步就是要用LVS進(jìn)行版圖與原理圖的對比。

2.4 用LVS進(jìn)行版圖驗證

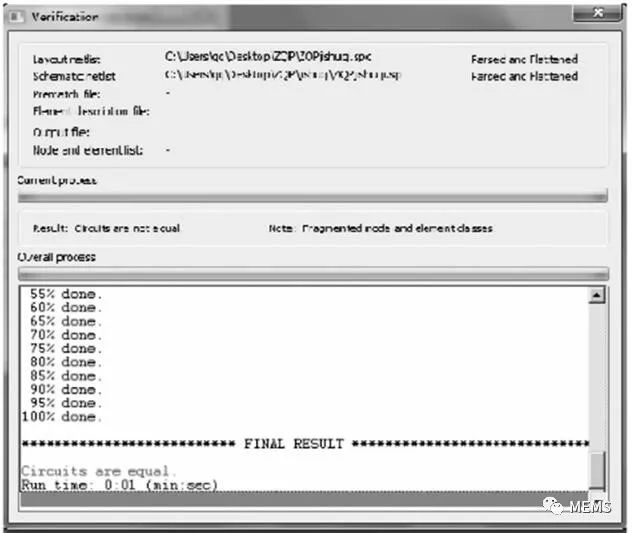

LVS(版圖與電路圖比較器)是一種網(wǎng)表比較工具,主要用來檢查IC芯片版圖的正確性。LVS通過比較L-Edit的Extract(版圖提取器)從版圖提取的Spice網(wǎng)表(*.spc)與S-Edit的網(wǎng)表輸出功能從同一設(shè)計的電路原理圖產(chǎn)生的Spice網(wǎng)表(*.sp),判別它們是否描述同一個電路。如果S-Edit中的電路圖已通過驗證,利用LVS,后一張網(wǎng)表可以作為判別前一張網(wǎng)表正確性的標(biāo)準(zhǔn),實現(xiàn)電路圖與版圖的比較。如果兩個網(wǎng)表一致,工具的對話界面將出現(xiàn)“Circuits Are Equal”的提示,則通過驗證,說明設(shè)計成功。由圖4的LVS對比結(jié)果可知本文成功設(shè)計了計數(shù)器。實際上,當(dāng)不一致時,LVS還能幫助確認(rèn)和改正版圖中錯誤,然后重復(fù)進(jìn)行驗證過程,直到成功為止。最終將L-Edit設(shè)計好的版圖輸出成GDSII文件類型,提交給芯片代工廠加工生產(chǎn)該計數(shù)器IC芯片。

圖4 LVS對比結(jié)果

3 結(jié)論

本文介紹了一種實用的、適合于數(shù)字集成電路原理與設(shè)計課程教學(xué)的IC設(shè)計工具Tanner EDA。通過以上應(yīng)用實例可以看出,采用Tanner EDA進(jìn)行IC設(shè)計,現(xiàn)象直觀,結(jié)果精確。可見,將先進(jìn)的計算機(jī)仿真技術(shù)和現(xiàn)代教學(xué)結(jié)合起來,有利于理論與實踐的結(jié)合,對于學(xué)生理解IC的原理與設(shè)計流程,對于學(xué)生微電子技術(shù)的興趣的激發(fā)、吸引他們涉足IC設(shè)計領(lǐng)域都有很好的幫助。

-

eda

+關(guān)注

關(guān)注

71文章

2924瀏覽量

177926 -

數(shù)字集成電路

+關(guān)注

關(guān)注

11文章

94瀏覽量

22278

原文標(biāo)題:Tanner EDA在數(shù)字集成電路教學(xué)中的應(yīng)用

文章出處:【微信號:MEMSensor,微信公眾號:MEMS】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

華大九天Empyrean Liberal工具助力數(shù)字集成電路設(shè)計

思爾芯攜手南京大學(xué)開展暑期協(xié)同課程,產(chǎn)教融合共育集成電路英才

EDA是什么,有哪些方面

新思科技攜手深圳大學(xué)助力數(shù)字集成電路人才培養(yǎng)

產(chǎn)學(xué)研融合!思爾芯數(shù)字EDA工具走進(jìn)北航課堂

數(shù)字集成電路 Verilog 熟悉vivado FPGA微電子、電子工程

新思科技攜手深圳大學(xué)推動集成電路設(shè)計領(lǐng)域發(fā)展

集成電路測試方法與工具

74VHC00FT CMOS數(shù)字集成電路硅單片英文手冊

什么是集成電路?有哪些類型?

音響集成電路是數(shù)字集成電路嗎

TC7WZ74FK CMOS數(shù)字集成電路硅單片規(guī)格書

ic 電子元器件類型有哪些?

思爾芯賽題正式發(fā)布,邀你共戰(zhàn)EDA精英挑戰(zhàn)賽!

Tanner EDA:數(shù)字集成電路原理與設(shè)計課程教學(xué)的IC設(shè)計工具

Tanner EDA:數(shù)字集成電路原理與設(shè)計課程教學(xué)的IC設(shè)計工具

評論