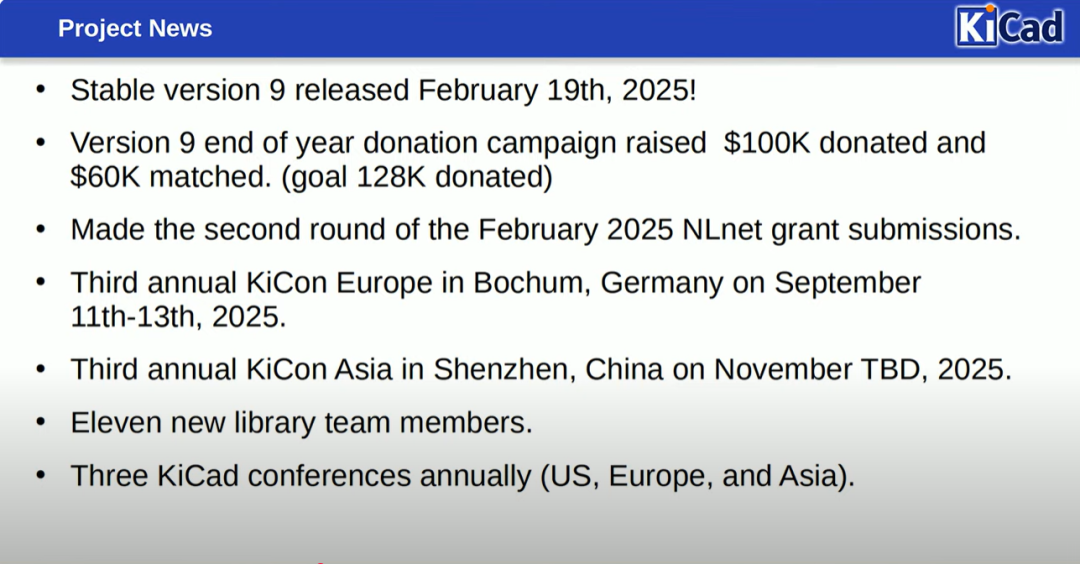

“KiCon US 于 5.28~30 在美國的圣地亞哥舉行。這個會議有 live stream,有興趣的小伙伴可以去油管上查看。接下去還有 9 月的 KiCon Europe 以及 11 月 的 KiCon Asia。”

?

?第一天的內容錄播 URL 在這里:

https://www.youtube.com/watch?v=v2uiwDnLGx8

很高興看到會議上出現了很多關于中國社區的信息:

第一天的 Topic

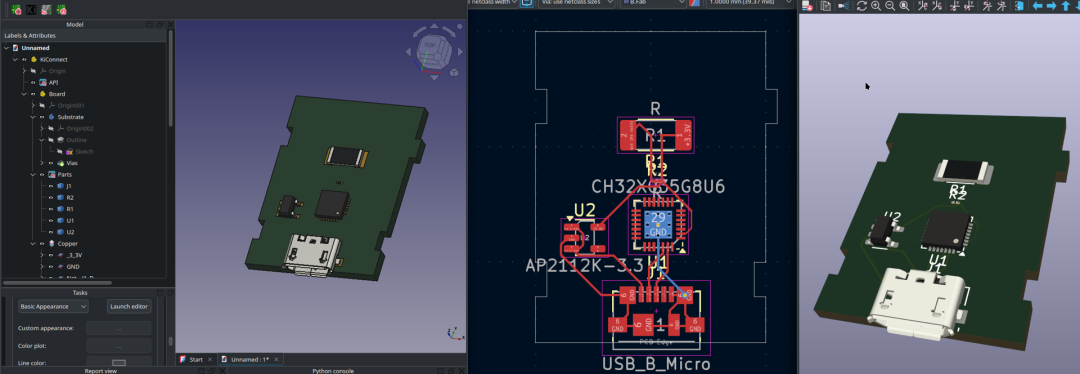

1. 介紹 KiConnect (Morgan Allen)

KiConnect 是我自 2018 年創建 The Cacoffiny 以來就夢寐以求的 FreeCAD 工作臺。經歷了幾次失敗的嘗試后,如今終于天時地利。FreeCAD 1.0 發布了,KiCAD 9 也帶著其新的長期支持 API 即將問世,我終于看到了這個工作臺可能實現的曙光。

即便在早期階段,它已經能實現我想要的許多功能,其中最重要的莫過于能夠將電路板放入 FreeCAD 裝配體中,并能夠對其進行原地更新。以前我僅能通過一堆脆弱的宏指令堆砌勉強實現的功能,如今只需點擊幾下即可完成。

隨著核心功能順利推進,未來的發展路線圖充滿了可能性。多板裝配體、剛柔結合裝配體、異形板的拼板,以及更多功能。

3.從 Altium 到 KiCad 以及其間的各種工具:將開源EDA集成到專業工作流程中的路徑(Eli Hughes)

?

?將 KiCad 集成到我們專業工作流的決定,是由以下幾個因素共同驅動的:

- 專業許可證“維護”成本與實際獲得的支持價值之間存在脫節。

- “永久”許可證中原有功能被移除。

- 對封閉的二進制文件格式感到沮喪,這導致了嚴重的工作流問題(現場將分享真實案例)。

- 與 MCAD 格式的互操作性被刻意限制(現場將分享真實案例)。 我們曾多次遇到這樣的情況:為了滿足客戶的特定需求,不得不將 PCB 導入 KiCad,利用其 3D 導出功能。

- 將工具適配到公司特定的 CI/CD 工作流門檻過高。

- 認識到大量 PCB 設計師正在退休。 新進入的硬件開發者普遍具備 git、持續集成、Python 和軟件開發工作流的經驗。EDA 工具行業需要適應這種人員結構的變化。

- 對項目長期性的擔憂(Wavenumber 的某些項目周期長達 20 年以上;我們最近還需要打開 2005 年項目的文件)。

LLM(大語言模型)技術的出現,使得各類工程師能夠通過腳本和小型實用工具快速適應和定制流程,而無需成為軟件專家。

對于像我們這樣的設計組織,真正的競爭優勢不僅在于元件庫,更在于跨設計積累的關于部件如何配置、連接和實現的知識。這種組織知識資產,即真正的“制勝法寶”,其價值會隨時間推移而日益增長,但有效維護和共享卻充滿挑戰。我們認為,每家公司都需要圍繞其自身的組織知識資產制定策略,并且這些知識絕不能被封閉在不使用互操作格式的第三方服務之后。

我們啟動 KiCad 項目的一個主要動機是其新的 HTTP 元件庫功能。我們將其視為一個更宏大愿景和企業級功能的開端。我們曾廣泛使用數據庫元件庫,但 Altium 的解決方案已停滯不前,偏向于其專有的云接口。盡管 KiCad 的 HTTP 庫功能仍在開發中,但它為我們提供了一種機制,將大約 10,000 個部件及其相關元數據遷移到 KiCad 9。通過利用kicad-cli工具,Wavenumber 成功構建了一個并行工作流的原型:在 Altium 中創建的所有部件也能在 KiCad 中使用。

目前,我們的元件庫遷移工作已基本完成。有兩個將在 2025 年發布的商用產品設計中使用的電路板正在開發中。我們還將 KiCad 集成到了我們的 PDM(產品數據管理)系統中,這種方式既能支持快速原型設計,又能提供重要的設計可追溯性。長期目標是建立一個全面的工作流,以追蹤公司內所有電路板、裝配體及其使用場景,并能進行高效的基于 LLM 的知識查詢。

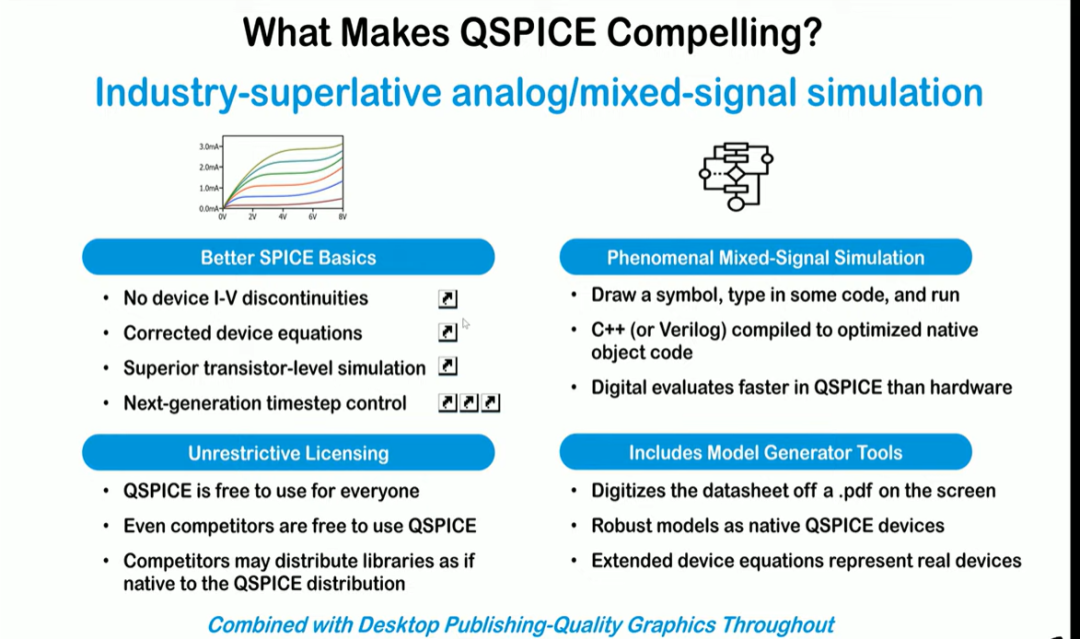

4.QSPICE 建模與仿真工具,助力更高效的 PCB 布局(Mike Engelhardt)

?

?Mike 也是 LTSpice 的作者。

QSPICE 是一款基于 SPICE 的免費電路仿真軟件,包含用于創建 JFET、MOSFET 和二極管模型的工具。本次演示將詳細說明并記錄不同 QSPICE 進程之間的進程間通信,以便用戶可將 QSPICE 電路圖替換為 KiCAD 電路圖,從而在 KiCAD 中添加仿真、波形跟蹤和交叉探測功能。這將使 KiCAD 用戶能夠集成 QSPICE 元素,以補充 KiCAD 的功能,從而提升其電路仿真、模型創建和布局體驗。

5.如何使用KiCad 9自定義DRC避免常見DFM問題(Amit Bahl)

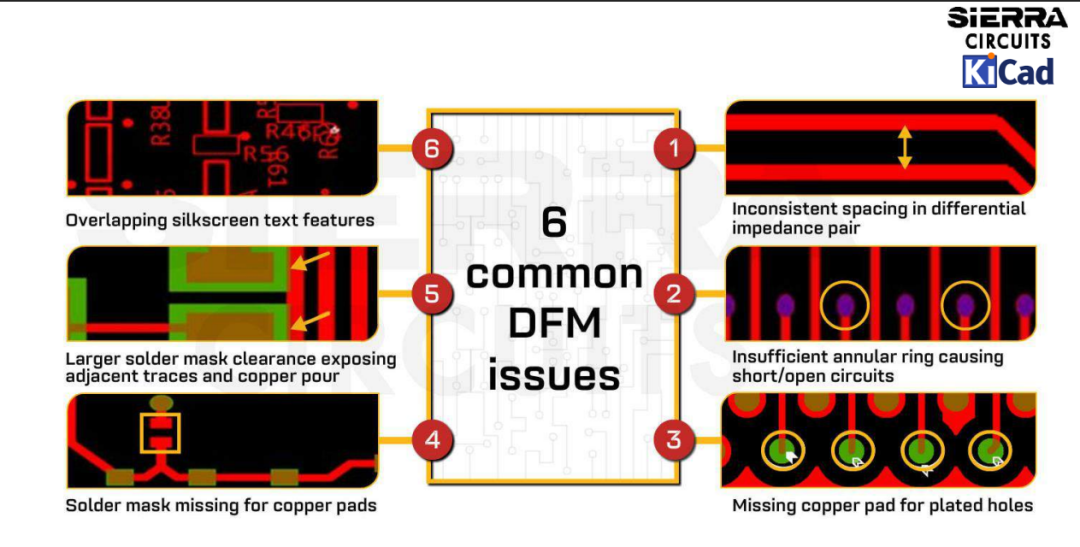

設計PCB不僅僅是布線和連接組件,它還涉及確保電路板能夠在不產生昂貴返工和延誤的情況下進行制造。這就是DRC發揮作用的地方。它們作為防止 DFM 問題的屏障,在設計進入制造工廠之前就發現錯誤。KiCad 9 通過自定義DRC進一步提升了這一功能,從設計初期就確保可制造性。

在本場演講中,您將學習如何在KiCad 9中設置自定義DRC以防止關鍵制造錯誤。

更新后的KiCad 9 DRC引擎支持更深入的自定義,允許您定義規則并匹配制造商的能力。您可以提前設置導線寬度和鉆孔尺寸的約束條件,消除猜測的必要性。

PCB設計中常見的陷阱之一是違反導線寬度和間距要求。如果導線過細,可能導致過熱。如果導線間距過近,則存在短路風險。為解決此問題,可在DRC編輯器中設置最小導線寬度和間距值(例如6 mil)。

過孔和環形區域容易出現制造問題。當過孔或環形區域尺寸過小時,可能導致開路。設置最小過孔尺寸和環形區域寬度,以匹配您的PCB制造商的鉆孔公差。根據您的鉆孔到銅層間距要求配置DRC(建議8密耳)。絲印和焊料掩模規則必須應用,以確保文字清晰可讀和足夠的掩模間距。

無需為單個導線應用長度匹配規則,可創建組并設置約束以防止信號失真。

別忘了用DRC驗證元件布局。為避免裝配問題,需在電路板邊緣及大型元件之間定義禁入區。

配置DRC可使設計準備就緒,讓原型機具備量產條件。使用KiCad 9自定義DRC以強制執行符合制造要求的實用設計規則。

6.Zero to KiCad(Walter Stanish)

作為一名軟件背景的從業者,由于業務需求,我首次通過KiCad 5.1接觸生產電子設計。在這一非 trivial 的項目中,我們將分享在工作流程、項目管理、升級難題、文件類型、自定義自動化、機械集成、布線與互聯、知識產權等多個方面遇到的挑戰與機遇。

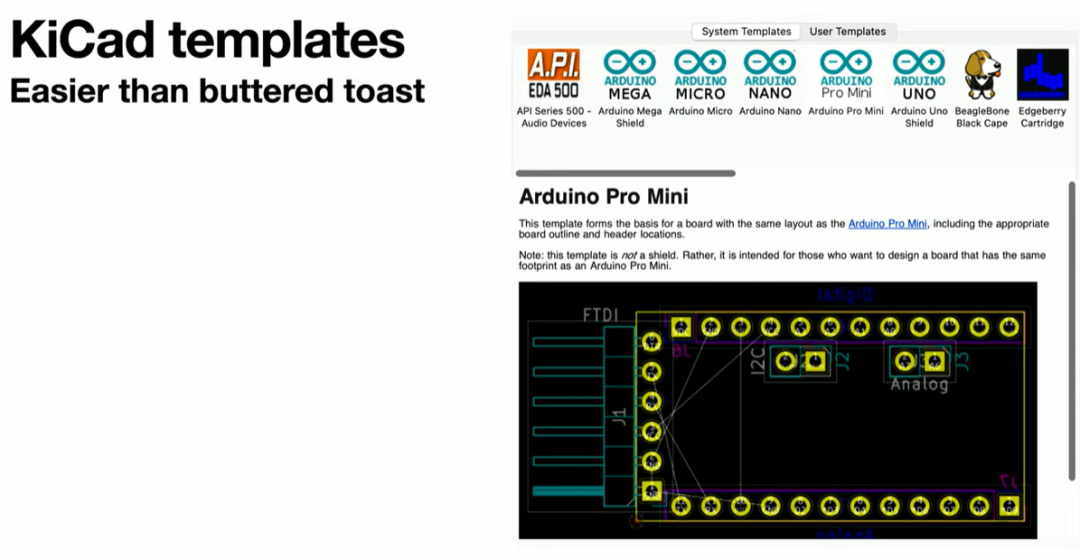

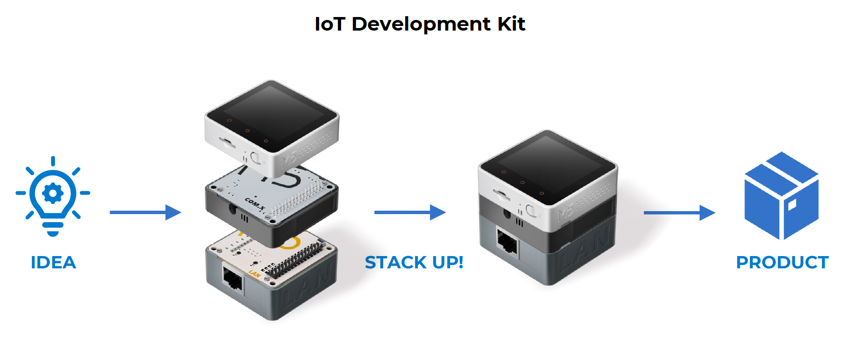

7.拼圖項目:利用KiCad模板創建可互換原型與開發板(Reed Harston)

通過使用 KiCad 項目模板創建可互換和可互鎖的電路板,實現更快速、更經濟的原型開發,并在項目早期階段增強信心。

在硬件開發中,原型階段常常被跳過——或者在制作后強行塞入最終產品而非重新設計——因為負責預算的人(可能就是你!)認為原型制作成本高昂且耗時。在精打細算時,似乎立即著手開發“正式產品”更劃算。當設計足夠簡單且團隊經驗豐富時,這種情況可能成立,但考慮到當今技術水平和每天都有新工程師加入該領域,這種組合何時才能真正實現?

在Appaloosa Computing,我們開發了一套原型開發模板系統,允許我們通過幾塊簡單的“拼圖塊”電路板,以多種方式組合,實現電路板和元器件布局的即時更改。這使得我們可以重復使用已驗證的電路板,并快速迭代那些需要改進的電路板,從而加速原型開發并降低成本。

-

pcb

+關注

關注

4354文章

23422瀏覽量

406889 -

電路板

+關注

關注

140文章

5093瀏覽量

101614 -

KiCAD

+關注

關注

5文章

233瀏覽量

9341

發布評論請先 登錄

KiCad Conference 預告及 KiCon Asia 調研

KiCad直播活動(三):在 Windows上編譯KiCad 手把手教您編譯/構建 KiCad 源碼

KiCad 直播系列活動預告(二):KiCad 華秋發行版專題介紹

KiCad 直播系列活動預告(一):KiCad 9 新功能揭秘

KiCon 演講回顧(十五):提交 Kicad Bug

KiCon 演講回顧(十三):嵌入工程師的硬件夢之 KiCad 經驗和項目分享

KiCon演講回顧(二):華秋 KiCad 發行版

KiCon 主會議倒計時 2 天!培訓活動明日啟航

KiCad 線下培訓開始報名 (KiCon Asia 2024 系列活動)

KiCon 3 天倒計時 與KiCad全球開發者對話 了解最前沿信息

KiCad Asia 2024:與全球 KiCad 用戶共筑創新之路 - 報名已開啟

看看老外們在 KiCad 社區做什么:KiCon US 首日議程圖文

看看老外們在 KiCad 社區做什么:KiCon US 首日議程圖文

評論