概述

ADN4620/[ADN4621]均為雙通道、信號隔離式、低壓差模信號(LVDS)緩沖器,數據速率高達2.5 Gbps,并且具有非常低的抖動。這些器件集成了ADI公司的iCoupler?技術,已針對高速運行進行了增強,可提供LVDS信號鏈的插入式電氣隔離。與LVDS接收器和LVDS驅動器之間的交流耦合和/或電平轉換允許隔離其他高速信號,例如電流模式邏輯(CML)。

ADN4620/ADN4621包括一種刷新機制,用于監控輸入和輸出狀態,并確保它們在沒有數據轉換的情況下(例如上電時)保持不變。為了以低抖動實現低功耗和高速運行,隔離器電路采用1.8 V電源,3.3 V電源用于LVDS接收器,以支持全共模范圍,輸入電壓范圍為(輸入共模+差分輸入電壓)0 V至2.4 V,如數據手冊中的表2所示。

額定溫度范圍為寬工業溫度范圍,采用具有5.3 mm爬電距離的緊湊型SSOP封裝(在交流電源電壓下實現強化絕緣)或具有15.1 mm爬電距離的寬SOIC_IC封裝(增強的高工作絕緣電壓高達1500 V峰值)。

數據表:*附件:ADN4620 ADN4621 7.5 kV RMS 3.75 kV rms雙通道LVDS 2.5 Gbps隔離器技術手冊.pdf

應用

特性

- 7.5 kV rms/3.75 kV rms LVDS隔離器

- 符合TIA/EIA-644-A LVDS信號電平標準

- 雙通道配置(ADN4620:2 + 0,ADN4621:1 + 1)

- 任何數據速率支持高達2.5 Gbps開關頻率,具有低抖動特性

- 兩個通道的總帶寬為5 Gbps

- 2.15 ns傳輸延遲(典型值)

- 典型抖動:0.82 ps rms(隨機),40 ps(總峰峰值)

- 低功耗1.8 V電源和用于I/O的3.3 V電源

- 高達±8 kV的IEC 61000-4-2 ESD隔離柵保護

- 高共模瞬變抗擾度:70 kV/μs(典型值)

- 安全和法規認證(16引腳SOIC_IC封裝)

- UL(申請中):1分鐘7500 V rms,符合UL 1577

- CSA元件驗收通知5A(申請中)

- VDE合規證書,強化絕緣(申請中)

- DIN V VDE V 0884-11 (VDE V 0884-11):2017-01

- V

IORM= 1500 VPEAK(最大工作絕緣電壓)

- 使能或禁用刷新(20引腳SSOP封裝)

- 工作溫度范圍:?40°C至+125°C

- 具有5.3 mm爬電距離的緊湊型SSOP封裝或具有15.1 mm爬電距離的寬SOIC_IC封裝

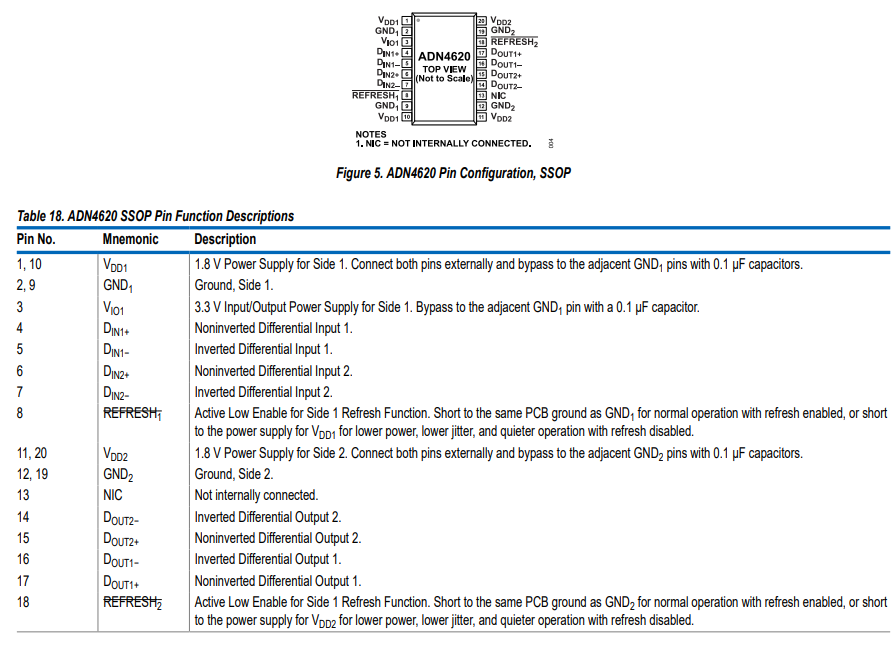

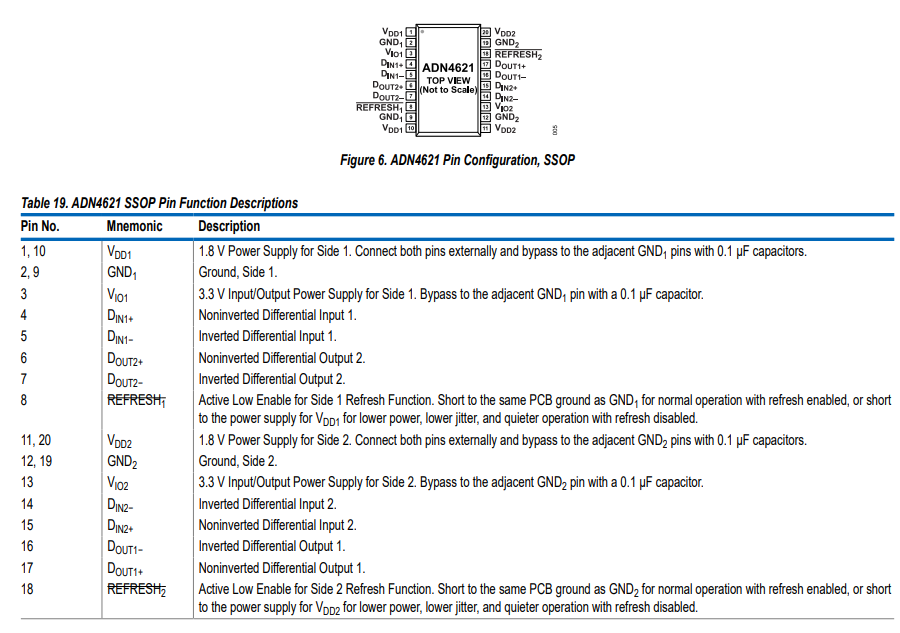

引腳配置描述

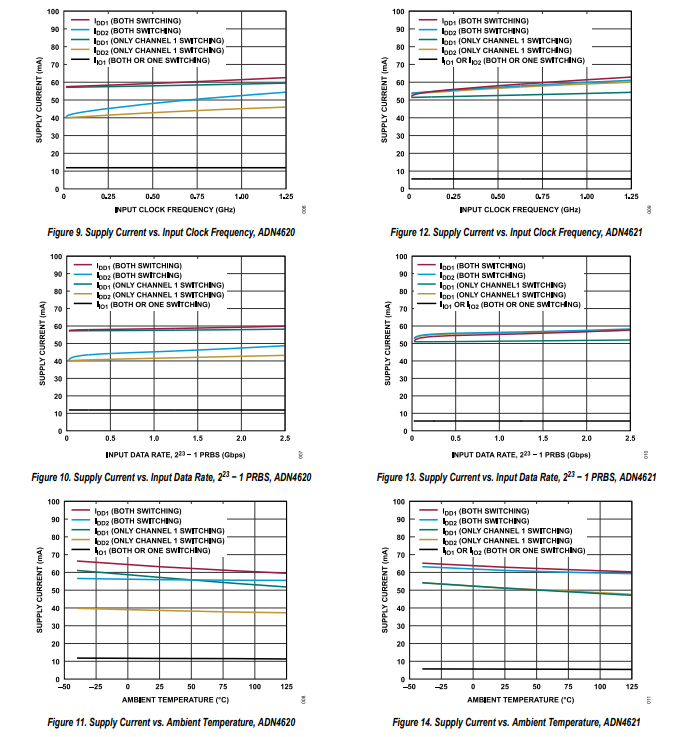

典型性能特征

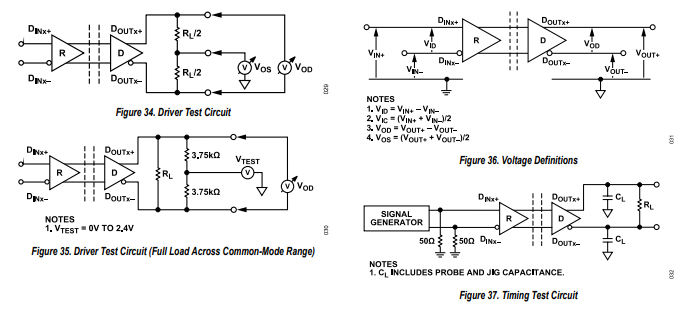

測試電路和開關特性

隔離與刷新

ADN4620/ADN4621是高速差分信號隔離器,能夠以高達2.5Gbps的速率切換,信號電平符合TIA/EIA - 644 - A標準。這些器件將施加到LVDS接收器輸入端的差分信號,通過隔離柵耦合到另一側,并以LVDS形式重新傳輸比特流或時鐘。這種集成方式允許LVDS信號鏈的中斷隔離,以及對其他信號(如CML)的隔離。

LVDS接收器檢測LVDS輸入上端接電阻兩端存在的差分電壓。集成數字隔離器將輸入狀態傳輸到隔離柵另一側,LVDS驅動器輸出與輸入相同的狀態。

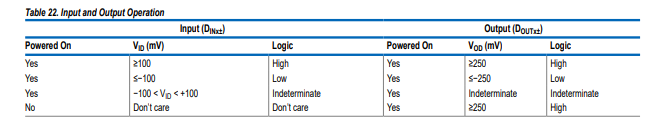

當在任意DIn+引腳和對應的DIn-引腳之間存在+100mV的正差分電壓時,對應的DOut+引腳會流出電流。該電流通過連接的傳輸線和端接電阻流動,而DOut-引腳吸收回流電流。當在任意DIn+引腳和對應的DOut-引腳之間存在-100mV的負差分電壓時,對應的DOut+引腳吸收電流,而DOut-引腳流出電流。表22總結了這些輸入和輸出組合。

該輸出驅動電流為±2.5mA和±4.5mA(典型值為±3.1mA),在100Ω端接電阻(RT)上產生±250mV和±450mV的電壓。接收電壓以1.2V為中心。由于差分電壓(VD)會反轉極性,跨越RT的電壓擺幅是差分電壓幅值(|VD|)的兩倍。

為響應集成LVDS接收器檢測到的輸入狀態變化,編碼器電路會發送窄(~1ns)脈沖,以觸發解碼器,使輸出LVDS驅動器緩沖器輸出恢復到正常工作狀態,反映隔離的LVDS輸入狀態。

對于ADN4620/ADN4621的正常運行,SSOP封裝型號上的低電平有效使能引腳(ENABLE1和ENABLE2)分別短接到相應的電源(VDD1和VDD2),以啟用刷新功能。啟用此功能后,解碼器會在檢測到輸入狀態變化超過約1μs時,發送周期性刷新脈沖(指示輸入邏輯轉換),包括故障安全輸出狀態(如適用)。此功能在SOIC封裝型號上永久啟用,用于SOIC。

上電時,輸出狀態初始為正確狀態,若無輸入轉換,在1μs內由刷新脈沖校正。

如果解碼器在超過約1μs的時間內未接收到內部脈沖,器件會認為輸入側未通電或無功能,此時輸出將設置為正差分電壓(邏輯高電平)。

對于時鐘、恒定比特流或協議,如果錯誤校正,刷新功能可能不需要。如果SSOP封裝型號上的ERROR1和ERROR2引腳以及REFRESH1和REFRESH2引腳短接到相應的電源(VDD1和VDD2),則刷新功能將被禁用,允許在無內部時鐘信號(可能會減少傳導或輻射發射)的情況下運行。在此模式下,可能需要在輸入側或連接的輸出側進行數據轉換,甚至在超過保證的共模瞬態抗擾度規范的電源上電后,也可能需要進行共模輸出狀態事件。

真值表

LVDS標準TIA/EIA - 644 - A定義了兩種正常接收器工作條件:輸入差分電壓為+100mV對應一種邏輯狀態,-100mV對應另一種邏輯狀態。在這些閾值之間,標準允許接收器檢測任一邏輯狀態,如表22所示。

-

緩沖器

+關注

關注

6文章

2037瀏覽量

46549 -

lvds

+關注

關注

2文章

1110瀏覽量

67052 -

隔離器

+關注

關注

4文章

817瀏覽量

39033

發布評論請先 登錄

ADN4621是否支持單端LVDS信號傳輸?是否還能支持單端的LVDS(單線LVDS)信號隔離?

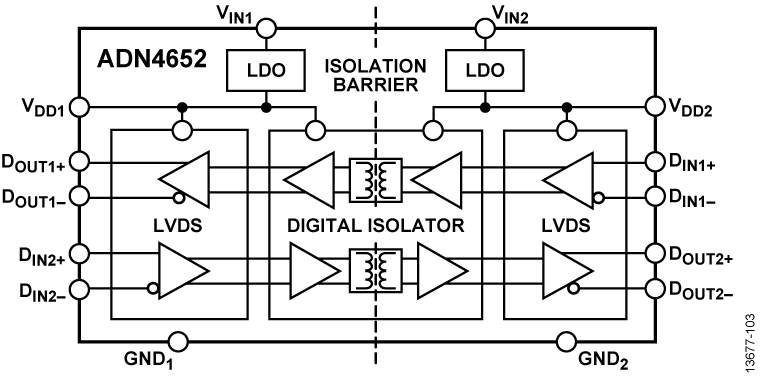

ADN4652 5 kV/3.75 kV rms、600 Mbps雙通道LVDS隔離器

ADuM1280/ADuM1281/ADuM1285/ADuM1286:3 kV RMS雙通道數字隔離器

ADN4650/ADN4651/ADN4652: 5 kV RMS、600 Mbps雙通道LVDS隔離器

UG-933:評估ADN4650 5 kV rms、600 Mbps LVDS隔離器(SOIC_W)

UG-900:評估ADN4651/ADN4652 5 kV rms、600 Mbps LVDS隔離器(SOIC_W)

ADuM220N/ADuM221N/ADuM225N/ADuM226N:5.0 kV rms雙通道數字隔離器數據表

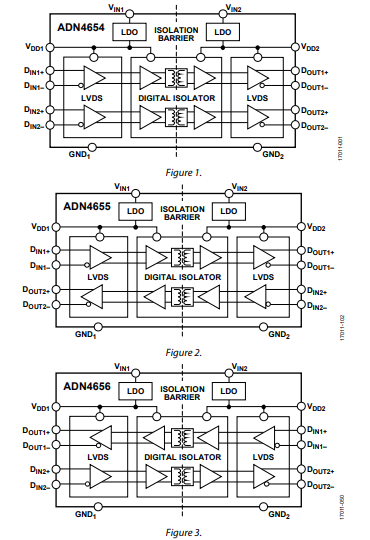

ADN4654/ADN4655/ADN4656:5 kV RMS和3.75 kV RMS,雙通道LVDS Gigabit Sigabit數據Sheet

UG-第1373:評估ADN4654/ADN4655/ADN4656 5 kV rms雙通道LVDS千兆隔離器

3 kV RMS雙通道數字隔離器ADuM1280數據手冊

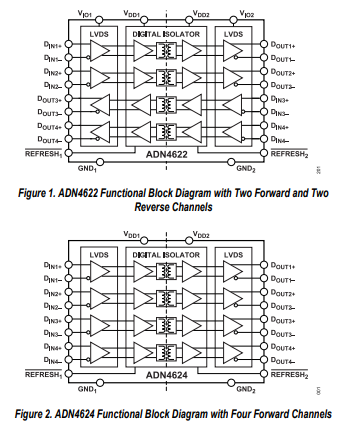

ADN4622/ADN4624 5.7 kV rms/1.5 kV rms、四通道 LVDS 2.5 千兆位隔離器技術手冊

ADN4654/ADN4655/ADN4656 5kV RMS/3.75 kV RMS、雙通道LVDS千兆位隔離器技術手冊

ADN4620/ADN4621 7.5 kV RMS/3.75 kV rms雙通道LVDS 2.5 Gbps隔離器技術手冊

ADN4620/ADN4621 7.5 kV RMS/3.75 kV rms雙通道LVDS 2.5 Gbps隔離器技術手冊

評論