半導體芯片易受大電流與高電壓現象影響。為實現元件級保護,我們采用片上ESD保護電路來提供安全的靜電放電電流泄放路徑。靜電放電(ESD)是電子設備面臨的常見威脅。當ESD事件發生時,一定量的電荷會在兩個物體間轉移(例如從人體到集成電路)。這種電荷轉移可能導致極高電流在極短時間內流經芯片,若器件無法快速耗散能量就會造成損壞。

ESD威脅貫穿產品全生命周期:在制造組裝階段、終端用戶使用過程或設備維護期間都可能發生。隨著移動設備、汽車電子、工業及醫療應用等新興技術的快速發展,市場對芯片級ESSD防護提出了獨特需求。ESD保護是電子元件的強制性要求,其設計是半導體行業的重點課題。為確保可靠運行,需同時在元件級和器件級考慮ESD防護措施。

ESD元件測試(ESD模型)

行業標準規定了一系列ESD認證測試來保障系統與元件的可靠性。這些標準詳細規定了測試流程、設備校準及常規驗證程序。本節重點介紹元件級測試,通過這些測試是產品獲得認證并上市的前提條件。

模擬日常元件ESD事件的測試模型(各自代表特定物理現象)包括:

? 人體模型(HBM)

? 機器模型(MM)

? 充電器件模型(CDM)

? 傳輸線脈沖測試(TLP)

【人體模型】

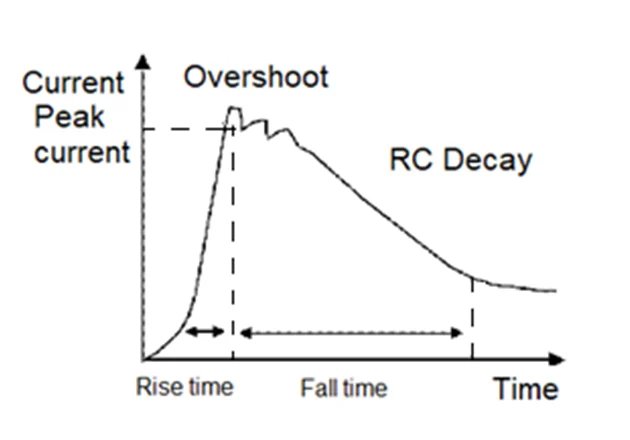

當帶電人體用手指接觸元件時就會產生人體模型放電。這種最古老的ESD測試最初為采礦行業開發,模擬電荷從手指轉移到集成電路引腳(其他引腳接地)的過程。最新數據顯示HBM很少能模擬真實ESD事件——現代封裝尺寸通常小到無法用手指操作,且大型元件制造多采用自動化設備,人工接觸元件的情況極少。圖1展示了HBM脈沖波形。

圖1

圖1【機器模型脈沖】

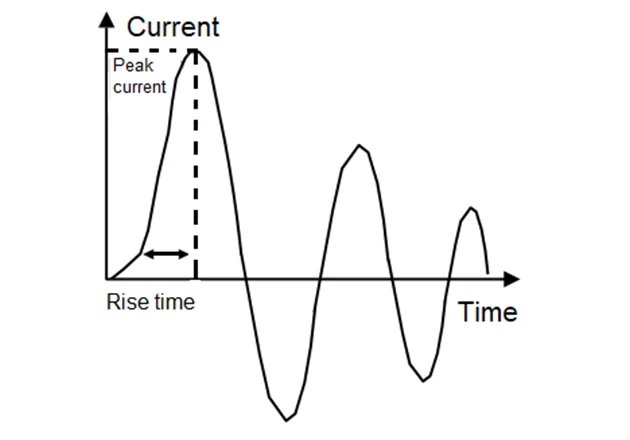

機器模型(MM)用于模擬帶電金屬物體接觸IC引腳的ESD事件。圖2顯示其脈沖波形。HBM與MM模型的共同點是電荷都轉移至受測元件。

圖2

圖2【充電器件模型】

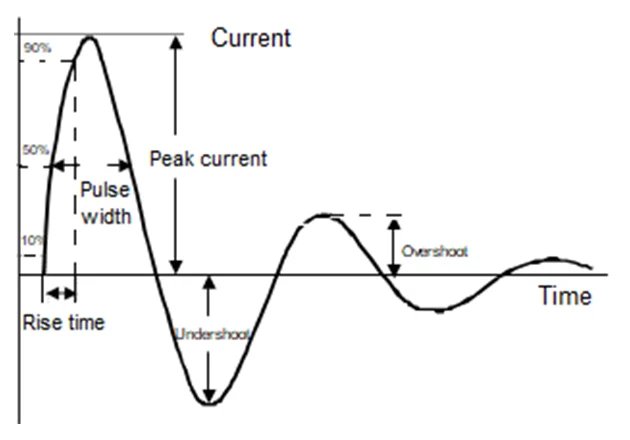

當帶電器件接觸接地物體時就會產生充電器件模型(CDM)。該測試中元件作為電荷源,通過接物體放電。CDM模型能復現組件在工廠和客戶端的失效情況,可檢測IC封裝帶電后通過接地金屬物體放電時的脆弱性。這類放電事件是現代電路ESD失效的主因。圖3呈現CDM電流波形。

圖3

圖3【傳輸線脈沖測試】

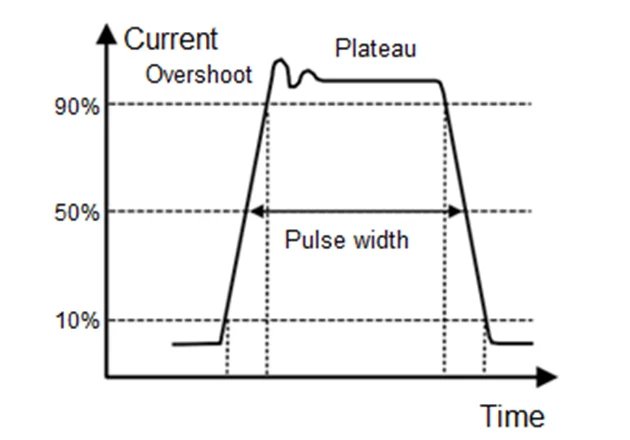

傳輸線脈沖(TLP)測試中,電壓源對同軸電纜充電后,系統會向受測器件釋放一系列類ESD脈沖。該方法可評估器件在ESD應力下的工作性能,既能作為HBM方法的等效替代方案,也能測量ESD特性參數。圖4顯示TLP脈沖波形。

圖4

圖4常見ESD失效

ESD失效具有破壞性,可導致IC芯片立即功能失常。結區和氧化層尤其易損,主要失效機制包括:

硅結燒毀:最常見的HBM失效機制,ESD瞬態能量注入會導致結擊穿

氧化層擊穿:當介質層承受高壓應力時,介電擊穿會引發電流傳導,產生的熱斑可熔化介質、硅等材料

金屬化燒毀:當I2R發熱達到材料熔點時互連通路斷裂,通常是結/氧化層失效后的次生效應

片上ESD保護器件

片上ESD保護結構通過提供到地總線/電源軌的安全泄放路徑,保護核心電路的輸入/輸出及電源引腳。這些結構在系統正常工作時關閉,ESD事件發生時迅速開啟。保護電路會在事件期間將引腳電壓鉗位在低位,電流泄放后恢復關閉狀態,且確保器件不受損。

當工藝限制無法實現片上保護時,可采用線纜、連接器、陶瓷載體或電路板上的片外保護方案。某些情況下,經優化的定制方案能降低成本。優質ESD保護器件需具備四大特性:

? 魯棒性

? 有效性

? 響應速度

? 電路透明性

保護電路不僅要堅固有效,其開啟速度還必須快于被保護主電路,同時不能影響主電路性能。

ESD電路基礎構件

保護鉗位電路有多種實現技術,選擇取決于工藝和設計約束。三種常用ESD保護器件為:

二極管:結構最簡單,正向偏置時滿足低壓ESD應用需求(導通電壓低、導通電阻小、電流處理能力強),但反向偏置時性能不佳且漏電流較大

柵極接地NMOS(GGNMOS):通過特殊版圖設計優化ESD性能,可工作于主動模式或回滯模式(后者能以低壓維持大電流,但魯棒性較差)

可控硅整流器(SCR):憑借雙極導通機制具有最優魯棒性,但存在閂鎖風險(需通過設計控制風險)

注:二極管屬無回滯型器件,而SCR和GGNMOS具有回滯特性。

片上ESD保護策略

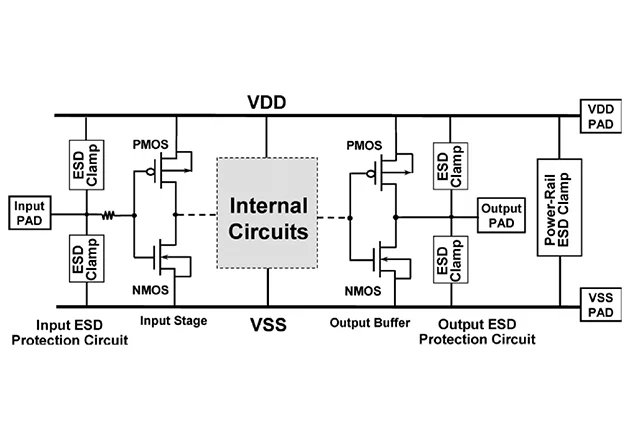

ESD保護策略包括鉗制過應力電壓,以及利用片上保護結構提供電流泄放路徑。輸入/輸出及電源焊盤均需配置保護電路,這些元件正常工作時保持休眠狀態,僅當檢測到電壓瞬變時才激活泄放通道。圖5展示了典型的ESD保護電路布局,包含以下保護組件:

圖5

圖5? 輸入焊盤到地(Vss)

? 輸入焊盤到電源軌(Vdd)

? 輸出焊盤到地(Vss)

? 輸出焊盤到電源軌(Vdd)

? 電源軌(Vdd)到地(Vss)

該技術適用于CMOS、BiCMOS及III-V族化合物等主要工藝。

IC接地技術綜述

靜電放電本質是不同電勢物體間的電荷轉移現象,其快速能量釋放會損壞IC。ESD防護通過建立安全泄放路徑、耗散能量及電壓鉗位來實現保護。隨著半導體尺寸持續縮小,ESD失效已成為更嚴峻的可靠性挑戰。驗證電路設計的ESD免疫力和可靠性至關重要,主要元件級標準包括HBM、MM和CDM。典型ESD防護器件包括二極管、GGNMOS和SCR。片上保護器件在常態下關閉,達到閾值電壓后導通電流,從而保護內部電路免受損傷。

-

ESD

+關注

關注

50文章

2290瀏覽量

175728 -

電路設計

+關注

關注

6705文章

2537瀏覽量

214613 -

半導體芯片

+關注

關注

61文章

932瀏覽量

71398

發布評論請先 登錄

半導體芯片的ESD靜電防護:原理、測試方法與保護電路設計

半導體芯片的ESD靜電防護:原理、測試方法與保護電路設計

評論