概述

AD9912是一款集成14位數模轉換器(DAC)的直接數字頻率合成器(DDS)。AD9912具有一個48位頻率調諧字(FTW),可以合成步長不超過4μHz的頻率。通過調整DAC系統時鐘可以實現絕對頻率精度。

AD9912還集成了系統時鐘鎖相環(PLL),支持低至25MHz的系統時鐘輸入。

AD9912在?40℃至+85℃工業溫度范圍內工作。

數據表:*附件:AD9912 1 GSPS直接數字頻率合成器,內置14位數模轉換器技術手冊.pdf

應用

特性

- 1 GSPS內部時鐘速度(直接輸出高達400MHz)

- 集成1 GSPS 14位DAC

- 48位頻率調諧字,分辨率為4μHz

- 差分HSTL比較器

- 靈活的系統時鐘輸入接受晶振或外部基準時鐘

- 片內低噪聲PLL REFCLK乘法器

- 2個SpurKiller通道

- 低抖動時鐘倍頻器,頻率高達750 MHz

- 單端CMOS比較器;頻率 <150 MHz

- 可編程輸出分頻器,支持CMOS輸出

- 串行I/O控制

- 出色的動態性能

- 軟件控制關斷功能

- 采用兩種64引腳LFCSP封裝

- 殘余相位噪聲(250 MHz)

- 10 Hz偏移:-113 dBc/Hz

- 1 kHz偏移:-133 dBc/Hz

- 100 kHz偏移:-153 dBc/Hz

- 40 MHz偏移:-161 dBc/Hz

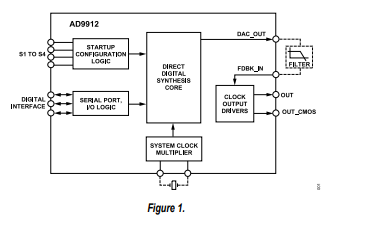

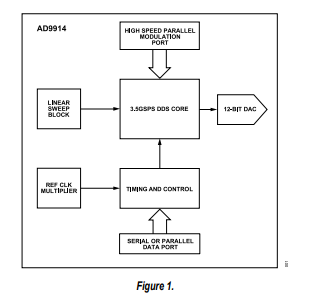

框圖

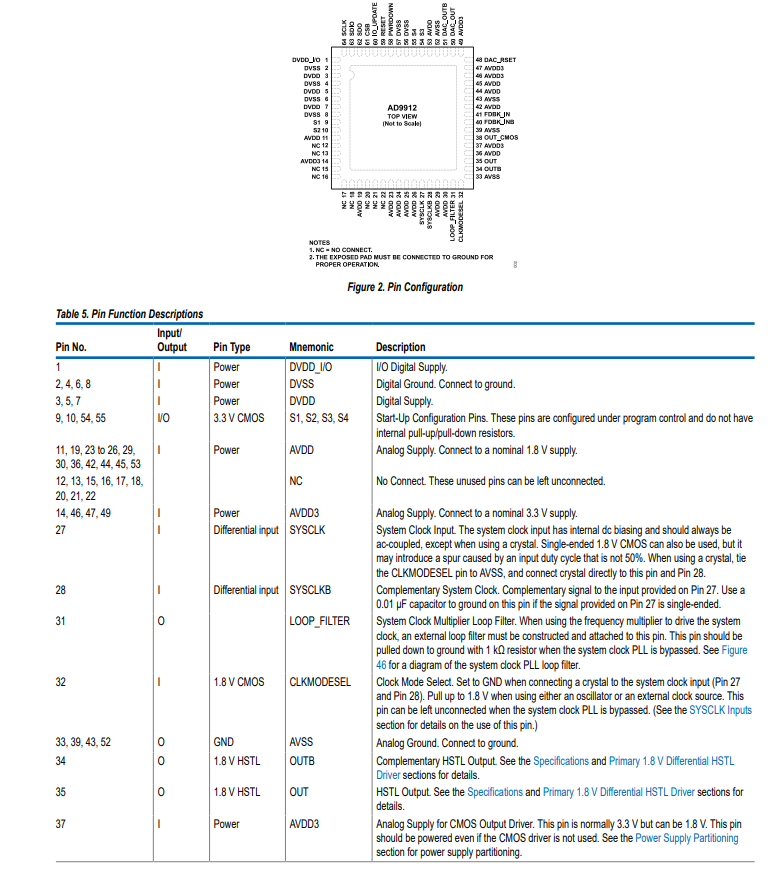

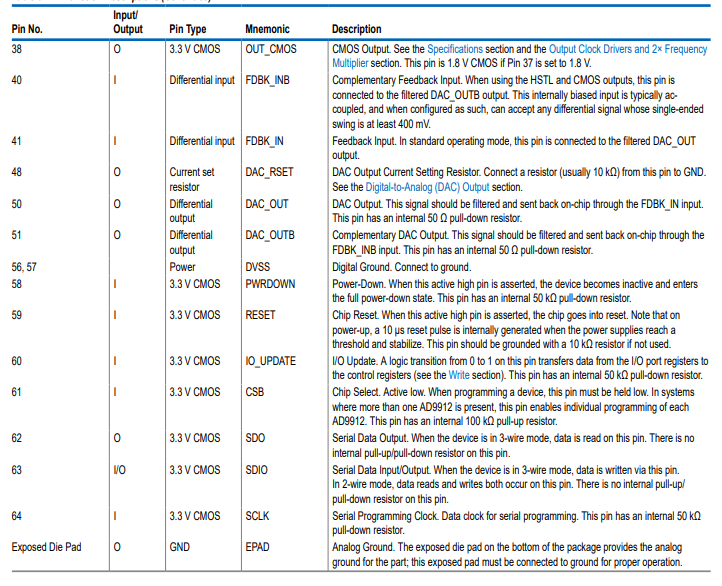

引腳配置描述

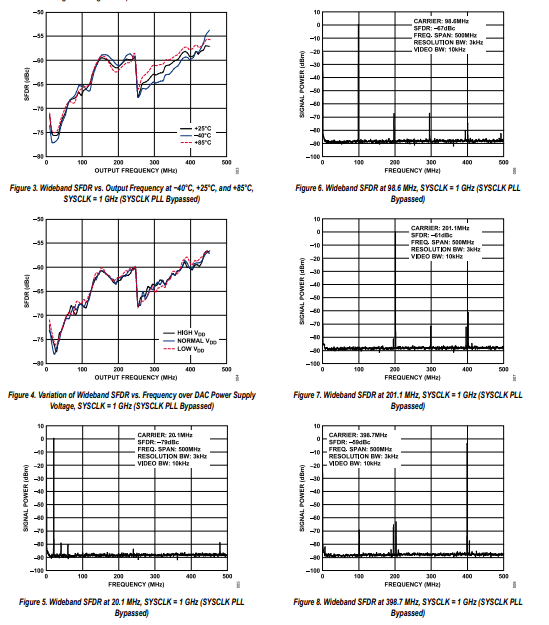

典型性能特征

操作理論

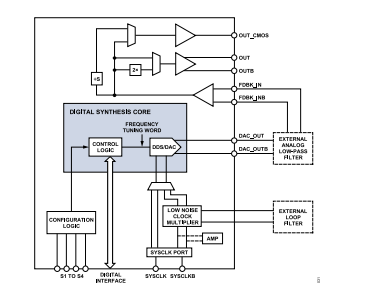

圖39. 詳細框圖

AD9912是一款高性能、低噪聲的14位直接數字頻率合成器(DDS)時鐘合成器,集成了比較器,適用于需要產生靈活、精細調諧的方波或正弦波輸出信號的應用。通過直接數字合成器(DDS)與集成數模轉換器(DAC),實現了數控振蕩器(DCO)功能,由系統時鐘驅動。

該器件采用基于鎖相環(PLL)的倍頻器,可使用低成本、低頻源作為系統時鐘。為獲得最佳抖動性能,應繞過系統時鐘PLL,并提供低噪聲、高頻系統時鐘。根據采樣理論,DDS的輸出頻率上限為采樣時鐘頻率(fs)的50%(fs為DAC采樣速率),但實際應用中,通常建議上限為40%fs,以確保所需片外重構濾波器的選擇性。

重構濾波器的輸出信號可反饋至AD9912進行進一步處理。輸出電路包括HSTL和CMOS輸出緩沖器,以及頻率倍增器,適用于需要高于DDS奈奎斯特頻率的應用。

AD9912還提供預編程的頻率配置文件,允許用戶在無需編程器件的情況下進行頻率調諧。以下各節將分別介紹各個功能模塊。

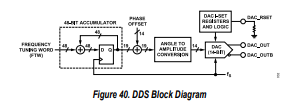

直接數字合成器(DDS)

DDS生成的正弦波頻率由頻率調諧字(FTW)確定(即數字值)。與模擬正弦波發生器不同,DDS使用數控模塊并在采樣系統中運行。因此,它需要一個采樣時鐘(fs),作為DDS的基本定時源。累加器相當于一個模數為2^48的計數器,其可編程步長由頻率調諧字(FTW)決定。DDS的框圖如圖40所示。

DDS的輸入是一個48位的FTW,為累加器提供速率值。在每個fs周期,累加器將FTW的值加到其運行總和上。例如,給定FTW = 5,累加器在每個fs周期將增加5。當累加器達到其容量上限(在這種情況下為2^48 )時,它會溢出并回滾,保留溢出部分。累加器回滾的平均速率決定了輸出正弦波的頻率。以下公式定義了累加器的回滾速率,并確定了DDS的輸出頻率(fDDS):

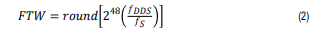

對該公式求解FTW可得:

例如,給定fs = 1 GHz,fDDS = 19.94 MHz,則FTW = 5,471,873,547.255(0x04FA05143B7F )。

-

dac

+關注

關注

43文章

2396瀏覽量

193321 -

DDS

+關注

關注

22文章

672瀏覽量

154236 -

數模轉換器

+關注

關注

14文章

1062瀏覽量

84077 -

數字頻率合成器

+關注

關注

0文章

31瀏覽量

6530

發布評論請先 登錄

使用AD9912直接數字頻率合成器的AD9912A/PCBZ評估板

AD9914BCPZ直接數字頻率合成器

AD9914BCPZ數字頻率合成器產品介紹

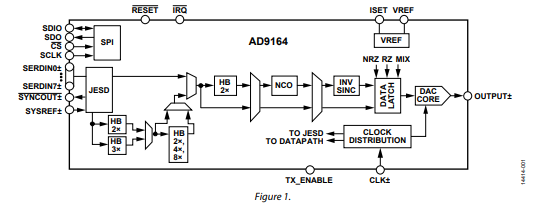

高性能16位數模轉換器AD9164怎么樣?

AD9915: 2.5 GSPS直接數字頻率合成器,內置12位數模轉換器數據手冊

AD9164 16位、12 GSPS、RF DAC和直接數字頻率合成器技術手冊

AD9912 1 GSPS直接數字頻率合成器,內置14位數模轉換器技術手冊

AD9912 1 GSPS直接數字頻率合成器,內置14位數模轉換器技術手冊

評論