概述

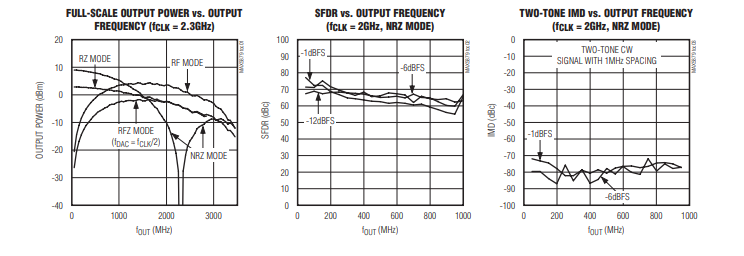

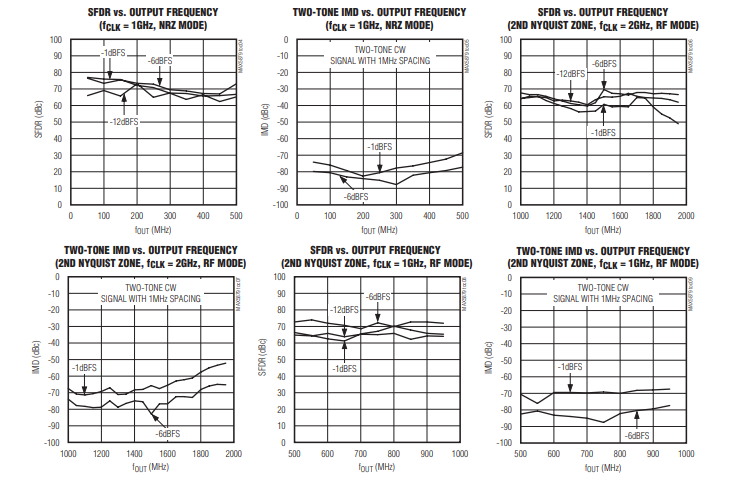

MAX5879是高性能、14位、2.3Gsps數(shù)/模轉(zhuǎn)換器(DAC),在基帶和高階奈奎斯特區(qū)用于合成高頻和寬帶信號。2.3Gsps刷新速率,結合可選擇的頻率響應模式(NRZ、RZ、RF和RFZ),允許生成超過2GHz輸出頻率的數(shù)字信號。獨特的RFZ模式可產(chǎn)生高達6階的奈奎斯特信號,刷新速率可達1150Msps。器件具有優(yōu)異的雜散、噪聲和交調(diào)失真性能,可以直接合成超過1GHz的信號帶寬。

數(shù)據(jù)表:*附件:MAX5879 14位、2.3Gsps直接RF合成DAC,提供可選擇頻響技術手冊.pdf

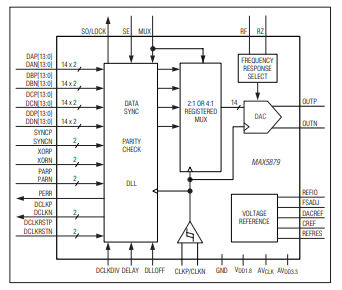

器件具有四路14位、多路復用、低壓差分信號(LVDS)輸入端口,每個端口工作速率達1150Mwps。DAC工作時鐘頻率(f CLK )可達2.3GHz。器件具有一個可選擇的2:1或4:1輸入多路復用器,允許用戶選擇兩個數(shù)據(jù)端口(每端口速率高達1150Mwps),或四個數(shù)據(jù)端口(每端口速率高達575Mwps)。相應地,每個端口的輸入數(shù)據(jù)速率為DAC刷新速率的1/2或1/4。器件的延遲鎖相環(huán)(DLL)可方便器件與FPGA或ASIC進行數(shù)據(jù)同步。奇偶輸入和奇偶誤差標識輸出用于檢測數(shù)據(jù)源與DAC之間的誤碼。器件還具有數(shù)據(jù)時鐘復位電路,用于對齊多個DAC數(shù)據(jù)采集時鐘。

器件具有四個可選擇的頻率響應輸出模式:

- 不歸零(NRZ)模式,在第一段奈奎斯特區(qū)提供最高動態(tài)范圍/輸出功率。

- 歸零(RZ)模式,在第一、第二和第三段奈奎斯特區(qū)調(diào)整SNR,以改善增益平坦度。

- 射頻(RF)模式,在第二和第三奈奎斯特區(qū)提供較高的SNR和優(yōu)異的動態(tài)性能。

- 射頻歸零(RFZ)模式,f

CLK/2最大刷新速率下,在第三至第六奈奎斯特區(qū)提供高動態(tài)范圍并改善增益平坦度。

器件采用電流型DAC架構,集成50Ω差分輸出匹配電阻,確保器件的最佳動態(tài)性能。器件工作在3.3V和1.8V電源,40mA滿量程電流下耗電1.8W;80mA滿量程電流下耗電2.3W。器件工作在-40°C至+85°C擴展級溫度范圍,采用256焊球(17mm x 17mm) CSBGA封裝。

應用

特性

- 業(yè)界領先性能

- 高輸出功率:9dBm (CW)

- 頻率響應模式:NRZ、RZ、RF、RFZ

- 2GHz輸出帶寬

- 2:1或4:1多路LVDS輸入

- 每個端口達1150MHz

- 工作在1倍或2倍數(shù)據(jù)速率

- 片上DLL用于輸入數(shù)據(jù)同步

- 復位功能用于多路DAC同步

框圖

典型操作特性

應用信息

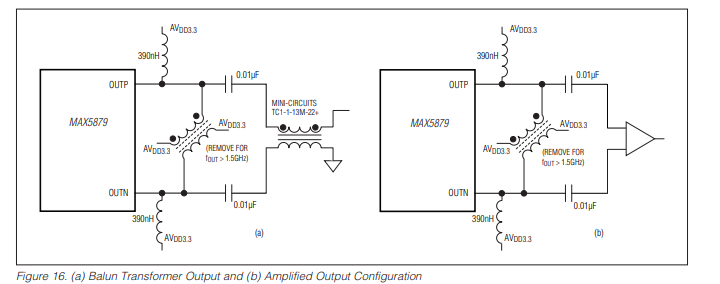

輸出耦合

OUTP和OUTN之間的差分電壓可使用變壓器或差分放大器轉(zhuǎn)換為單端電壓。數(shù)模轉(zhuǎn)換器(DAC)輸出應上拉至AVDD3.3 。建議使用偏置抽頭,利用分立電感和電容將輸出上拉。圖16中展示了推薦的輸出電路配置。為實現(xiàn)最大帶寬并盡量減小變壓器次級側接地引線上的電感,連接接地層時請使用極短的走線和多個過孔。

接地、旁路、電源及電路板布局注意事項

接地和電源去耦會對器件性能產(chǎn)生顯著影響。不需要的數(shù)字串擾可能會通過輸入、基準、電源和接地連接耦合進來,從而影響動態(tài)性能。高速高頻應用的正確接地和電源去耦準則應嚴格遵守。這有助于減少電磁干擾(EMI)和內(nèi)部串擾,而它們會顯著影響器件的動態(tài)性能。

使用具有獨立接地層和電源層的多層印刷電路板(PCB)是必要的。建議將模擬輸出和時鐘輸入作為受控阻抗微帶線在電路板頂層布線。

直接布設在接地層上方,且模擬輸出(OUTP、OUTN)信號和時鐘輸入(CLKP、CLKN)不使用過孔。根據(jù)走線長度和工作條件,可能需要使用低損耗電介質(zhì)材料(如ROGERS RO4003)作為頂層電介質(zhì)材料。數(shù)據(jù)時鐘(DCLKP、DCLKN)的布線應使耦合到時鐘輸入和DAC輸出的干擾最小化。

數(shù)字信號應作為受控阻抗走線布設在接地層之間。數(shù)字信號應盡量遠離敏感的模擬輸入、基準輸入感應線、共模輸入和時鐘輸入。尤其重要的是,要盡量減小數(shù)字信號與時鐘之間的耦合,以優(yōu)化高速輸出頻率下的動態(tài)性能。對稱的時鐘輸入和模擬輸出走線設計對于最小化失真和優(yōu)化DAC的動態(tài)性能至關重要。數(shù)字信號路徑應盡量短,走線長度應匹配,以避免數(shù)據(jù)延遲失配。

該器件支持三個獨立的電源輸入,分別用于模擬3.3V(AVDD3.3)、開關電源(VDD1.8)和時鐘(AVCLK)電路。每個AVDD3.3、VDD1.8和AVCLK輸入都應在盡可能靠近輸入的位置連接一個獨立的47nF電容器,其另一端應連接到對應的接地層,以盡量減小環(huán)路電感。這三個電源電壓也應在其離開印刷電路板的位置去耦,可使用鉭電容或電解電容,并添加鐵氧體磁珠,以及形成π型網(wǎng)絡的去耦電容,這樣也能改善性能。

-

dac

+關注

關注

43文章

2378瀏覽量

193009 -

數(shù)模轉(zhuǎn)換器

關注

14文章

1052瀏覽量

83964 -

MAX5879

+關注

關注

0文章

2瀏覽量

5807

發(fā)布評論請先 登錄

基于RF DAC的RF直接變頻發(fā)送器實現(xiàn)設計

請問哪種Xylinx產(chǎn)品具有足夠的BlockRAM性能?

MAX5881直接RF合成DAC與FPGA的接口

MAX5881直接RF合成DAC與FPGA的接口

MAX5879高性能數(shù)模轉(zhuǎn)換器(DAC)

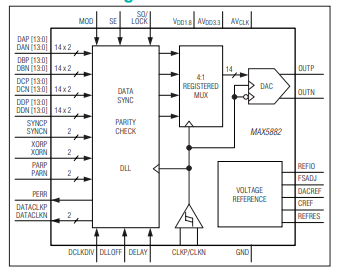

MAX5882 14位,4.6Gsps下行電纜直接RF-DAC

利用MAX5879 DAC實現(xiàn)RF直接變頻發(fā)送器 提升系統(tǒng)穩(wěn)定性

AD9910: 1 GSPS、14位、3.3 V CMOS直接數(shù)字頻率合成器

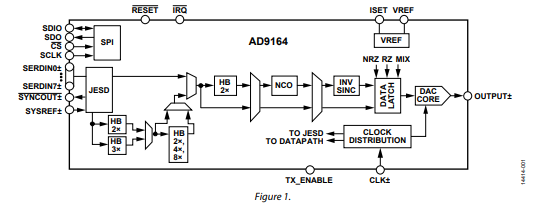

AD9164:16位、12 GSPS、RF DAC和直接數(shù)字合成器數(shù)據(jù)表

AD9174:雙16位12.6 GSPS RF DAC和直接數(shù)字合成器數(shù)據(jù)表

UG-475:評估采用14位DAC的AD9912 1 GSPS直接數(shù)字頻率合成器

AD9164 16位、12 GSPS、RF DAC和直接數(shù)字頻率合成器技術手冊

MAX5882 14位、4.6Gsps電纜下行RF直接合成DAC技術手冊

MAX5879 14位、2.3Gsps直接RF合成DAC,提供可選擇頻響技術手冊

MAX5879 14位、2.3Gsps直接RF合成DAC,提供可選擇頻響技術手冊

評論