概述

AD9161是一款高性能11位數(shù)模轉(zhuǎn)換器(DAC),支持最高達6 GSPS的數(shù)據(jù)速率。DAC內(nèi)核基于一個四通道開關(guān)結(jié)構(gòu)配合2倍插值濾波器,使DAC的有效更新速率在某些模式下高達12 GSPS。高動態(tài)范圍和帶寬使這些DAC非常適合最苛刻的高速射頻(RF)DAC應(yīng)用。

數(shù)據(jù)表:*附件:AD9161 AD9162 11位、12 GSPS、RF數(shù)模轉(zhuǎn)換器技術(shù)手冊.pdf

在基帶模式下,元件的寬帶寬能力和高動態(tài)范圍相結(jié)合,在最小兩個載波至最大1.794 GHz的滿量程頻譜范圍內(nèi)可支持DOCSIS 3.1電纜基礎(chǔ)設(shè)施兼容性。2倍插值濾波器(FIR85)使AD9161/AD9162針對較低數(shù)據(jù)速率和轉(zhuǎn)換器時鐘進行配置,可降低系統(tǒng)總體功耗和濾波要求。在Mix-Mode^?^ 操作模式中,AD9161/ AD9162可在高達7.5 GHz的二階和三階奈奎斯特區(qū)內(nèi)重構(gòu)RF載波,同時仍保持出色的動態(tài)范圍。輸出電流可以在8 mA至38.76 mA范圍內(nèi)進行編程。AD9161/AD9162數(shù)據(jù)接口由最多八個JESD204B串行器/解串器(SERDES)通道組成,可對其通道速度和通道數(shù)進行編程,從而實現(xiàn)應(yīng)用靈活性。

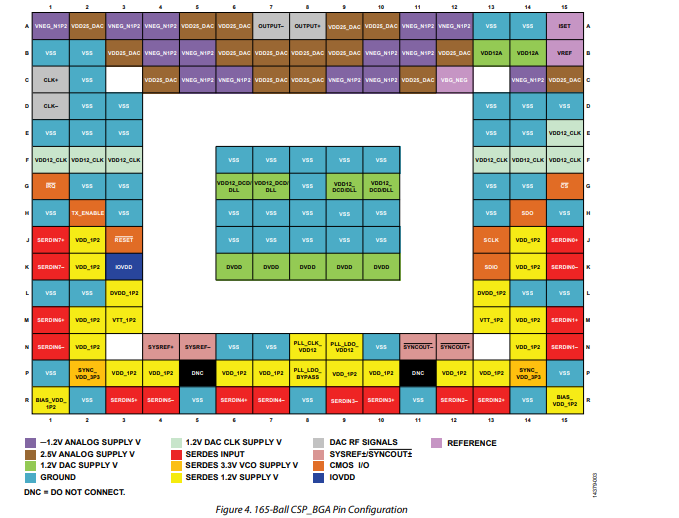

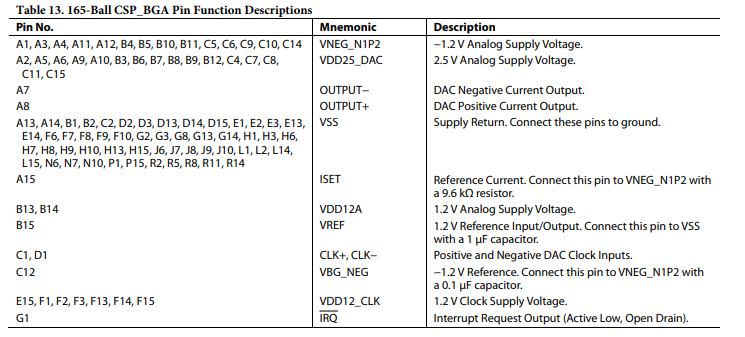

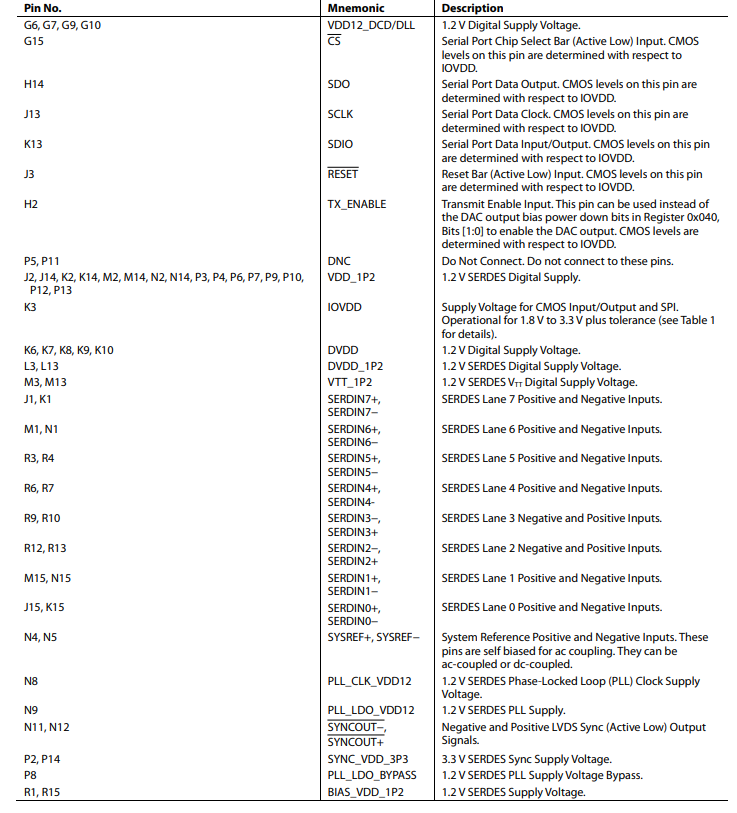

串行外設(shè)接口(SPI)可配置AD9161并監(jiān)控所有寄存器的狀態(tài)。AD9161提供165引腳、8.0 mm × 8.0 mm、0.5 mm間距、CSP_BGA和169引腳、11 mm × 11 mm、0.8 mm間距、CSP_BGA兩種封裝。

產(chǎn)品特色

- 高動態(tài)范圍和信號重建帶寬支持高達7.5 GHz的RF信號頻率合成。

- 高達八個通道JESD204B SERDES接口,支持靈活的通道數(shù)和通道速度。

- 帶寬和動態(tài)范圍可滿足DOCSIS 3.1余量兼容性要求。

應(yīng)用

- 寬帶通信系統(tǒng)

- DOCSIS 3.1電纜調(diào)制解調(diào)器終端系統(tǒng)(CMTS)/視頻點播(VOD)/邊沿正交幅度調(diào)制(EQAM)

- 無線通信基礎(chǔ)設(shè)施

- 儀器儀表、自動測試設(shè)備(ATE)

- 雷達和干擾發(fā)射器

特性

- DAC更新速率高達12 GSPS(最小值)

- 6 GSPS直接RF頻率合成(最小值)

- 直流至2.5 GHz(基帶1倍旁路模式)

- 直流至6 GHz(2倍不歸零(NRZ)模式)

- 1.5 GHz至7.5 GHz(混合模式)

- 可旁路的插值(1倍或旁路模式)

- 2×, 3×, 4×, 6×, 8×, 12×, 16×, 24×

- 出色的動態(tài)性能

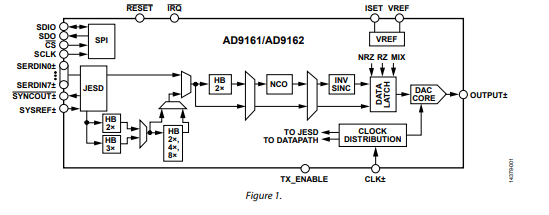

框圖

引腳配置描述

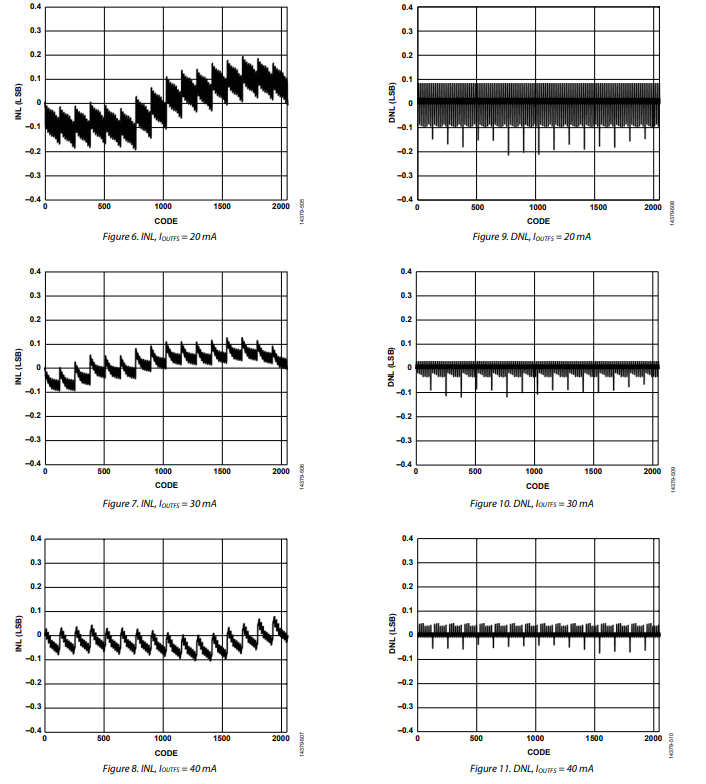

典型性能特征

AD9161/AD9162 分別是具有串行解串器(SERDES)接口的 11 位和 16 位單路射頻數(shù)模轉(zhuǎn)換器(DAC)。圖 1 展示了 AD9161/AD9162 的詳細(xì)功能框圖。12 條高速串行通道將數(shù)據(jù)傳輸至 DAC,數(shù)據(jù)速率最高可達 1.56 Gbps,實輸入或 2.5 Gbps 復(fù)輸入。

與 LVDS 或 CMOS 接口相比,SERDES 接口簡化了印刷電路板(PCB)布局,并降低了設(shè)備的時鐘要求。

輸入數(shù)據(jù)的時鐘源自 DAC 時鐘,即設(shè)備時鐘(符合 JESD204B 規(guī)范要求)。該設(shè)備時鐘由高保真外部 DAC 采樣時鐘提供。通過片上時鐘輸入調(diào)整,可使用 SPI 端口優(yōu)化 DAC 性能。設(shè)備可配置為在單通道、雙通道、三通道、四通道、六通道或八通道模式下運行,具體取決于所需的輸入數(shù)據(jù)速率。

AD9161/AD9162 的數(shù)字?jǐn)?shù)據(jù)路徑提供旁路(1x)模式(僅 AD9162 支持)以及多種插值模式(2x、3x、4x、6x、8x、12x、16x 和 24x),這些模式可通過具有 80%或 90%帶寬的可編程半帶濾波器實現(xiàn),且三個后續(xù)半帶濾波器(均為 90%帶寬)和 DAC 采樣率為 6 Gsps。提供了一個反 sinc 濾波器來補償 sinc 相關(guān)的滾降。額外的半帶濾波器 FIR85 采用四開關(guān)架構(gòu),可在時鐘下降沿進行插值,從而在 2x NRZ 模式下有效使 DAC 更新速率翻倍。48 位可編程數(shù)控振蕩器(NCO)可實現(xiàn)信號的近無限精度數(shù)字頻率偏移。NCO 可與僅在 AD9162 中可用的時鐘同步,也可與來自 SERDES 接口和數(shù)字?jǐn)?shù)據(jù)路徑的數(shù)字?jǐn)?shù)據(jù)同步。100 MHz 的 SPI 字接口能夠快速更新 NCO 的頻率設(shè)置字。

AD9161/AD9162 DAC 內(nèi)核提供全差分電流輸出,標(biāo)稱滿量程電流為 38.76 mA。滿量程輸出電流 I_{OUTFS} 用戶可在 8 mA 至 38.76 mA 之間調(diào)節(jié),通常為該范圍中間值。

差分電流輸出是互補的。DAC 采用專利的四開關(guān)架構(gòu),使 DAC 解碼器能夠?qū)⑤敵鲱l率范圍擴展到第二和第三奈奎斯特區(qū),可在混頻模式、歸零(RZ)模式和 2x NRZ 模式(啟用 FIR85 時)下工作。在 1x 旁路(僅 AD9162 支持)和 NRZ 模式下運行時,DAC 輸出信號范圍為 0 Hz 至 2.5 GHz。混頻模式可用于訪問 1.5 GHz 至 7.5 GHz 的輸出信號范圍。在 2x NRZ 模式下,通過 NCO 將信號偏移至高達 1.8 GHz 的瞬時帶寬,插值模式下輸出信號范圍為 0 Hz 至 6 GHz。

AD9161/AD9162 支持多芯片同步功能,既能同步多個 DAC,又能為 DAC 建立恒定且可確定的延遲(延遲鎖定)路徑。每個 DAC 的延遲在多個 DAC 時鐘周期內(nèi)保持恒定,以實現(xiàn)鏈路建立。外部對齊(SYNCEXF)信號使 AD9161/AD9162 Subclass 1 符合 SYRESREF 信號鏈路要求。系統(tǒng)中提供了多種信號處理模式。

SPI 用于配置各種功能模塊并監(jiān)控其狀態(tài)。不同功能模塊和數(shù)據(jù)接口有特定的操作順序要求(詳見啟動順序部分)。評估板軟件包中包含簡單的 SPI 初始化例程,用于建立 JESD204B 鏈路。本數(shù)據(jù)手冊詳細(xì)介紹了 AD9161/AD9162 的各個模塊,描述了 JESD204B 接口、控制參數(shù)和各種寄存器,用于設(shè)置和監(jiān)控設(shè)備。推薦的啟動例程可可靠地建立數(shù)據(jù)鏈路。

JESD204B串行數(shù)據(jù)接口

JESD204B概述

AD9161/AD9162有八個JESD204B數(shù)據(jù)端口用于接收數(shù)據(jù)。這八個JESD204B端口可作為JESD204B鏈路的一部分進行配置,該鏈路使用單個系統(tǒng)參考時鐘(SYREF±)和設(shè)備時鐘(CLKC±)。

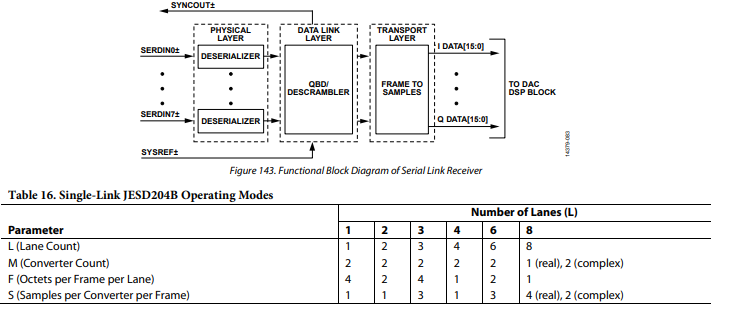

JESD204B串行接口硬件由三層組成:物理層、數(shù)據(jù)鏈路層和傳輸層。硬件的這些部分將在后續(xù)章節(jié)中進行描述,包括如何配置接口的各個方面。圖143展示了AD9161/AD9162串行接口中實現(xiàn)的通信層,用于恢復(fù)時鐘和數(shù)據(jù)去斜,以及在數(shù)據(jù)被發(fā)送到設(shè)備的數(shù)字信號處理部分之前對數(shù)據(jù)進行解擾。

物理層在發(fā)送器(Tx)和接收器(Rx)之間建立可靠的通道;數(shù)據(jù)鏈路層負(fù)責(zé)將數(shù)據(jù)進行打包和解包。傳輸層接收J(rèn)ESD204B幀并將其轉(zhuǎn)換為數(shù)字樣本。

一系列JESD204B參數(shù)(L、F、K、M、N、NP、S、HD)定義了數(shù)據(jù)的打包方式,并告知設(shè)備如何將串行數(shù)據(jù)轉(zhuǎn)換為樣本。這些參數(shù)在傳輸層部分進行了詳細(xì)定義。AD9161/AD9162還具有解擾選項(有關(guān)更多信息,請參見“解擾器”部分)。

支持的JESD204B參數(shù)的各種組合僅取決于通道數(shù)。因此,通過選擇要使用的通道數(shù),可以確定一組唯一的參數(shù)。此外,插值速率和要使用的通道數(shù)可用于定義配置的其余部分。所需的插值速率和通道數(shù)在寄存器0x110中選擇。

AD9161/AD9162有一個單路DAC輸出;然而,為了在芯片上進行復(fù)信號處理,當(dāng)使用插值時,轉(zhuǎn)換器計數(shù)定義為M = 2。

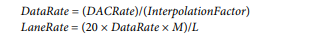

對于特定的應(yīng)用,要使用的轉(zhuǎn)換器數(shù)量(M)和數(shù)據(jù)速率變量是已知的。通道速率變量和通道數(shù)(L)可以按如下方式進行權(quán)衡:

其中,通道速率必須在750 Mbps和12.5 Gbps之間。

實現(xiàn)和恢復(fù)通道的同步非常重要。為了簡化與發(fā)送器的同步,AD9161/AD9162為每個JESD204B鏈路指定一個主同步信號。SYNCOUT±引腳用作主同步信號,用于所有通道。如果任何鏈路中存在同步請求,發(fā)送器會停止向所有鏈路發(fā)送數(shù)據(jù)和時鐘,直到實現(xiàn)同步。

-

dac

+關(guān)注

關(guān)注

43文章

2378瀏覽量

193009 -

RF

+關(guān)注

關(guān)注

65文章

3170瀏覽量

168498 -

數(shù)模轉(zhuǎn)換器

+關(guān)注

關(guān)注

14文章

1052瀏覽量

83964

發(fā)布評論請先 登錄

AD9172BBPZ數(shù)模轉(zhuǎn)換器

請問AD9161能否長時間穩(wěn)定的工作在12Gsps的模式下?

AD9162BBCAZ 數(shù)模轉(zhuǎn)換器

AD9164BBCZ數(shù)模轉(zhuǎn)換器

高速轉(zhuǎn)換器的創(chuàng)新從三個方面改變世界

AD9162BBCZ現(xiàn)貨銷售

高性能16位數(shù)模轉(zhuǎn)換器AD9164怎么樣?

數(shù)模轉(zhuǎn)換器AD9161能否穩(wěn)定的長時間工作在2xNRZ模式下即轉(zhuǎn)換率為12Gsps ?

AD9915: 2.5 GSPS直接數(shù)字頻率合成器,內(nèi)置12位數(shù)模轉(zhuǎn)換器數(shù)據(jù)手冊

AD9914:3.5 GSPS直接數(shù)字頻率合成器,內(nèi)置12位數(shù)模轉(zhuǎn)換器數(shù)據(jù)手冊

AD9119/AD9129:11/14位、5.7GSPS、RF數(shù)模轉(zhuǎn)換器

AD9161/AD9162:11位/16位,12 GSPS,RF數(shù)碼模擬Condertor數(shù)據(jù)Sheet

更改AN-785(AD9161/AD9162/AD9163/AD9164陣列10)

AD9154:四路16位2.4 GSPS TxDAC+?數(shù)模轉(zhuǎn)換器

AD9161/AD9162 11位、12 GSPS、RF數(shù)模轉(zhuǎn)換器技術(shù)手冊

AD9161/AD9162 11位、12 GSPS、RF數(shù)模轉(zhuǎn)換器技術(shù)手冊

評論