概述

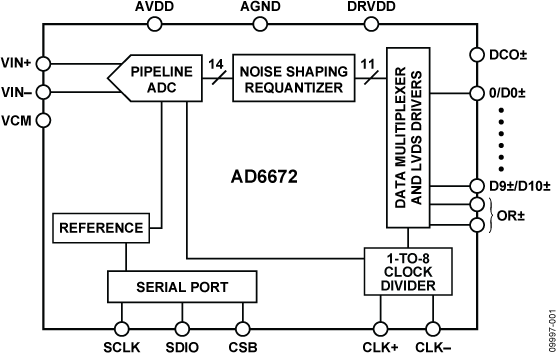

AD6672是一款11位中頻接收機,采樣速率最高可達250 MSPS,旨在為低成本、小尺寸、寬帶寬、多功能通信應用提供解決方案。

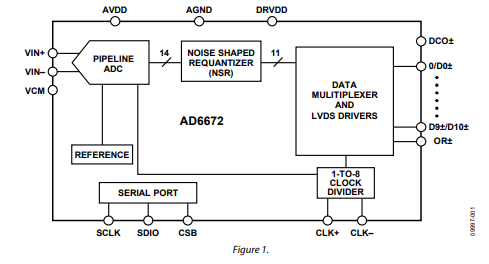

這款ADC內核采用多級、差分流水線架構,并集成了輸出糾錯邏輯。ADC具有寬帶寬輸入,支持用戶可選的各種輸入范圍。集成基準電壓源可簡化設計。占空比穩定器可用來補償ADC時鐘占空比的波動,使轉換器保持出色的性能。

該ADC的內核輸出內部連接到噪聲整形再量化器(NSR)模塊。該器件支持兩種輸出模式,可通過串行端口接口(SPI)選擇。如果使能NSR特性,則在處理ADC的輸出時,AD6672可以在有限的奈奎斯特帶寬區域內實現更高的SNR性能,同時保持11位輸出分辨率。可對NSR模塊進行編程,以提供最高33%的采樣時鐘帶寬。例如,若采樣時鐘速率為250 MSPS,則AD6672在82 MHz帶寬、185 MHz fIN時實現最高73.6 dBFS的SNR。

如果禁用NSR模塊,則ADC數據直接以11位的輸出分辨率提供給輸出端。這種工作模式下,AD6672能夠在整個奈奎斯特帶寬內實現最高66.6 dBFS的SNR。

數據表:*附件:AD6672中頻接收機技術手冊.pdf

應用

特性

- 11位、250MSPS輸出數據速率

- NSR禁用時的性能

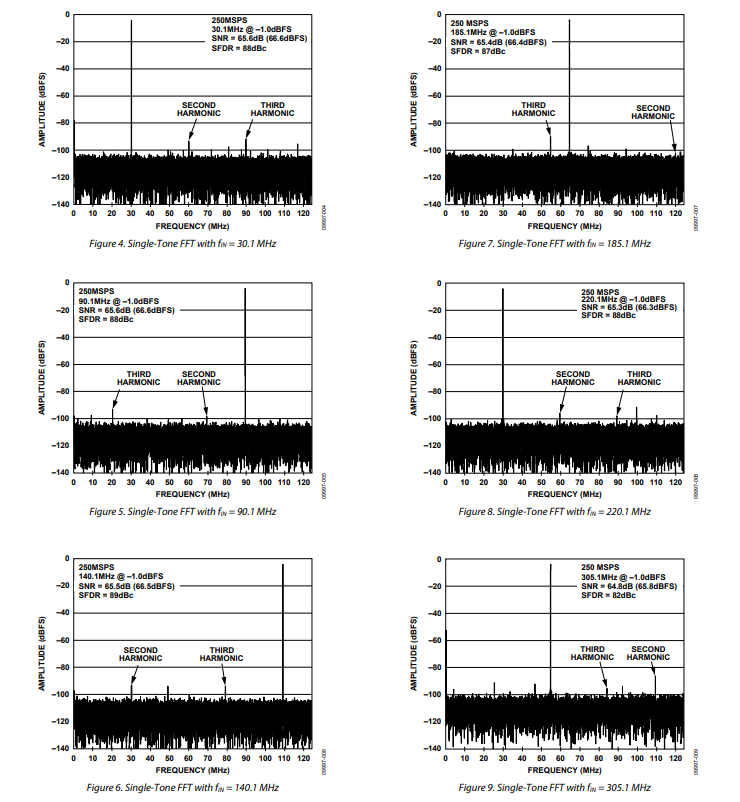

SNR:66.4 dBFS(最高185 MHz、250 MSPS)

SFDR:87 dBc(最高185 MHz、250 MSPS) - 禁用NSR時的性能

SNR:66.4 dBFS(最高185 MHz,250 MSPS)

SFDR:87 dBc(最高185 MHz,250 MSPS) - 總功耗:358 mW(250 MSPS)

- 1.8 V電源電壓

- LVDS(ANSI-644電平)輸出

- 1至8整數輸入時鐘分頻器(最大輸入頻率625MHz)

- ADC內部基準電壓源

- 靈活的模擬輸入范圍:1.4 V p-p至2.0 V p-p(標稱值1.75 V p-p)

- 差分模擬輸入、350 MHz帶寬

- 串行端口控制

- 節能的關斷模式

- 用戶可配置的內置自測(BIST)功能

框圖

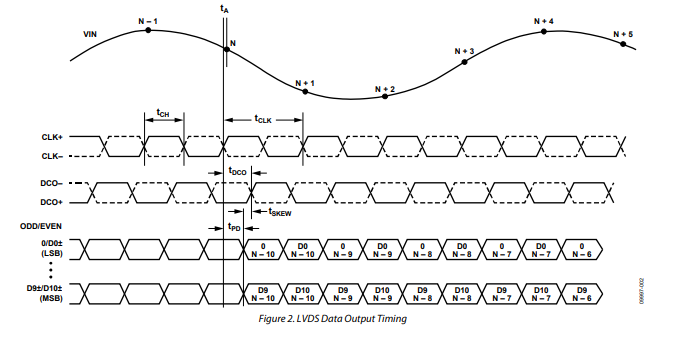

時序圖

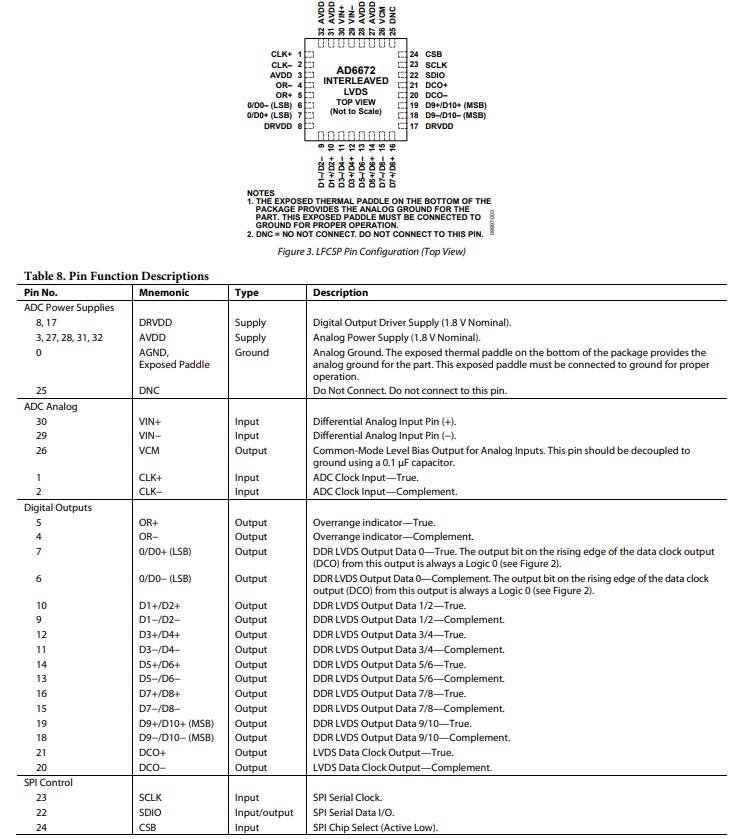

引腳配置描述

典型性能特征

概述

AD6672在采用適當的低通或帶通濾波器對ADC輸入進行濾波時,可對直流至250 MHz頻率范圍內的任意f/2頻段進行采樣,且在ADC性能方面僅有極小損失。通過一個三線制、SPI兼容的串行接口對AD6672進行編程和控制。

ADC架構

AD6672架構由前端采樣保持電路組成,其后連接流水線開關電容ADC。每個階段的量化輸出先進行合并,再得到最終的11位數字校正邏輯結果。流水線架構使第一級能夠基于新的輸入樣本運行,并讓其余各級對前一個樣本進行處理,在時鐘上升沿進行采樣。

流水線的每一級(最后一級除外)均由一個低分辨率閃存ADC、一個數模轉換器(DAC)以及一個積分誤差放大器(MDAC)組成。MDAC對DAC輸出與下一級流水線中閃存輸入的差值進行放大。每一級中都有一位冗余,用于校正閃存誤差。最后一級僅由一個閃存ADC組成。

輸入級包含一個差分采樣電路,可實現交流耦合或單端模式。輸出數據鎖存模塊會阻塞數據、校正誤差,并將數據輸出到外部緩沖器。輸出緩沖器由獨立電源供電,使數字輸出能夠與模擬內核隔離。在掉電期間,輸出緩沖器進入高阻態。

AD6672具備11位噪聲整形量化器(NSR)功能,可在奈奎斯特頻帶內保持較低的SNR。

模擬輸入注意事項

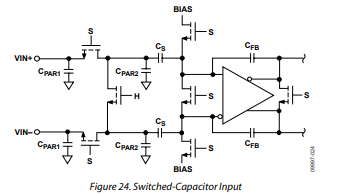

AD6672的模擬輸入采用差分開關電容電路,針對差分輸入信號處理進行了優化。

時鐘信號交替切換輸入電路,使其在采樣模式和保持模式間轉換(配置見圖24)。處于采樣模式時,信號源必須能夠在半個時鐘周期內完成對采樣電容的充電以及設置。

每個輸入端串聯一個小電阻,有助于降低驅動源輸出級所需的峰值瞬態電流。可在輸入端之間并聯一個旁路電容,為動態充電電流提供通路。這種無源網絡會在ADC輸入端形成一個低通濾波器,因此,具體數值取決于應用場景。

在中頻欠采樣應用中,應減少采樣電容。結合驅動源阻抗,旁路電容會限制輸入帶寬。更多相關信息,請參考《AN - 742應用筆記:失調與增益誤差對開關電容放大器的影響》、《AN - 827應用筆記:射頻/中頻放大器接口的電阻性方法》,以及Analog Dialogue文章《變壓器耦合前端與寬帶A/D轉換器》。

為實現最佳動態性能,需匹配驅動VIN+和VIN - 引腳的源阻抗,并使輸入差分平衡。

輸入共模

AD6672的模擬輸入內部無直流偏置。在交流耦合應用中,用戶必須從外部提供此偏置。將器件設置為VCM = 0.5 × AVDD(或0.9 V)可實現最佳性能。芯片設計中集成了片上共模電壓基準,可通過VCM引腳獲取。建議使用VCM輸出來設置輸入共模。

模擬輸入的最佳共模電壓由VCM引腳電壓(通常為0.5 × AVDD)設定。VCM引腳必須通過0.1 μF電容接地,具體內容見應用信息部分。將此去耦電容放置在靠近引腳處,可縮短電阻和電感回路,從而改善性能。

-

接收機

+關注

關注

8文章

1218瀏覽量

54230 -

中頻

+關注

關注

0文章

51瀏覽量

22313 -

ADC

+關注

關注

0文章

206瀏覽量

16845

發布評論請先 登錄

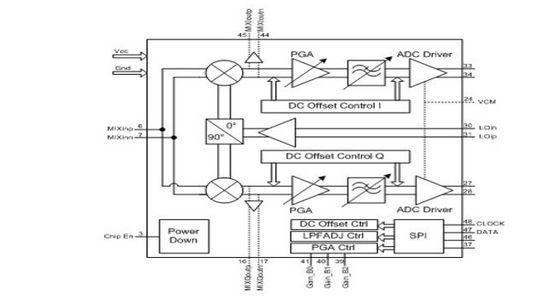

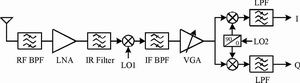

零中頻接收機設計

經典又實用的零中頻接收機的技術解決方案

HFA3783芯片在類零中頻接收機中的應用

零中頻射頻接收機技術

AD6672 中頻接收機

AD6672中頻接收機技術手冊

AD6672中頻接收機技術手冊

評論