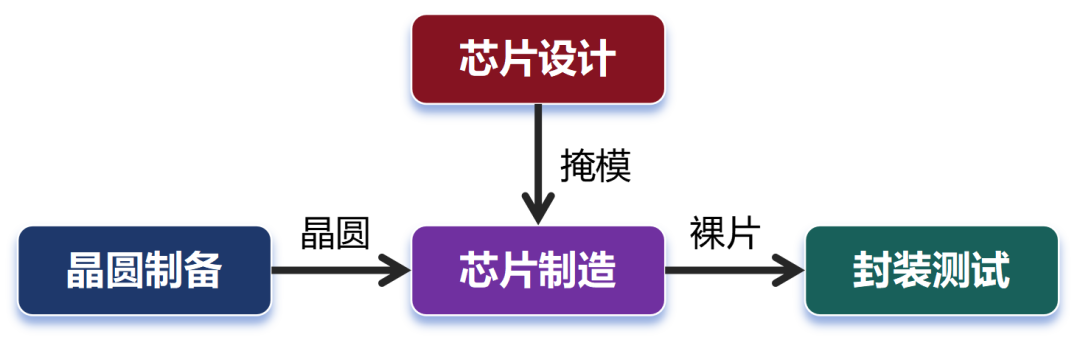

之前給大家介紹了晶圓制備和芯片制造:晶圓是如何制造出來的?從入門到放棄,芯片的詳細制造流程!從今天開始,我們聊聊芯片的封裝和測試(通常簡稱“封測”)。

這一部分,在行業里也被稱為后道(Back End)工序,一般都是由OSAT封測廠(Outsourced Semiconductor Assembly and Test,外包半導體封裝與測試)負責。

封裝的目的

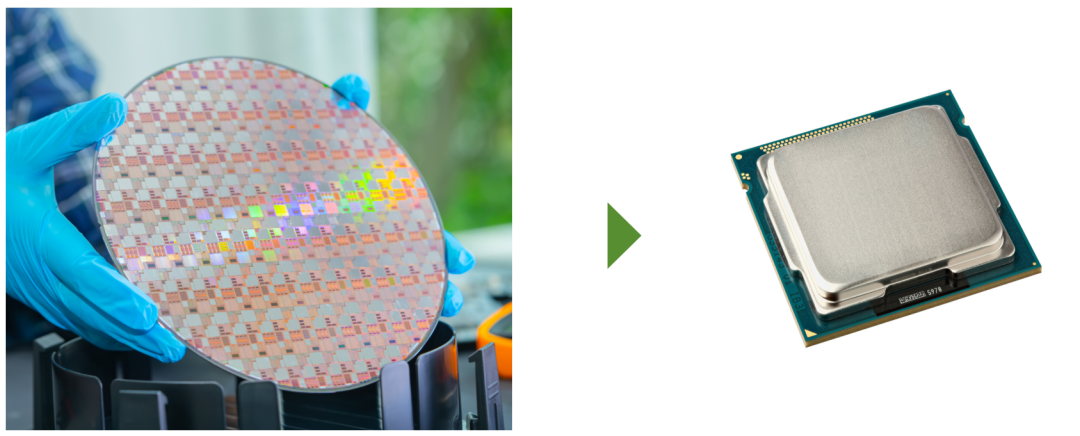

先說封裝。封裝這個詞,其實我們經常會聽到。它主要是指把晶圓上的裸芯片(晶粒)變成最終成品芯片的過程。

之所以要做封裝,主要目的有兩個。一個是對脆弱的晶粒進行保護,防止物理磕碰損傷,也防止空氣中的雜質腐蝕晶粒的電路。二是讓芯片更適應使用場景的要求。芯片有很多的應用場景。不同的場景,對芯片的外型有不同的要求。進行合適的封裝,能夠讓芯片更好地工作。

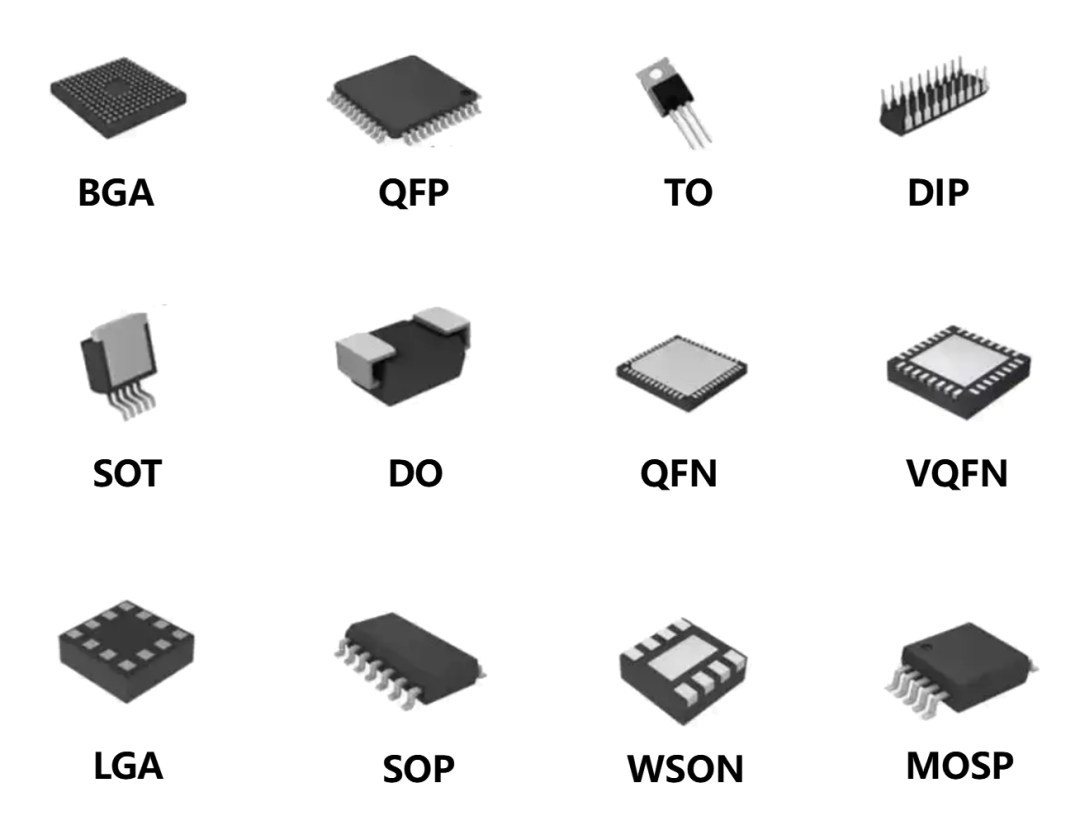

我們平時會看到很多種外型的芯片,其實就是不同的封裝類型

封裝的發展階段

封裝工藝伴隨芯片的出現而出現,迄今為止已有70多年的歷史。總的來看,封裝工藝一共經歷了五個發展階段:

接下來,我們一個個來說。

- 傳統封裝

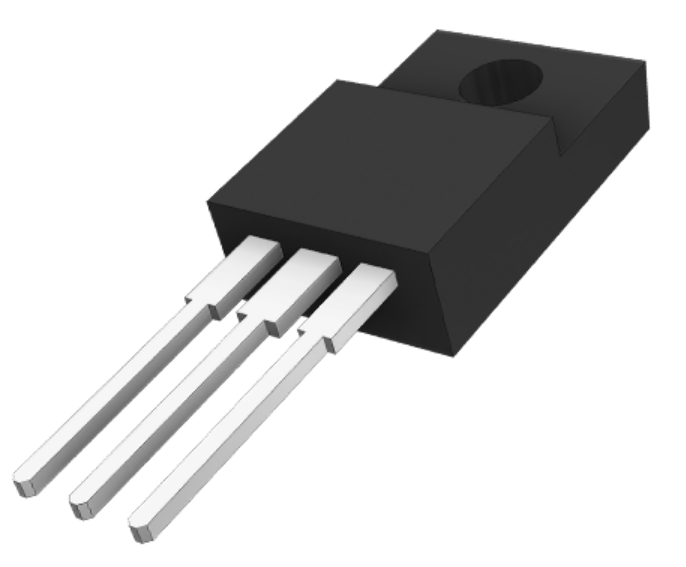

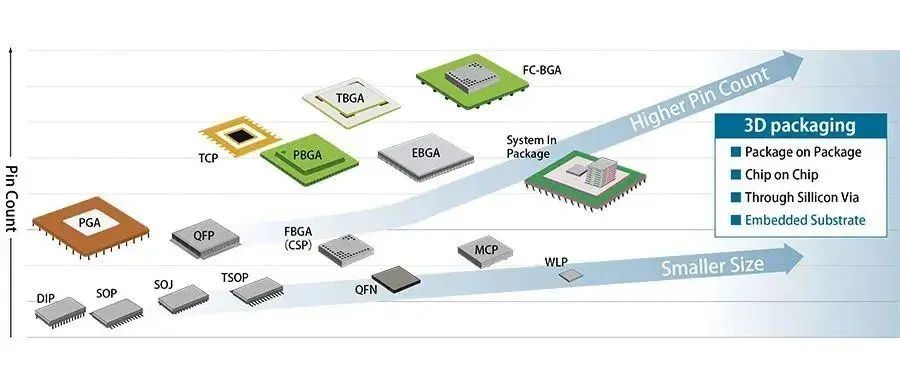

最早期的晶體管,采用的是TO(晶體管封裝)。后來,發展出了DIP(雙列直插封裝)。

我們最熟悉的三極管造型,就是TO封裝

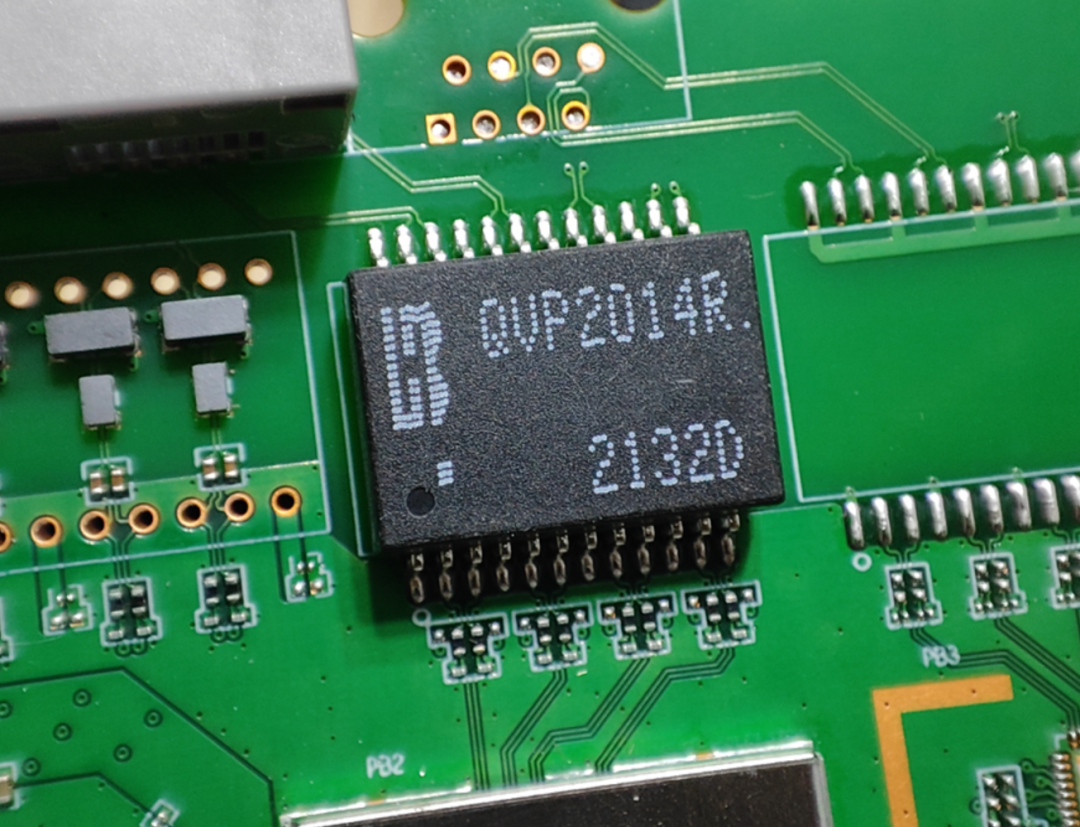

再后來,由PHILIP公司開發出了SOP(小外型封裝),并逐漸派生出SOJ(J型引腳小外形封裝)、TSOP(薄小外形封裝)、VSOP(甚小外形封裝)、SSOP(縮小型SOP)、TSSOP(薄的縮小型SOP)及SOT(小外形晶體管)、SOIC(小外形集成電路)等。

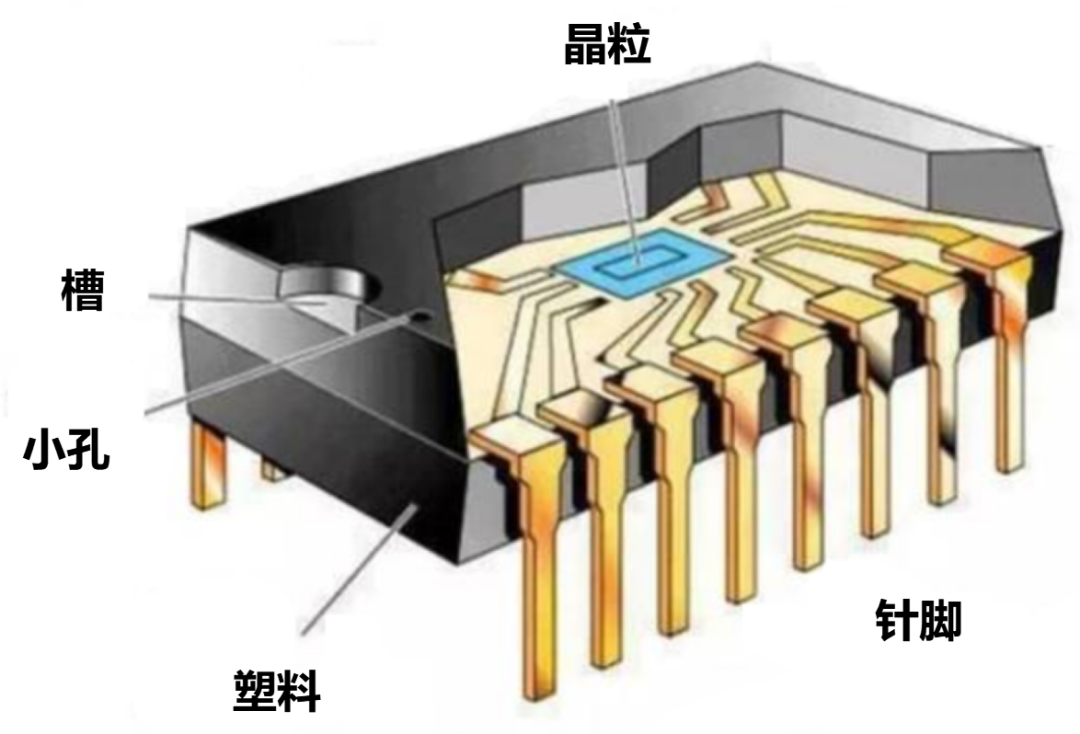

DIP內部構造

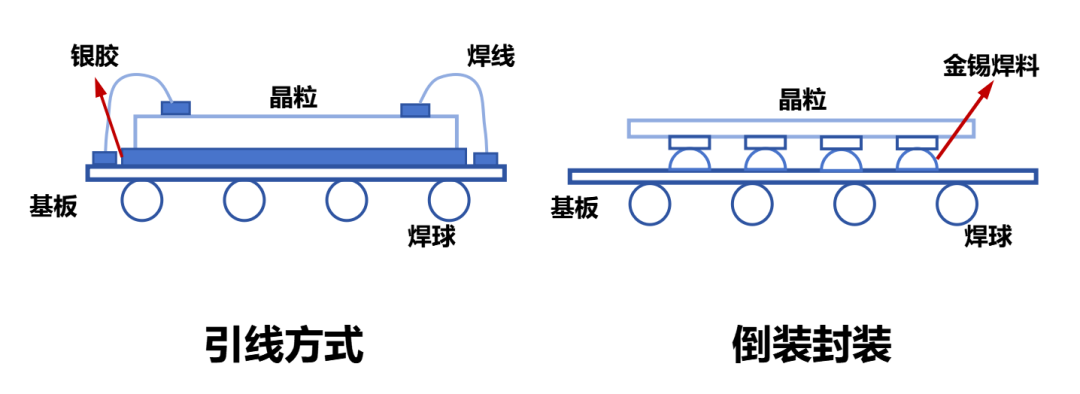

第一、第二階段(1960-1990年)的封裝,以通孔插裝類封裝(THP)以及表面貼裝類封裝(SMP)為主,屬于傳統封裝。傳統封裝,主要依靠引線將晶粒與外界建立電氣連接。

這些傳統封裝,直到現在仍比較常見。尤其是一些老的經典型號芯片,對性能和體積要求不高,仍會采用這種低成本的封裝方式。

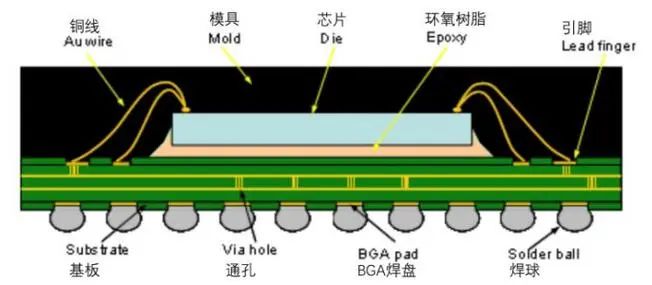

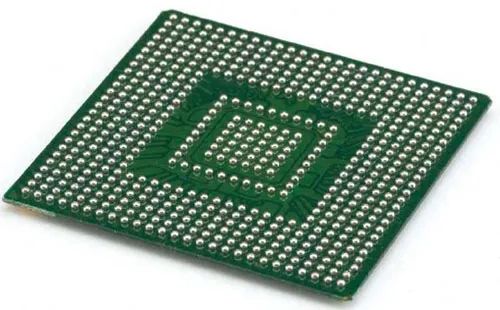

第三階段(1990-2000年),IT技術革命加速普及,芯片功能越來越復雜,需要更多的針腳。電子產品小型化,又要求芯片的體積繼續縮小。這時,BGA(球型矩陣、球柵陣列)封裝開始出現,并成為主流。BGA仍屬于傳統封裝。它的接腳位于芯片下方,數量龐大,非常適合需要大量接點的芯片。而且,相比DIP,BGA的體積更為緊湊,非常適合需要小型化設備。

BGA封裝

BGA封裝內部和BGA有些類似的,還有LGA(平面網格陣列封裝)和PGA(插針網格陣列封裝)。大家應該注意到了,我們最熟悉的CPU,就是這三種封裝。

- 先進封裝

20世紀末,芯片級封裝(CSP)、晶圓級封裝(WLP)、倒裝封裝(Flip Chip)開始慢慢崛起。傳統封裝開始向先進封裝演變。相比于BGA這樣的封裝,芯片級封裝(CSP)強調的是尺寸的更小型化(封裝面積不超過芯片面積的1.2倍)。

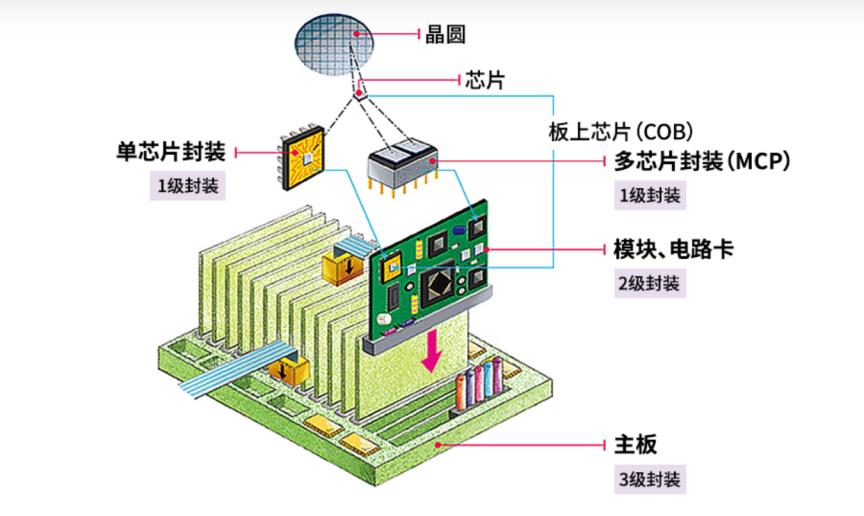

封裝的層級(來自Skhynix)

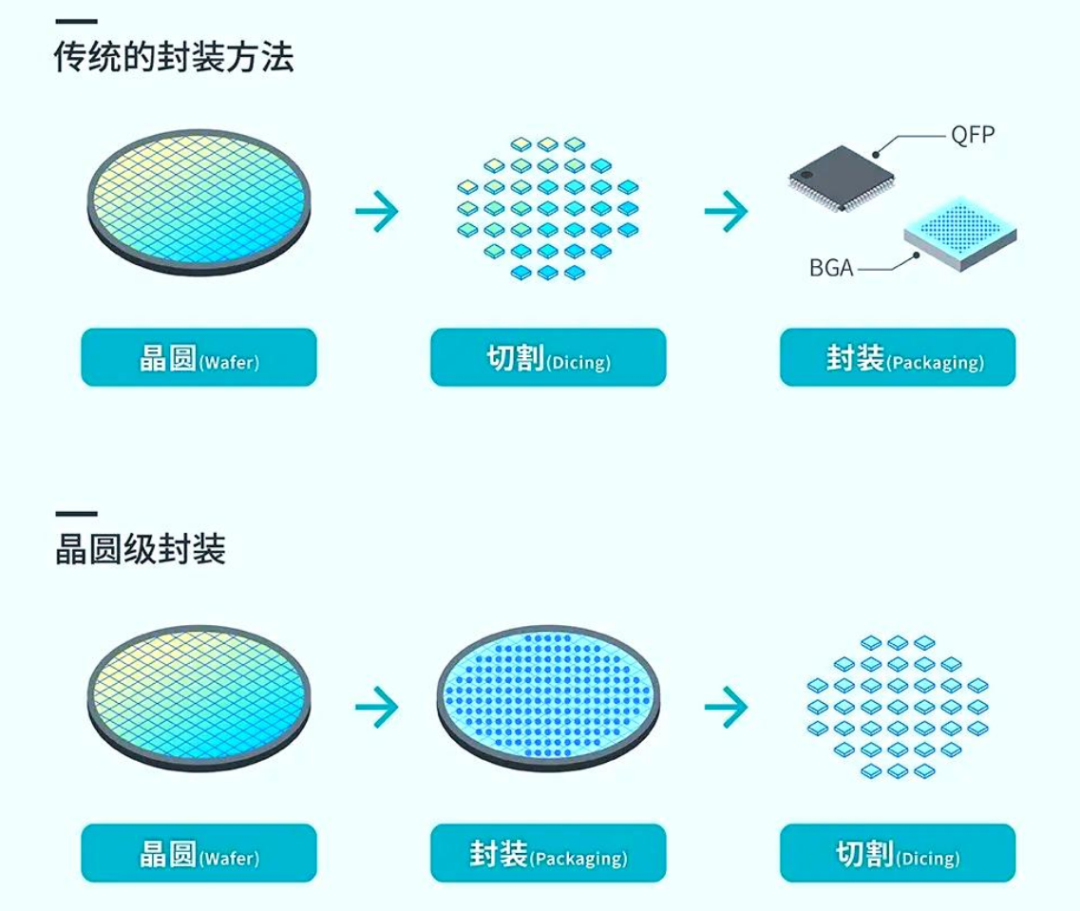

晶圓級封裝是芯片級封裝的一種,封裝的尺寸接近裸芯片大小。下期我們講具體工藝的時候,會提到封裝包括了一個切割工藝。傳統封裝,是先切割晶圓,再封裝。而晶圓級封裝,是先封裝,再切割晶圓,流程不一樣。

晶圓級封裝

倒裝封裝(Flip Chip)的發明時間很早。1960年代的時候,IBM就發明了這個技術。但是直到1990年代,這個技術才開始普及。采用倒裝封裝,就是不再用金屬線進行連接,而是把晶圓直接反過來,通過晶圓上的凸點(Bump),與基板進行電氣連接。和傳統金屬線方式相比,倒裝封裝的I/O(輸入/輸出)通道數更多,互連長度縮短,電性能更好。另外,在散熱和封裝尺寸方面,倒裝封裝也有優勢。

先進封裝的出現,迎合了當時時代發展的需求。它采用先進的設計和工藝,對芯片進行封裝級重構,帶來了更多的引腳數量、更小的體積、更高的系統集成度,能夠大幅提升系統的性能。進入21世紀后,隨著移動通信和互聯網革命的進一步爆發,促進芯片封裝進一步朝著高性能、小型化、低成本、高可靠性等方向發展。先進封裝技術開始進入高速發展的階段。這一時期,芯片內部布局開始從二維向三維空間發展(將多個晶粒塞在一起),陸續出現了2.5D/3D封裝、硅通孔(TSV)、重布線層(RDL)、扇入(Fan-In)/扇出(Fan-Out)型晶圓級封裝、系統級封裝(SiP)等先進技術。

當芯片制程發展逐漸觸及摩爾定律的底線時,這些先進的封裝技術,就成了延續摩爾定律的“救命稻草”。

先進封裝的關鍵技術

- 2.5D/3D封裝

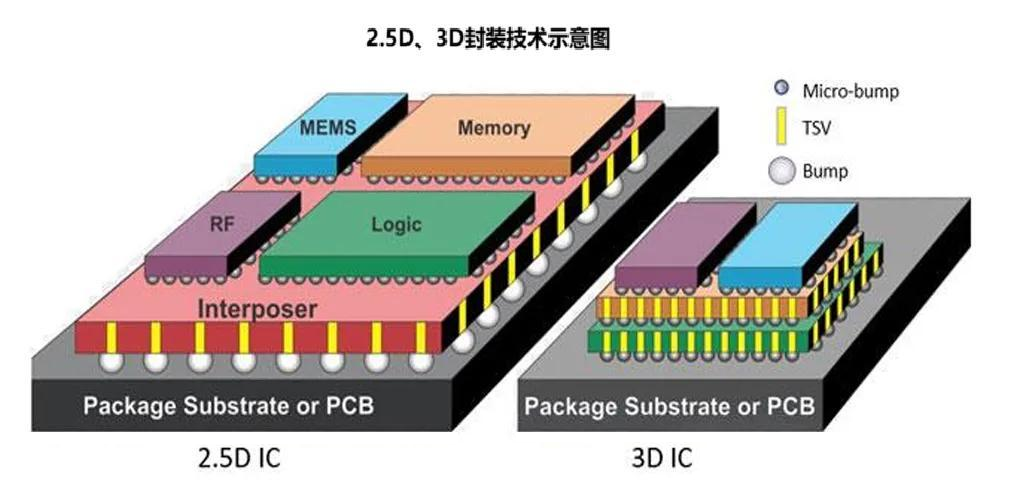

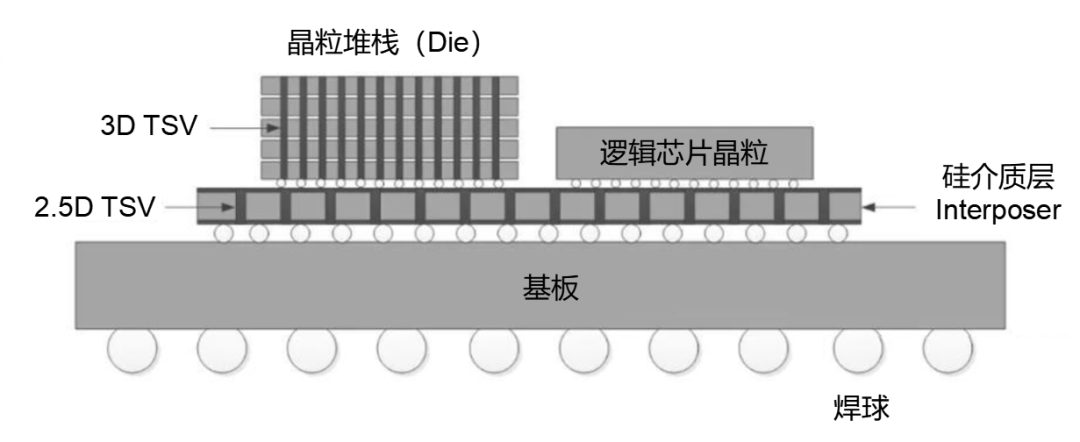

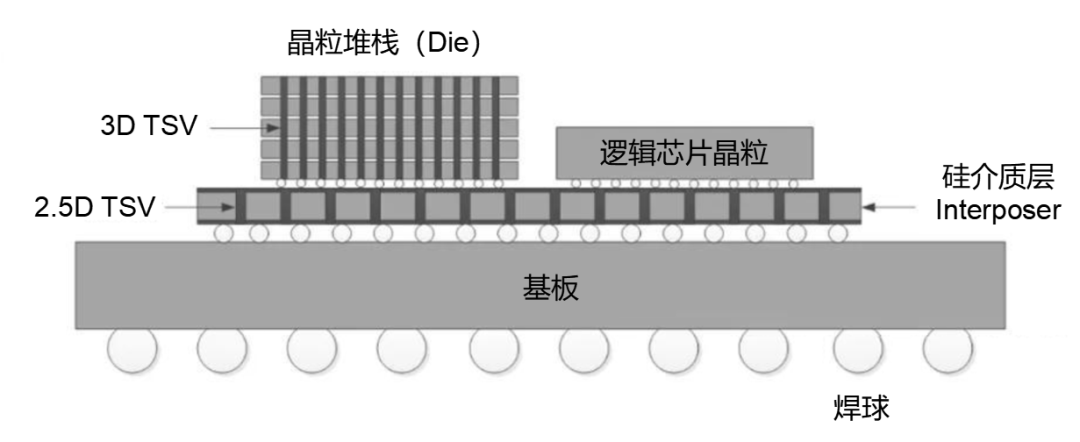

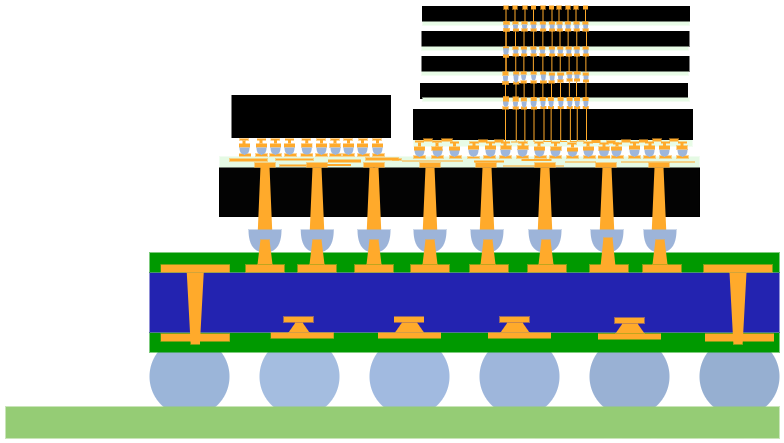

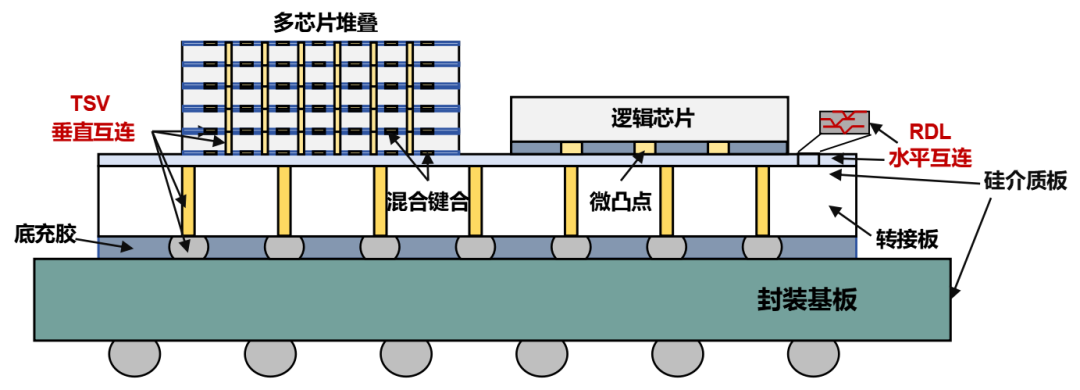

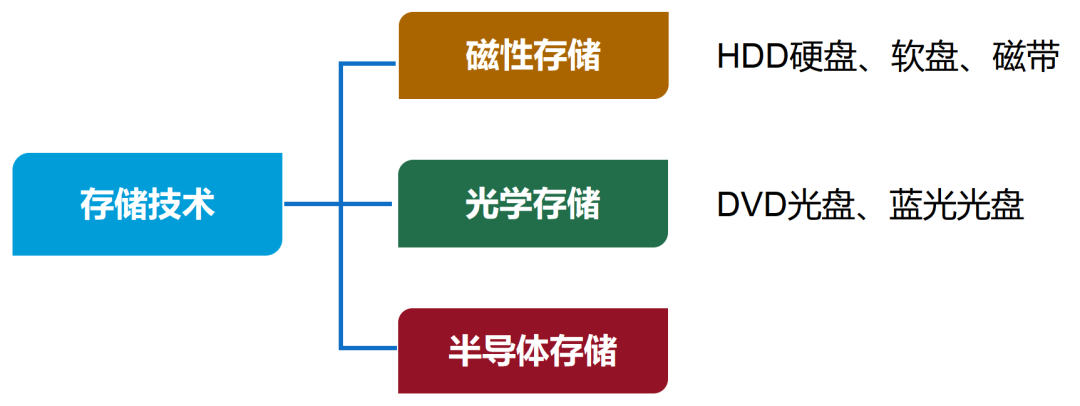

2.5D和3D封裝,都是對芯片進行堆疊封裝。2.5D封裝技術,可以將兩種或更多類型的芯片放入單個封裝,同時讓信號橫向傳送,這樣可以提升封裝的尺寸和性能。最廣泛使用的2.5D封裝方法,是通過硅中介層(Interposer)將內存和邏輯芯片(GPU或CPU等)放入單個封裝。2.5D封裝需要用到硅通孔(TSV)、重布線層(RDL)、微型凸塊等核心技術。

3D封裝是在同一個封裝體內,于垂直方向疊放兩個以上芯片的封裝技術。

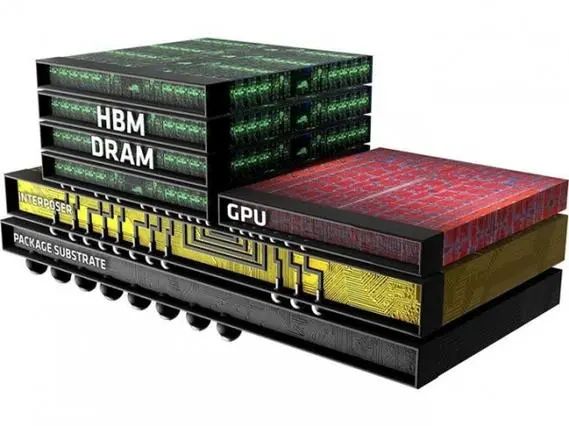

2.5D和3D封裝的主要區別在于:2.5D封裝,是在Interposer上進行布線和打孔。而3D封裝,是直接在芯片上打孔和布線,連接上下層芯片堆疊。相對來說,3D封裝的要求更高,難度更大。2.5D和3D封裝起源于FLASH存儲器(NOR/NAND)及SDRAM的需求。大名鼎鼎的HBM(High Bandwidth Memory,高帶寬存儲器),就是2.5D和3D封裝的典型應用。將HBM和GPU進行整合,能夠進一步發揮GPU的性能。

HBM,對于GPU很重要,對AI也很重要

HBM通過硅通孔等先進封裝工藝,垂直堆疊多個DRAM,并在Interposer上與GPU封裝在一起。HBM內部的DRAM堆疊,屬于3D封裝。而HBM與GPU合封于Interposer上,屬于2.5D封裝。現在業界很多廠商推出的新技術,例如CoWoS、HBM、Co-EMIB、HMC、Wide-IO、Foveros、SoIC、X-Cube等,都是由2.5D和3D封裝演變而來的。

- 系統級封裝(SiP)

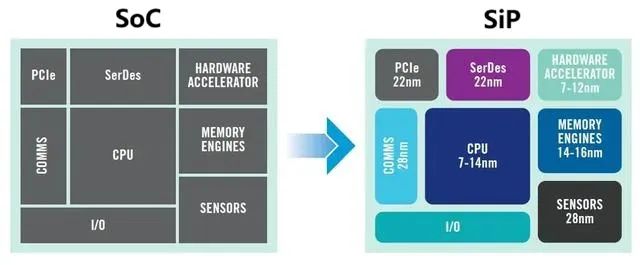

大家應該都聽說過SoC(System on Chip,系統級芯片)。我們手機里面那個主芯片,就是SoC芯片。SoC,簡單來說,是將多個原本具有不同功能的芯片整合設計到一顆單一的芯片中。這樣可以最大程度地縮小體積,實現高度集成。但是,SoC的設計難度很大,同時還需要獲得其他廠商的IP(intellectual property)授權,增加了成本。

SiP(System In Packet,系統級封裝),和SoC就不一樣。SiP將多個芯片直接拿來用,以并排或疊加的方式(2.5D/3D封裝),封裝在一個單一的封裝體內。盡管SiP沒有SoC那樣高的集成度,但也夠用,也能減少尺寸,最主要是更靈活、更低成本(避免了繁瑣的IP授權步驟)。業界常說的Chiplet(小芯粒、小芯片),其實就是SiP的思路,將一類滿足特定功能的裸片(die),通過die-to-die的內部互聯技術,互聯形成大芯片。

- 硅通孔(TSV)

前面反復提到了硅通孔(through silicon via,TSV,也叫硅穿孔)。所謂硅通孔,其實原理也挺簡單,就是在硅介質層上刻蝕垂直通孔,并填充金屬,實現上下層的垂直連接,也就實現了電氣連接。

由于垂直互連線的距離最短、強度較高,所以,硅通孔可以更容易實現小型化、高密度、高性能等優點,非常適合疊加封裝(3D封裝)。硅通孔的具體工藝,我們下期再做介紹。

- 重布線層(RDL)

RDL是在芯片表面沉積金屬層和相應的介電層,形成金屬導線,并將IO端口重新設計到新的、更寬敞的區域,形成表面陣列布局,實現芯片與基板之間的連接。

RDL技術

說白了,就是在硅介質層里面重新連線,確保上下兩層的電氣連通。在3D封裝中,如果上下堆疊的是不同類型的芯片(接口不對齊),則需要通過RDL重布線層,將上下層芯片的IO進行對準。

如果說TSV實現了Z平面的延伸,那么,重布線層(RDL)技術則實現了X-Y平面進行延伸。業界的很多技術,例如WLCSP、FOWLP、INFO、FOPLP、EMIB等,都是基于RDL技術。

- 扇入(Fan-In)/扇出(Fan-Out)型晶圓級封裝

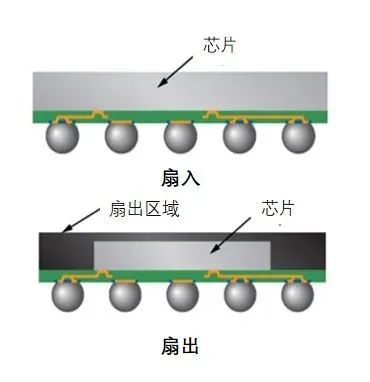

WLP(晶圓級封裝)可分為扇入型晶圓級封裝(Fan-In WLP)和扇出型晶圓級封裝(Fan-Out WLP)兩大類。扇入型直接在晶圓上進行封裝,封裝完成后進行切割,布線均在芯片尺寸內完成,封裝大小和芯片尺寸相同。

扇出型則基于晶圓重構技術,將切割后的各芯片重新布置到人工載板上。然后,進行晶圓級封裝,最后再切割。布線可在芯片內和芯片外,得到的封裝面積一般大于芯片面積,但可提供的IO數量增加。目前量產最多的,是扇出型產品。

參考文獻:1、《芯片制造全工藝流程》,半導體封裝工程師之家;2、《一文讀懂芯片生產流程》,Eleanor羊毛衫;3.、《不得不看的芯片制造全工藝流程》,射頻學堂;4、《什么是先進封裝?和傳統封裝有什么區別?如何分類?》,失效分析工程師趙工;5、《一文了解先進封裝之倒裝芯片(FlipChip)技術》,圓圓的圓,半導體全解;6、《一文了解硅通孔(TSV)及玻璃通孔(TGV)技術》,圓圓的圓,半導體全解;7、《先進封裝發展充要條件已具,關鍵材料國產替代在即》,國金證券;8、《Chiplet先進封裝大放異彩》,民生證券;9、維基百科、百度百科、各廠商官網。

文章來源于鮮棗課堂,作者小棗君

-

芯片測試

+關注

關注

6文章

146瀏覽量

20664 -

芯片封裝

+關注

關注

11文章

576瀏覽量

31373 -

封測

+關注

關注

4文章

363瀏覽量

35471

發布評論請先 登錄

寫給小白們的FPGA入門設計實驗

寫給小白們的FPGA入門設計實驗

PCB封裝入門的必備知識

寫給小白的ChatGPT和AI原理

收藏 | 寫給小白的芯片半導體科普!

寫給小白的芯片半導體科普

寫給小白的AI入門科普

寫給小白的大模型入門科普

寫給小白的芯片封裝入門科普

寫給小白的芯片封裝入門科普

評論