背景介紹

在嵌入式系統中,UART 串口通常用于調試和通訊。通常情況下,調試串口對波特率的大小沒有特別要求,一般配置是 115200 8N1。UART 串口除了調試功能外,有時候在設計中也會充當數據通訊接口和其它單板或模組進行互連通訊。當 UART 作為數據通訊接口時,對傳輸的帶寬就會有較高要求,往往原先的波特率 115200 就不能適應這樣的需求了。接下來將介紹 Altera A10 SoC HPS UART 作為數據通訊接口需要注意的地方。

HPS UART 波特率配置

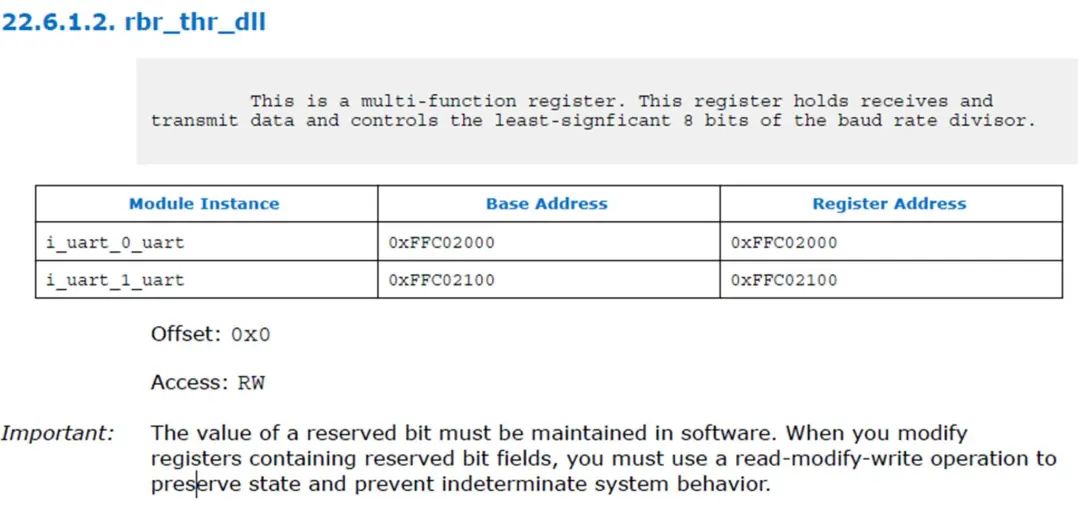

1. 配置波特率的寄存器 rbr_thr_dll

Altera A10 SoC HPS 提供了兩個 UART 接口:UART 0 和 UART 1。分配的固定基地址如下圖 (圖1) 所示:

圖1 固定基地址

根據數據手冊的描述說明,分頻值 = 串口時鐘 ÷ (16* 波特率)。由于分頻值的結果很可能是個小數,需要取最接近的一個整數,寫進分頻值的寄存器的低 8 位 DLL 和高 8 位 DLH,這樣實際的波特率就和預期的波特率存在些差異,見下圖 (圖2):

圖2 DLL 寄存器

2. 波特率誤差控制

這里需要注意的是:實際中,當 SoC FPGA 單板的 UART 串口作為數據傳輸接口與其它單板或模組通訊時,兩者 UART 串口的波特率大小配置要盡可能相等或接近,波特率的相差控制在 2% 以內。若相差過大就有可能出現 UART 串口所傳輸的數據不能被對端 UART 串口正確識別,從而可能導致數據傳輸失敗。

實際應用案例

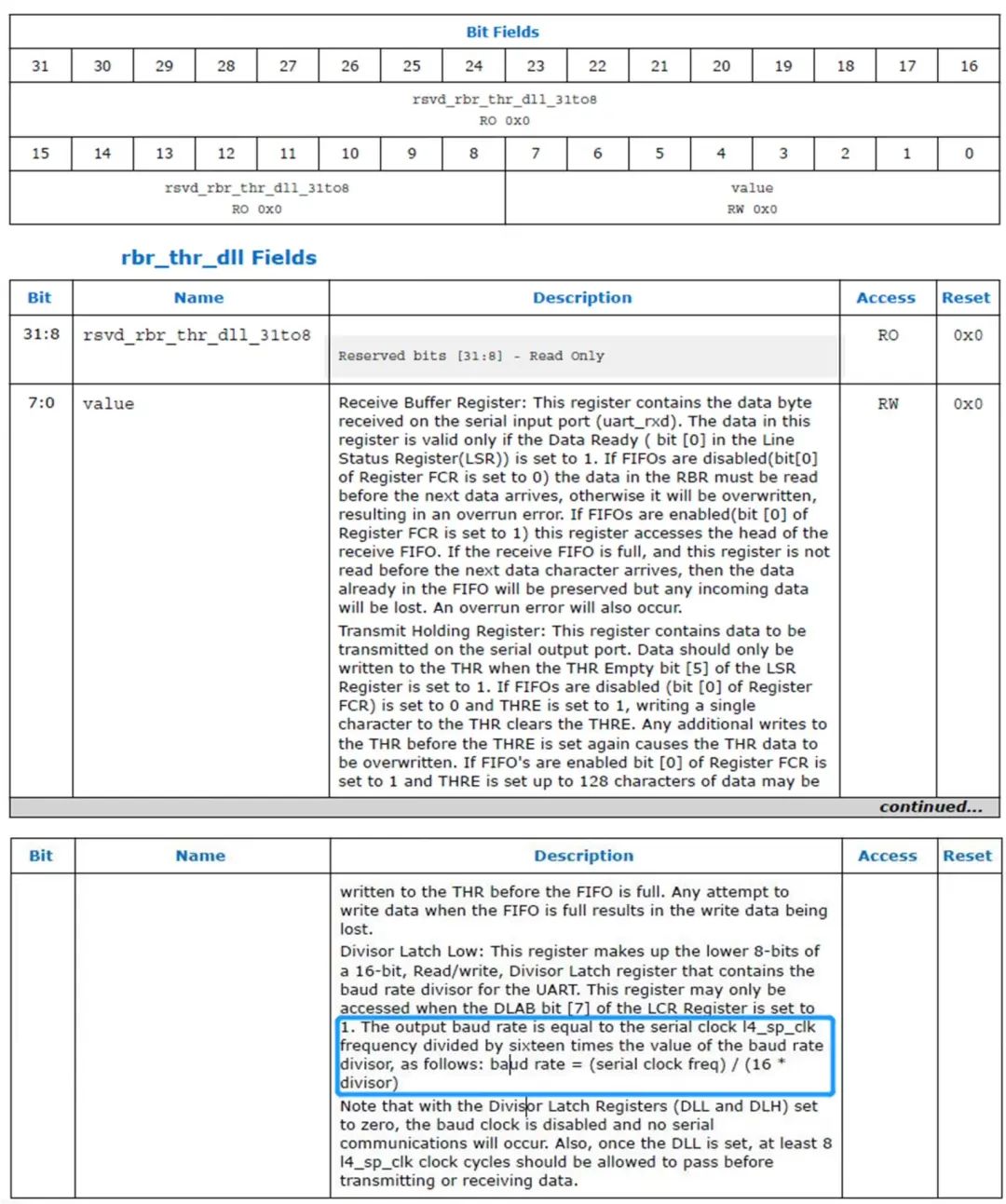

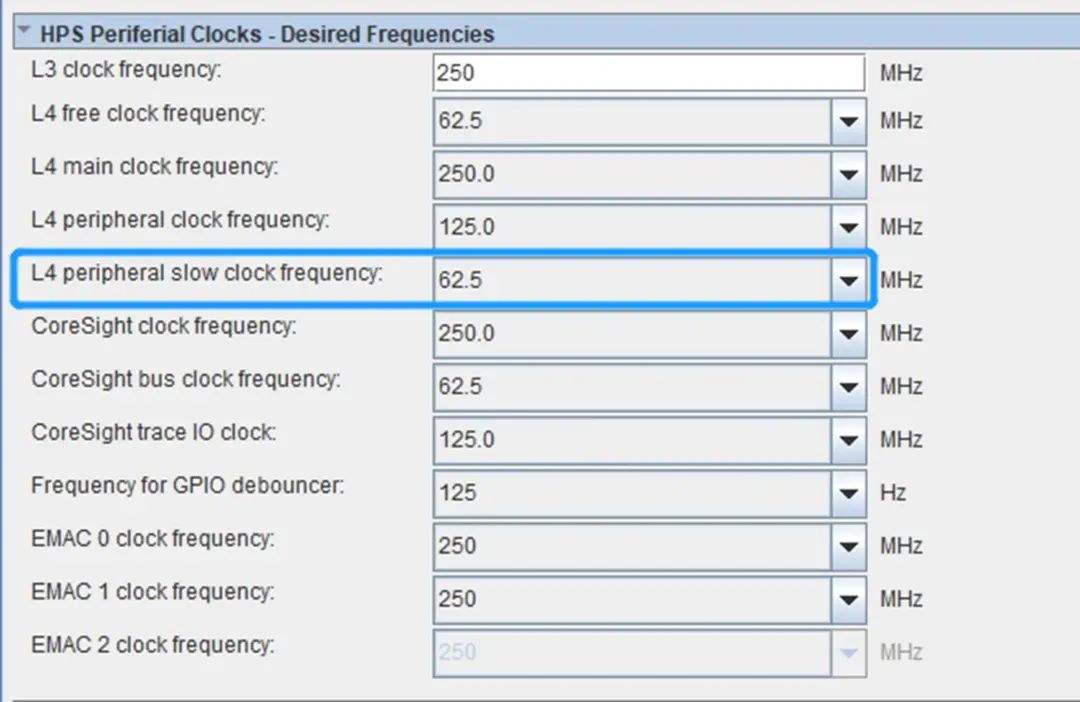

關于這種應用情況,接下來通過一個客戶實際的例子為大家進行解釋說明。客戶使用 Altera A10 SOC FPGA,HPS 通過 UART 0 外接一塊模組進行數據傳輸,初始配置如下圖 (圖3) 所示:

圖3 初始配置

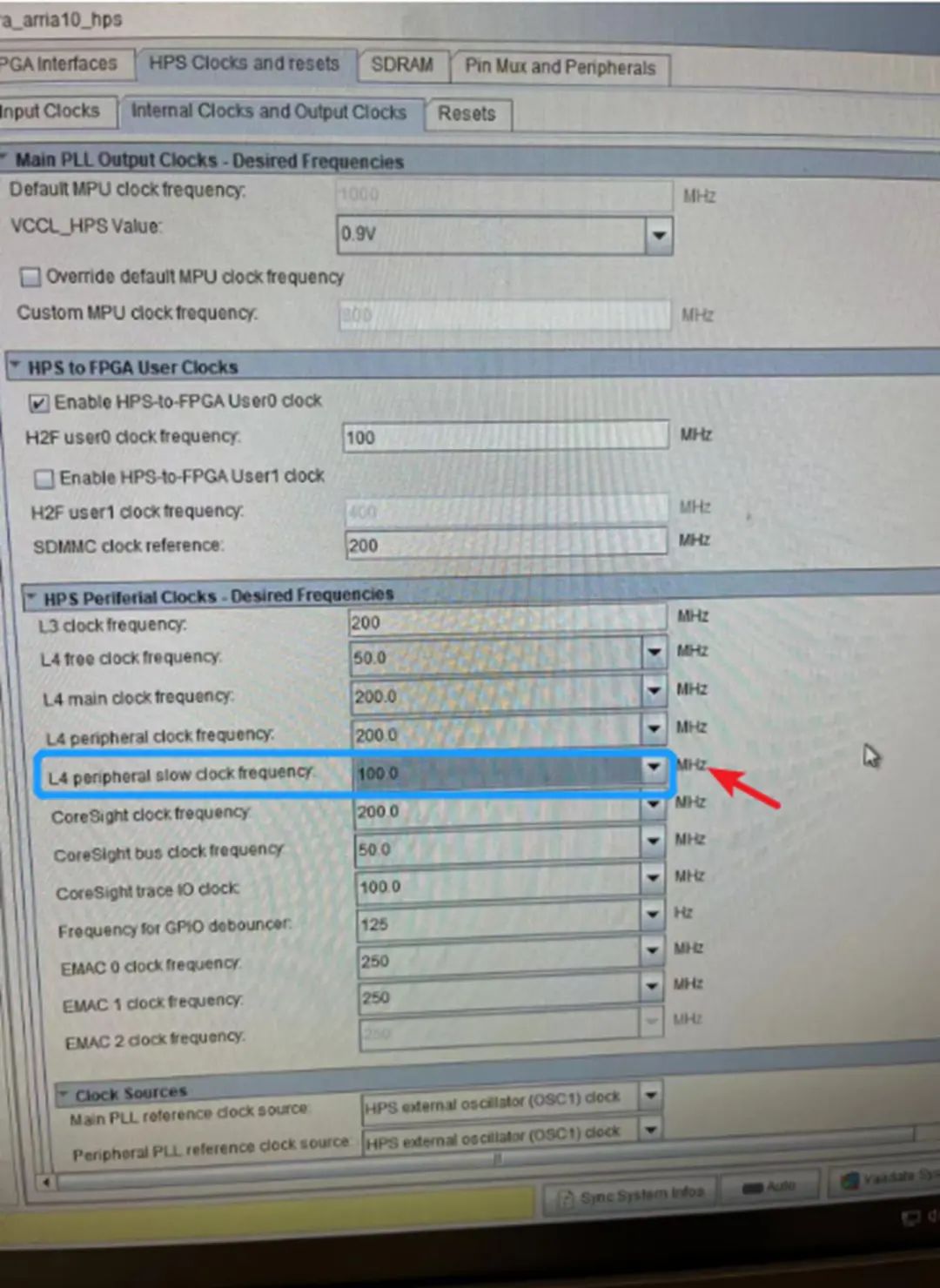

從上圖可以看出,Qsys HPS 時鐘與復位 config,客戶配置的 l4_sp clock 為 100MHz,配置的分頻值為 3,對應的波特率為 100 ÷ (16*3) = 2.083M。但示波器測試是 2.084M,見下圖 (圖4) 藍框標記:

圖4 示波器測試值

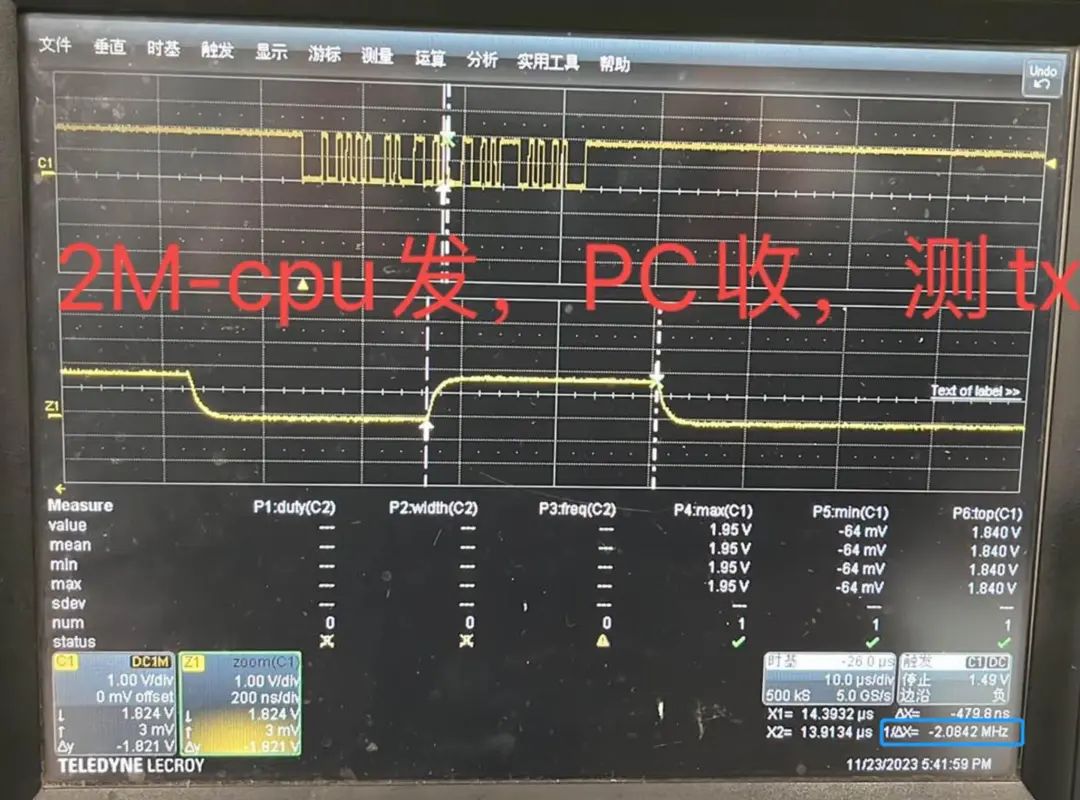

然而,HPS UART 串口外接模組的串口波特率為 2.00M,相差達到 4%,導致兩塊單板通訊失敗。經過調整適配配置參數最終才找到合適的時鐘及分頻值,如下圖 (圖5) 所示:

圖5 合適的時鐘及分頻值

將客戶配置的 l4_sp clock 由 100MHz 調整為 62.5MHz,配置的分頻值調整為 2,對應的波特率為 62.5 ÷ (16*2) = 1.95M,兩者波特率相差大約 2%,最終兩塊單板的 UART 串口通訊恢復正常,數據帶寬大約是 0.19MB/S。

總結

本文介紹了 Altera A10 SoC HPS UART 作為數據通訊接口的應用,重點講解了波特率配置、分頻值計算及實際應用中的調試技巧。通過合理配置時鐘和分頻值,開發者可以實現高速、穩定的 UART 數據傳輸。

-

接口

+關注

關注

33文章

8949瀏覽量

153221 -

Altera

+關注

關注

37文章

800瀏覽量

155500 -

串口

+關注

關注

14文章

1586瀏覽量

78686 -

uart

+關注

關注

22文章

1268瀏覽量

103294 -

數據通訊

+關注

關注

0文章

46瀏覽量

12152

原文標題:Altera A10 SoC HPS UART 作為數據通訊接口應用的配置與調試

文章出處:【微信號:駿龍電子,微信公眾號:駿龍電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

《電子發燒友電子設計周報》聚焦硬科技領域核心價值 第9期:2025.04.21--2025.04.25

遠程醫療的數據通訊分析

基于CANopen協議的車載平臺數據通訊系統

基于EZ-USB FX單片機的無線式數據通訊接口卡的設計

基于USB接口的超聲檢測數據通訊

PC104總線與DSP數據通信接口設計

LED顯示屏高速數據通訊接口設計

應該了解300 CPU MPI全局數據通訊組態的方法

Altera A10 SoC HPS UART作為數據通訊接口應用的配置與調試

Altera A10 SoC HPS UART作為數據通訊接口應用的配置與調試

評論