概述

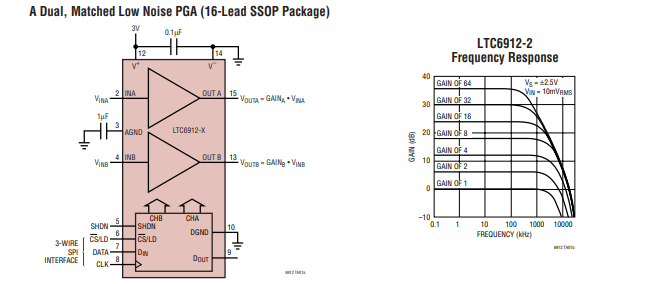

LTC6912 是雙通道、低噪聲、數字可編程增益放大器 (PGA) 系列,易于使用,占用的 PC 板空間非常小。兩個通道的增益均可使用 3 線 SPI 接口獨立編程,以選擇 0、1、2、5、10、20、50 和 100V/V (LTC6912-1) 的電壓增益;以及 0、1、2、4、8、16、32 和 64V/V (LTC6912-2)。所有增益都是反相的。

LTC6912 系列由 2 個具有軌到軌輸出的匹配放大器組成。當使用運行時,它們還將處理軌到軌輸入信號。在 AGND 引腳內部生成的半電源基準支持單電源應用。LTC6912-X 系列采用 2.7V 至 10.5V 的單電源或分離電源供電,采用微型 SSOP 和 DFN-12 封裝。

數據表:*附件:LTC6912雙通道可編程增益放大器,具有串行數字接口技術手冊.pdf

應用

- 數據采集系統

- 動態增益變化

- 自動測距電路

- 自動增益控制

特性

- 2 個通道,具有獨立的增益控制

- LTC6912-1:(0、1、2、5、10、20、50 和 100V/V)

- LTC6912-2:(0、1、2、4、8、16、32 和 64V/V)

- 失調電壓 = 2mV (最大值) (–40°C 至 85°C)

- 通道間增益匹配:0.1dB (最大值)

- 3 線 SPI^TM^ 接口

- 高增益時擴展增益帶寬

- 可提供有線 OR 輸出(2:1 模擬多路復用器功能)

- 低功耗硬件關斷(僅限 GN-16,2.7V 時最大 2μA)

- 軌到軌輸入范圍

- 軌到軌輸出擺幅

- 單電源或雙電源:2.7V 至 10.5V 總計

- 輸入噪聲:12.6nV/√Hz

- 總系統動態范圍達 115dB

- 16 引腳 GN (SSOP) 或 12 引腳 DFN 封裝選項

典型應用

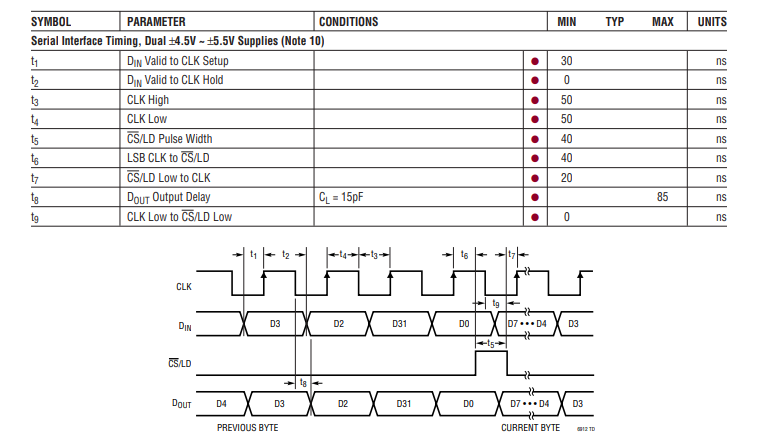

串行接口規格

注釋

- 絕對最大額定值是指超過這些值可能會損害器件使用壽命的數值。

- LTC6912 - 1C和LTC6912 - 1L在 - 40°C至85°C的工作溫度范圍內可保證功能正常。LTC6912 - 1H在 - 40°C至125°C的工作溫度范圍內可保證功能正常。

- LTC6912 - 1C的規格性能是在0°C至70°C下測量確定的,LTC6912 - 1L按預期或要求應在 - 40°C至85°C達到指定性能,但未在此溫度范圍內進行測試或鑒定;LTC6912 - 1H在 - 40°C至85°C范圍內可保證達到指定性能,LTC6912 - 1H在 - 40°C至125°C范圍內保證達到指定性能。

- 輸出電壓擺幅是指輸出與相應電源軌之間的差值。

- 不建議在高于150°C(對于GN封裝)和125°C(對于DFN封裝)的溫度下進行輸出短路操作。

- 增益不能通過輸出電壓在電源電壓約30% - 70%范圍內擺動的大信號直流測試來測量。

- 通道間隔離度的測量方法是:向一個通道施加200kHz輸入信號,使其輸出產生1V有效值的變化,測量另一個通道相對于AGND的輸出電壓有效值。隔離度計算公式為:隔離度 = 20×log_{10}(frac{V_{OUTB}}{V_{OUTA}}) (單位:dB)。高通道間隔離度很大程度上取決于正確的電路布局。更多信息請參見應用信息部分。

- 相對于INA或INB輸入的失調電壓是(1 + 1/增益)乘以內部OP放大器的失調電壓,其中增益為標稱增益值。典型的失調電壓值僅適用于25°C。更多信息請參見應用信息部分。

- 在給定增益設置下,輸入電阻的部件間差異約為±30% 。

- 通過設計保證,無需測試。

- 狀態13、14和15(二進制110xx)未使用。將通道編程為這些狀態之一,會使該通道進入低功耗關閉狀態。需要注意的是,將通道編程為狀態15(二進制11111)會導致該通道消耗高達20mA的電源電流,不建議這樣做。

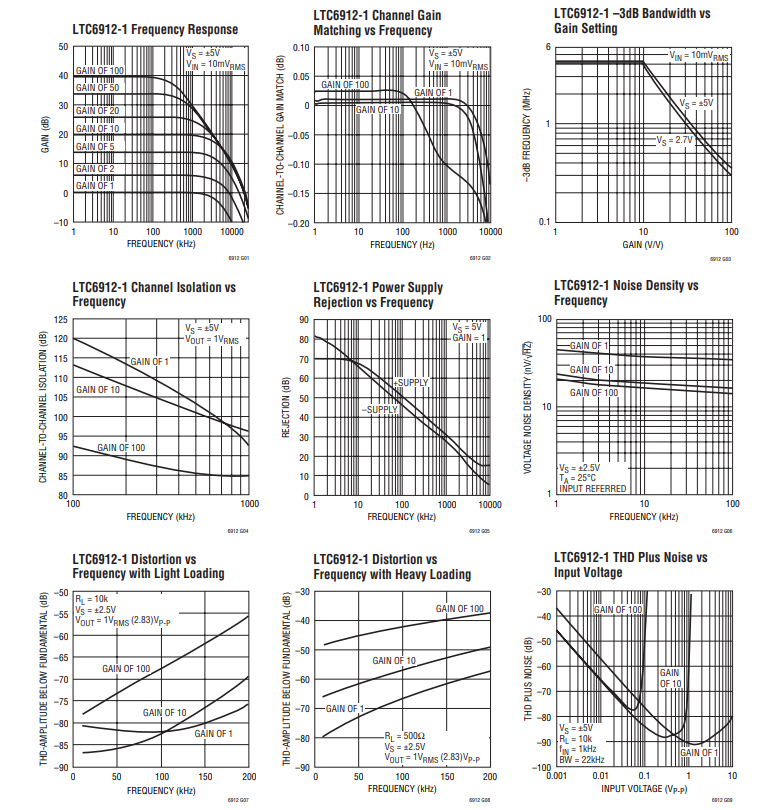

典型性能特征

應用信息

功能描述

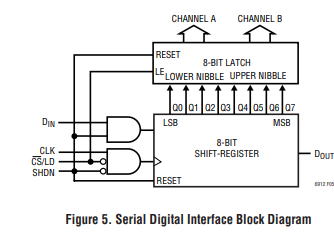

LTC6912 - X是一款小尺寸、寬帶、反相雙通道放大器,其電壓增益可獨立編程。每個通道都可通過三線串行數字接口選擇八種電壓增益,該接口兼容TTL或CMOS邏輯電平(見圖5)。表1和表2分別列出了LTC6912 - 1和LTC6912 - 2的標稱增益。在放大器內部,通過切換與閉環運算放大器電路匹配陣列中的電阻來實現增益控制(見圖1)。各獨立放大器的帶寬在“典型性能特征”部分的增益設置測量頻率響應中顯示。

三線SPI接口說明

每個放大器的增益控制可通過三線SPI接口獨立編程(見圖5)。LTC6912三線串行接口的邏輯電平兼容TTL/CMOS。當**overline{CS/LD}為低電平時,串行數據D_{IN}**在時鐘上升沿移入8位移位寄存器,最高有效位(MSB)先傳輸。**D_{OUT}**上的串行數據在時鐘下降沿移位輸出。**overline{CS/LD}上升沿會鎖存移位寄存器的內容,加載到8位D鎖存器中,并在芯片內部禁用時鐘。D鎖存器的高四位(4個最高有效位)配置B通道放大器的增益,低四位(4個最低有效位)配置A通道放大器的增益。表1和表2詳細列出了相應的標稱增益。在將overline{CS/LD}**拉低之前,務必確保CLK為低電平,以避免向8位移位寄存器輸入額外的時鐘脈沖(見圖5)。

**D_{OUT}在所有狀態下均有效,因此D_{OUT}**不能與其他SPI輸出“線或”。

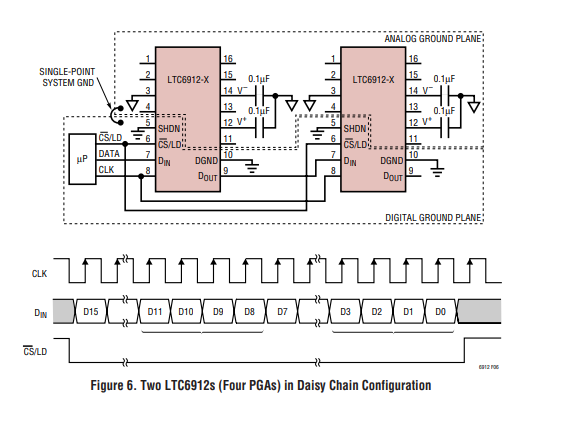

LTC6912可與其他LTC6912或其他具有串行接口的器件進行SPI級聯,方法是將D_{OUT}連接到下一個芯片的D_{IN},同時CLK和**overline{CS/LD}對菊花鏈中的所有芯片保持公共連接。串行數據在overline{CS/LD}**信號拉高時同步時鐘到所有芯片,從而同時更新所有芯片。圖6展示了兩個LTC6912進行SPI菊花鏈連接的示例。

配置

建議在數據傳輸間隙,串行接口信號保持空閑狀態,以盡量減少數字噪聲耦合到模擬路徑中。

上電復位

初次通電時,上電復位狀態下兩個放大器均處于低功耗軟件關斷狀態(狀態 = 8)(見表1和表2 )。在此狀態下,兩個模擬放大器均被禁用,其輸入和輸出均斷開。為便于在使用該器件的應用中進行應用,其具有一個2:1模擬多路復用器,通過它放大器的輸出可以進行線或連接,并且LTC6912可以交替選擇通道A和通道B。如果輸出進行線或連接,必須注意確保軟件關斷狀態(狀態 = 8)始終在兩個通道中的一個通道上被編程。

時序限制

CMOS增益控制邏輯的建立時間通常為幾納秒,比模擬信號路徑的速度更快。當放大器的增益發生變化時,限制時序的因素是模擬部分。與任何可編程增益放大器一樣,每次增益變化都會導致放大器輸出產生瞬變,因為放大器的輸出會以有限速度向不同縮放版本的輸入信號移動。LTC6912的模擬路徑會以特征時間常數或時間尺度tau 穩定下來,該時間尺度是一階帶限響應的標準值:

[ tau = 0.35/f_{-3dB} ]

詳見“典型性能特征”部分的“ - 3dB帶寬與增益設置”圖表。

-

放大器

+關注

關注

145文章

14103瀏覽量

216268 -

pga

+關注

關注

1文章

107瀏覽量

41882 -

增益放大器

+關注

關注

2文章

152瀏覽量

29476

發布評論請先 登錄

LTC6912雙通道可編程增益放大器,具有串行數字接口技術手冊

LTC6912雙通道可編程增益放大器,具有串行數字接口技術手冊

評論