文章來源:老虎說芯

原文作者:老虎說芯

本文從多個角度分析了在晶圓襯底上生長外延層的必要性。

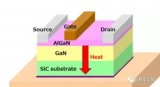

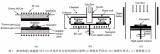

硅片襯底上再做一層硅原子外延,這樣做有什么好處呢?在CMOS硅工藝中,晶圓襯底上進行外延生長(EPI,epitaxial)是一項非常關(guān)鍵的工藝步驟。

1.提高晶體質(zhì)量

初始襯底缺陷和雜質(zhì):晶圓襯底在制造過程中可能會有一定的缺陷和雜質(zhì)。外延層的生長可以在襯底上生成一個高質(zhì)量、缺陷和雜質(zhì)濃度低的單晶硅層,這對于后續(xù)的器件制造非常重要。

均勻的晶體結(jié)構(gòu):外延生長可以保證一個更均勻的晶體結(jié)構(gòu),減少襯底材料中的晶界和缺陷的影響,從而提高整個晶圓的晶體質(zhì)量。

2.改善電氣性能

優(yōu)化器件特性:通過在襯底上生長外延層,可以精確控制硅的摻雜濃度和類型,優(yōu)化器件的電氣性能。例如,外延層的摻雜可以精確調(diào)節(jié)MOSFET的閾值電壓和其他電學(xué)參數(shù)。

減少漏電流:高質(zhì)量的外延層具有較低的缺陷密度,這有助于減少器件中的漏電流,從而提高器件的性能和可靠性。

3.支持先進工藝節(jié)點

縮小特征尺寸:在更小的工藝節(jié)點(例如7nm、5nm)中,器件特征尺寸不斷縮小,要求更加精細(xì)和高質(zhì)量的材料。外延生長技術(shù)能夠滿足這些要求,支持高性能和高密度的集成電路制造。

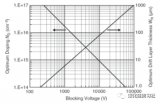

提高抗擊穿電壓:外延層可以設(shè)計成具有較高的抗擊穿電壓,這對于制造高功率和高電壓器件非常關(guān)鍵。例如,在功率器件中,外延層可以提高器件的擊穿電壓,增加安全工作范圍。

4.工藝兼容性和多層結(jié)構(gòu)

多層結(jié)構(gòu):外延生長技術(shù)允許在襯底上生長多層結(jié)構(gòu),不同層次可以具有不同的摻雜濃度和類型。這對于制造復(fù)雜的CMOS器件和實現(xiàn)三維集成非常有幫助。

兼容性:外延生長工藝與現(xiàn)有的CMOS制造工藝高度兼容,容易集成到現(xiàn)有的制造流程中,不需要大幅度修改工藝線路。

小結(jié):外延生長在CMOS硅工藝中的應(yīng)用主要是為了提高晶圓的晶體質(zhì)量,優(yōu)化器件的電氣性能,支持先進工藝節(jié)點,滿足高性能和高密度集成電路的制造需求。通過外延生長技術(shù),可以精確控制材料的摻雜和結(jié)構(gòu),提高整體器件的性能和可靠性。

-

CMOS

+關(guān)注

關(guān)注

58文章

5982瀏覽量

238034 -

晶圓

+關(guān)注

關(guān)注

52文章

5113瀏覽量

129145 -

工藝

+關(guān)注

關(guān)注

4文章

667瀏覽量

29243 -

晶圓襯底

+關(guān)注

關(guān)注

0文章

2瀏覽量

817

原文標(biāo)題:晶圓襯底上為什么要做外延?

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

在超純晶圓上堆疊超高純層的外延技術(shù)

【轉(zhuǎn)帖】一文讀懂晶體生長和晶圓制備

接口電路的必要性

半導(dǎo)體器件為什么要有襯底及外延層之分呢?外延層的存在有何意義?

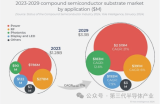

2029年襯底和外延晶圓市場將達到58億美元,迎來黃金發(fā)展期

半導(dǎo)體襯底和外延有什么區(qū)別?

SiGe外延工藝及其在外延生長、應(yīng)變硅應(yīng)用及GAA結(jié)構(gòu)中的作用

在晶圓襯底上生長外延層的必要性

在晶圓襯底上生長外延層的必要性

評論