時鐘是數字電路中所有信號的參考,特別是在FPGA中,時鐘是時序電路的動力,是血液,是核心。沒有時鐘或者時鐘信號處理不得當,都會影響系統的性能甚至功能,所以在一般情況下,在同一個設計中使用同一個時鐘源,當系統中有多個時鐘時,需要根據不同情況選擇不同的處理方法,將所有的時鐘進行同步處理,下面分幾種情況介紹時鐘的同步處理方法。

第一種情況:

當有多個時鐘在同一個數字電路中,且有一個時鐘(Clk)的速率大于其它時鐘兩倍以上。

這種情況最為簡單,在接口部分就必須要對其他時鐘進行同步化處理,將其處理為與Clk同步的時鐘信號。

這樣處理的好處是:

便于處理電路內部時序;

時鐘間邊界條件只在接口部分電路進行處理。

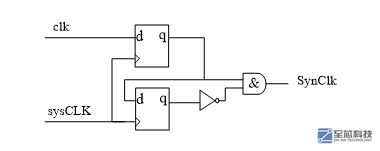

實質上,時鐘采樣的同步處理方法就是上升沿提取電路,經過上升沿提取輸出信息中,帶有了系統時鐘的信息,所以有利于保障電路的可靠性和可移植性。

第二種情況:

當系統中所有時鐘沒有一個時鐘速率達到其他時鐘頻率的兩倍的情況,也就是系統中多個時鐘速率差不多的情況。

這個時候無法滿足采樣定理,所以在接口部分就必須對其他時鐘和數據通過FIFO或者DPRAM進行隔離,并將其他時鐘信息轉換為和系統時鐘同步的允許信號。比如在高速的數據采集系統當中,AD的采集時鐘往往比較高,大于系統時鐘的一半以上,這時候采用同步化處理無法滿足時序設計。

第三種情況:

系統中多個時鐘之間存在數據互相采樣。

對于這種情況,可使用兩級觸發器級聯采樣數據,避免亞穩態發生。

第四種情況:

多級時鐘網絡處理。

所謂多級時鐘網絡是指時鐘經過超過一級的門電路后連到觸發器的時鐘輸入端。

由于時鐘建立-保持時間的限制,FPGA設計中應盡量避免采用多時鐘網絡,在設計中必須要將時鐘網絡進行簡化,盡量采用使能的方式或者其他簡化的電路結構。

-

FPGA

+關注

關注

1643文章

21966瀏覽量

614130 -

數字電路

+關注

關注

193文章

1637瀏覽量

81587 -

異步電路

+關注

關注

2文章

48瀏覽量

11304

原文標題:異步電路中時鐘同步的方法

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

在數字系統中的多種方法解決電磁干擾問題

異步電路中時鐘如何同步的多種方法

異步電路中時鐘如何同步的多種方法

評論