未來系統(例如云數據中心 [DC] 和自動駕駛汽車)需要在計算能力上大幅改進,以支持不斷增多的工作負載以及不斷演進的底層算法。例如,大數據分析、機器學習、視覺處理、基因組以及高級駕駛員輔助系統 (ADAS) 傳感器融合工作負載都在促使計算性能能以低成本、高效的方式實現提升,并且超出現有系統(例如 x86 系統)的極限。

系統架構師正在尋找能滿足要求的新計算平臺。該平臺需要足夠靈活,以便集成到現有的架構中 , 并支持各種工作負載及其不斷演進的算法。此外,這些系統很多還必須提供確定性的低時延性能,以支持實時系統(例如自動駕駛汽車)所需的快速響應時間。

圖形處理單元 (GPU) 廠商非常積極地將 GPU 定位成新時代計算平臺的最佳之選,主要依據其在機器學習訓練的高性能計算 (HPC) 領域取得的成功。在此過程中,GPU 廠商針對機器學習推斷工作負載修改了他們的架構。

然而,GPU 廠商還是忽視了基本的 GPU 架構的局限性。這些局限性會嚴重影響 GPU 以高效、低成本方式提供必要的系統級計算性能的能力。例如,在云端 DC 系統中,對工作負載的需求在一天內會發生很大變化。此外,這些工作負載的底層算法也會發生快節奏變化。GPU 架構的局限性會阻止很多今天的工作負載和明天形成的工作負載映射到 GPU,導致硬件閑置或低效。本白皮書的“GPU 架構的局限性”部分對這些局限性進行了更詳細介紹。

相反,賽靈思 FPGA 和 SoC 具有眾多關鍵屬性,使它們非常適合解決未來系統要求所提出的種種挑戰。

這些獨特屬性包括 :? 針對所有數據類型提供極高的計算能力和效率? 具備極高靈活性,能夠針對多種工作負載將計算和效率優勢最大化? 具備 I/O 靈活性,能方便地集成到系統中并實現更高效率? 具備大容量片上存儲器高速緩存,可提高效率并實現最低時延

本白皮書的“賽靈思 FPGA 和 SoC 的獨特優勢”章節介紹了賽靈思架構的優勢,并與 GPU 架構及其局限性進行對比。

GPU 起源和目標工作負載

GPU 的起源要追溯到 PC 時代,英偉達 (NVidia) 公司聲稱在 1999 年推出世界首款 GPU,但有很多其他顯卡要先于該公司的出品。GPU 是一款全新設計的產品,用來分擔 / 加速圖形處理任務,例如替 CPU 進行像素陣列的陰影和轉換處理,其架構非常適合高并行吞吐量處理 。本質上,GPU 的主要作用是為視覺顯示器 (VDU) 渲染高質量圖像。

多年來,少量非圖形的大規模并行和存儲器相關工作負載是在 GPU(而非 CPU)上實現并且受益良多,例如需要大規模矩陣計算的醫療成像應用。GPU 廠商意識到他們可以將 GPU 的市場延伸到非圖形應用領域,并導致 GPU 的非圖形編程語言(諸如 OpenCL)應運而生。這些編程語言實際上是將 GPU 轉化成了通用 GPU (GPGPU)。

機器學習

最近,能夠良好映射到 GPU 實現方案的工作負載之一就是機器學習訓練。通過充分運用 GPU,顯著縮短了深度神經網絡的訓練時間。

GPU 廠商試圖利用機器學習訓練方面的成功來助推其在機器學習推斷上的發展(部署經過訓練的神經網絡)。隨著機器學習算法和所需數據精度的發展演進,GPU 廠商一直在調整他們的架構以保持自身地位優勢。例如,英偉達在他們的 Tesla P4 產品中提供 INT8 支持。然而,即使是更低的精度,例如二進制和三進制,今天也正在被很多用戶探索。要利用機器學習及其它領域的進步,GPU 用戶必須等待新硬件推出之后購買新硬件。正如本白皮書后面所述,賽靈思 FPGA 和 SoC 的用戶則無需等待或購買新硬件,因為這類產品本身就具有高度的靈活性。

GPU 廠商想使自身成為這個新計算時代的首選計算平臺,機器學習是他們的基礎。但要弄清楚 GPU 是否適合未來系統,還要做更全面的系統級分析,需要考慮 GPU 架構的很多局限性以及系統要求如何隨時間發展演進。

GPU 架構的局限性

本部分將深入研究典型的 GPU 架構,以揭示它的局限性以及如何將它們應用于各種算法和工作負載。

SIMT ALU 陣列

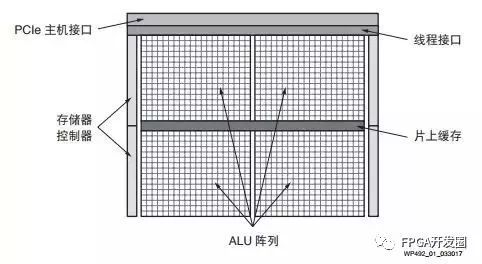

圖 1 給出了典型的 GPU 方框圖。通用 GPU 計算功能的核心是大型的算數邏輯單元 (ALU) 或內核陣列。這些 ALU 通常被認為是單指令多線程 (SIMT),類似于單指令多數據 (SIMD)。

圖 1 :GPU 方框圖

基本原理是將工作負載分成數千個并行的線程。需要大量 GPU 線程來防止 ALU 閑置。然后,對這些線程進行調度,以使 ALU 組并行執行同一(單個)指令。利用 SIMT,GPU 廠商能實現相對 CPU 占位面積更小和能效更高的方案,因為內核的很多資源都可與相同組中的其他內核共享。

然而,顯然只是特定的工作負載(或部分工作負載)能被高效映射到這種大規模并行架構中 。如果構成工作負載的線程不具有足夠的共性或并行性(例如連續工作負載或適度并行工作負載),則ALU 會閑置,導致計算效率降低。此外,構成工作負載的線程預期要最大化 ALU 利用率,從而產生額外的時延。即使有英偉達的 Volta 架構中的獨立線程調度這樣的功能,底層架構也保持 SIMT,也需要大規模并行工作負載。

對于連續、適度并行或稀疏工作負載,GPU 提供的計算功能和效率甚至低于 CPU。例如用 GPU 實現稀疏矩陣計算 ;如果非零元素數量較少,則從性能和效率角度看 GPU 低于或等同于 CPU。

有趣的是,很多研究人員正在研究稀疏卷積神經網絡,以利用很多卷積神經網絡中的大規模冗余[ 參考資料 9]。這種趨勢顯然在機器學習推斷領域向 GPU 提出了挑戰。

稀疏矩陣計算也是大數據分析中的關鍵環節。

包含大量并行計算任務的大多數工作負載也包含一些連續或適度并行元素,意味著需要 GPU-CPU 混合系統來滿足系統性能要求。顯然,高端 CPU 需求會影響平臺的效率和成本效益,CPU 與GPU 之間的通信也會給系統增加潛在瓶頸。

SIMT/GPU 架構的另一個局限性是 ALU 的功能取決于它的固定指令集和所支持的數據類型。

離散數據類型精度支持

系統設計人員正在探索簡化數據類型精度,以此實現計算性能的跳躍式提升,而且不會使精度明顯降低。

機器學習推斷在降低精度方面一馬當先,首先是 FP16,然后是 INT16 和 INT8。研究人員正在探索進一步降低精度,甚至降到二進制 。

GPU ALU 通常原生支持單精度浮點類型 (FP32),有些情況支持雙精度浮點 (FP64)。FP32 是圖形工作負載的首選精度,而 FP64 經常用于一些 HPC 用途。低于 FP32 的精度通常無法在 GPU 中得到有效支持。因此采用標準 GPU 上的更低精度,除了能減少所需存儲器帶寬以外,作用甚微。

GPU 通常提供一些二進制運算功能,但通常只能每 ALU 進行 32 位寬運算。32 位二進制運算存在很大的復雜性和面積需求。在二值化神經網絡中,算法需要 XNOR 運算,緊接著進行種群 (population) 計數。NVidia GPU 只能每四個周期進行一次種群計數運算,這會極大影響二進制計算 [ 參考資料 18]。如圖 2 所示,為了與機器學習推斷空間的發展保持同步,GPU 廠商一直進行必要的芯片修改,以支持有限的幾種降精度數據類型,例如 FP16 和 INT8。例如,Tesla P4 和 P40 卡上的 NVidia GPU 支持 INT8,每 ALU/Cuda 內核提供 4 個 INT8 運算。

圖 2 :英偉達降精度支持

然而,英偉達面向 Tesla P40 上的 GoogLeNet v1 Inference 發布的機器學習推斷基準結果表明,INT8 方案與 FP32 方案相比效率只提升 3 倍,說明要在 GPU 架構中強行降低精度并取得高效結果存在較大難度。

隨著機器學習和其他工作負載轉向更低精度和定制精度,GPU 廠商需要向市場推出更多新產品,他們的現有用戶也需要升級平臺才能受益于這種改進。

通過嚴格的存儲器層級實現軟件定義數據路徑

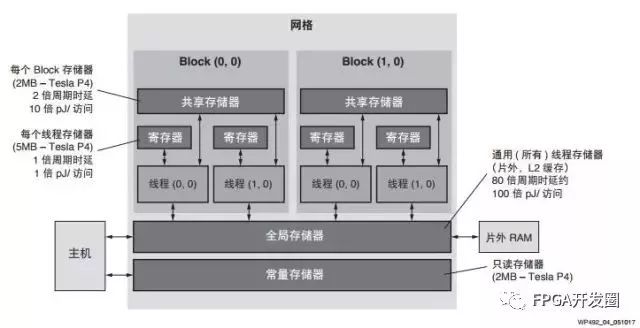

與 CPU 類似,GPU 中的數據流也由軟件定義,并取決于 GPU 的嚴格而復雜的存儲器層級。典型的 GPU 存儲器層級如圖 3 所示。

每個線程在寄存器文件中都有自己的存儲器空間,用以存儲線程的本地變量。少量線程(相同的存儲塊中)可通過共享存儲器通信 ;所有線程都能通過全局或片外存儲器通信 。

如圖 3 所示,與存儲器訪問有關的能耗和時延分別增加 100 倍和 80 倍以上,因為數據需要遍歷存儲器層級——從寄存器文件到全局存儲器。此外,存儲器沖突不可避免,會增大時延,導致 ALU 閑置,致使計算能力和效率降低。

圖 3 :典型的 GPU 存儲器層級

因此,如果實現 GPU 的計算和效率潛能,工作負載的數據流必須準確映射到 GPU 存儲器層級。工作負載要具備足夠的數據局部性,才能高效地映射到 GPU,實際上這樣的工作負載很少。對大多數工作負載而言,當在 GPU 上實現時,實際的計算能力和效率會大打折扣,解決方案的時延也會增加。

機器學習推斷作為量化實例,能清楚反應出這種數據流局限性。GPU 必須批處理,例如 128,以實現高效但時延更長的解決方案。最終,批處理使機器學習處理局部化,但代價是時延增加。GoogLeNet v1 Inference 的 NVidia P40 基準測試結果可清楚地反映出該效應。對于 GoogLeNet v1,網絡因 P40 存儲器帶寬而受計算束縛,因此與批處理有關的存儲器帶寬削減不會產生很大幫助。然而,P40顯然需要 128 批處理以實現 50% 的 GPU 理論性能,會給系統帶來很大時延。

有些情況下,可利用 CPU 對數據進行預處理,以便工作負載更好地映射到 GPU SIMT 架構和存儲器層級,但代價是產生更多 CPU 計算和功耗,抵消了 GPU 的優勢。

有限的 I/O 選項

如“GPU 起源和目標工作負載”部分所述,GPU 的角色是作為協處理器。為了便于與主機通信,GPU以往只有一個硬 PCIe? 接口以及幾個片外 DRAM 接口(例如 GDDR5)。最近幾代產品中,有些 GPU 采用硬接口實現 GPU 到 GPU 通信。仍然需要使用 CPU 來與網絡進行連接以及向 GPU 分配任務,這會增加系統功耗,同時會因 PCIe 的有限帶寬而帶來瓶頸問題。例如,英偉達的 Tesla P40 支持 PCIe 3.0 x16,只能實現 16GB/s 帶寬。

GPU 廠商已經開始構建小型 SoC,例如 NVidia Tegra X1,能夠提供集成 GPU 計算、ARM? 處理器以及一些通用汽車外設(如 HDMI、MIPI、SIP、CAN 和基礎以太網)。這些器件只具備少量計算能力,必須依靠額外的分立 GPU 實現必要的計算能力。然而,分立 GPU 的接口有很大局限性,例如 Tegra X1 僅支持 PCIe 2.0 x4,造成嚴重瓶頸。額外的 SoC 的功耗會進一步降低平臺的效率。

片上存儲器資源

除了時延、效率和吞吐量方面的不利影響,片外存儲器的帶寬要顯著低于本地 / 片上存儲器。因此,如果工作負載需要依靠片外存儲器,不僅片外存儲器的帶寬會成為瓶頸,而且計算資源也會被閑置,從而降低 GPU 提供的計算功能和效率。

因此,更有利的做法是采用大型低時遲、高帶寬片上存儲器。再次以機器學習推斷為例,GoogLeNet 共需要 27.2MB 的存儲器,假設 FP32 方案,這樣沒能提供 GPU,這意味著需要片外存儲器 。很多情況下需采用高昂的高帶寬存儲器 (HBM) 和批處理,以防止內核閑置。如果選擇具有更大型片上存儲器的器件,就能避免 HBM 成本以及額外的時延和功耗問題。

功耗范圍

GPU 廠商在設計板卡和 GPU 時通常要適應 250W 功耗上限,并依靠有效熱管理來調節溫度。針對機器學習推斷市場,英偉達開發了滿足 75W 功耗范圍的器件,例如 Tesla M4 和 P4。即使 75W 也遠超出所允許的系統級功耗和熱范圍。 GPU 的絕對功耗依然是阻礙 GPU 廣泛使用的一大因素。

功能安全性

GPU 源自消費圖形處理和高性能計算領域,不存在功能安全性要求。隨著 GPU 廠商瞄準 ADAS 市場,功能安全性就變成了優先考慮和要求。器件需要全新設計,以確保實現所需的功能安全性認證等級,以便用在 ADAS 系統中。對 GPU 廠商來說這是一個長期學習過程,涉及各個方面,需要新的工具和設備。

賽靈思 FPGA 的起源

1984 年,賽靈思發明了現場可編程門陣列 (FPGA),使用戶能夠在單個器件中編程(重編程)幾乎無限數量的功能。以前,系統設計人員使用很多通用的分立邏輯組件或通過構建高成本的 ASIC 來實現這些功能。

三十多年來,靈活性和可編程性仍然是賽靈思 All Programmable FPGA 和 SoC 的支柱。賽靈思提供的可編程平臺能滿足有線與無線通信、云計算、醫療、汽車、工業以及航空航天與國防領域中多種終端應用的核心需求。所有這些應用都需要強大的計算能力,很多還有非常嚴格的實時要求,例如工業自動化和 ADAS。

通常,FPGA 在使用上的挑戰之一是需要利用硬件描述語言 (HDL)(例如 Verilog 或 VHDL)對其進行編程。最近,賽靈思開發出了 SDSoC ? 和 SDAccel ? 工具,能夠將可編程器件的諸多優勢提供給更廣泛的用戶(例如軟件開發人員和系統架構師);并且構建了更多加速堆棧,使系統設計人員能更快速地實現賽靈思器件的優勢。

賽靈思 FPGA 和 SoC 的獨特優勢

原始計算能力與 GPU 擁護者的說法不同,單個賽靈思器件能提供強大的原始計算能力,例如 Virtex? UltraScale+ ?XCVU13P FPGA 的性能達到 38.3 INT8 TOP/s。最先進的 NVidia Tesla P40 加速卡以基礎頻率運行時提供相似的 40 INT8 TOP/s 原始計算能力,但功耗是賽靈思解決方案的 2 倍多 [ 參考資料 26]。賽靈思器件的靈活性和片上存儲器能針對很多工作負載和應用顯著提高計算能力(詳見 All Programmable 器件靈活性和片上存儲器資源)。

此外,賽靈思器件的靈活性意味著能夠支持各種數據類型精度,例如 FP32、INT8、二進制和定制。例如,針對二值化神經網絡,賽靈思提供 500TOPs/s 的超高二進制計算能力(假設 2.5LUT/ 運算),相當于 GPU 典型性能的 25 倍。有些精度最適合使用 DSP 資源,有些最適合在可編程邏輯中實現,還有些適合將二者結合起來使用。這種靈活性確保器件的計算和效率隨著精度降低而調整,一直到二進制運算。

機器學習領域的大量研究都從計算、精度和效率角度來研究最佳精度。無論最佳點在哪,對于給定工作負載,賽靈思器件的計算能力和效率都能隨之調整,以實現降低精度后的所有優勢。

幾年來,很多 FPGA 用戶實現了脈動陣列處理設計,以便針對多種工作負載實現最佳性能,包括機器學習推斷。為了確保賽靈思 FPGA 和 SoC 用戶能夠在現有的賽靈思器件上針對此類工作負載將可實現的計算能力和效率實現最大化,賽靈思為此提供多種資源。這些資源包括 INT8最優化以及將 DSP 陣列映射到 block RAM 和 UltraRAM 的最高效存儲器層級。如需了解有關這些資源的更多信息,敬請聯系您所在地的賽靈思銷售代表。

為了針對當今的深度學習工作負載提高可用的計算能力和效率,英偉達在 Volta 架構中以 Tensor Core 的形式硬化了類似功能。然而,深度學習工作負載會隨時間演進,因此 Tensor Core 架構也可能需要改變,而且 GPU 用戶需要等待和購買新的 GPU 硬件。

效率和功耗從系統級角度看,計算平臺必須在給定的功率和熱范圍之內提供最大計算能力。為滿足這一需求,計算平臺需要 :? 處于允許的功率范圍內? 能夠在功率預算內將計算能力最大化

賽靈思提供豐富的 All Programmable 器件,這使用戶能選擇與功率和熱范圍最匹配的器件。此外,賽靈思的 UltraScale+ 器件具有低壓模式 (VLOW),能將功耗降低 30%,效率提升 20%。

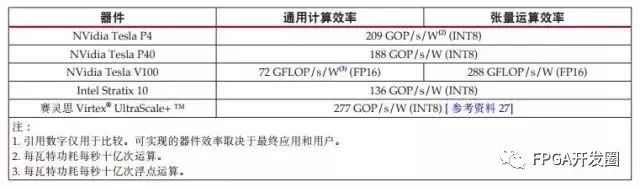

如表 1 所示,賽靈思器件針對固定精度數據類型提供從原始計算角度看最高效的通用計算平臺。這主要是因為賽靈思 FPGA 架構中的處理開銷更低。例如,GPU 需要圍繞計算資源實現更多復雜性,以便實現軟件可編程功能。對于當今的深度學習工作負載的張量運算,英偉達的 Tesla V100 憑借硬化的 Tensor Core 能實現與賽靈思 FPGA 和 SoC 差不多的效率。然而,深度學習工作負載也在快節奏演進,因此無法確定英偉達的 Tensor Core 能夠針對深度學習工作負載保持多久的高效性。顯然對于其他通用工作負載,NVidia V100 也存在效率方面的挑戰。

表 1 :器件效率假設 90% 器件利用率和 80% 有效時鐘周期 (1)

鑒于本白皮書之前介紹的局限性,對于真實的工作負載與系統,GPU 很難接近表 1 中所給出的數字。

賽靈思器件的靈活性及其他優勢,加之賽靈思最新軟件開發堆棧,能確保基于賽靈思的解決方案為大量最終應用和工作負載實現顯著提高的效率。

賽靈思器件的附加優勢——例如靈活性和片上存儲器——能確保賽靈思器件的效率被大量最終應用和工作負載所實現。

All Programmable 器件的靈活性

賽靈思器件經過精心設計,能滿足多種高性能終端系統的計算、效率、成本和靈活性需求。賽靈思將硬件可編程資源(例如邏輯、走線和 I/O)與靈活、獨立的集成內核模塊(例如 DSP Slice 和 UltraRAM)組合在一起,全部構建在領先的工藝技術上,例如臺積電 (TSMC) 的 16nm FinFET 工藝技術,從而達到這種平衡。

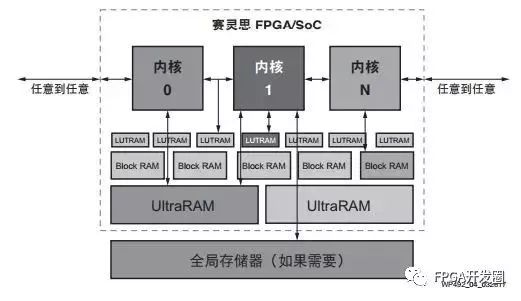

賽靈思器件具備硬件可編程性和靈活性,意味著底層硬件通過配置可滿足給定工作負載的需求。隨后,甚至在運行時也可通過部分重配置功能方便地重新配置數據路徑 [ 參考資料 35]。圖 4 試圖捕捉賽靈思 All Programmable 器件提供的部分靈活性,但是賽靈思器件的真正靈活性無法通過單張圖片來體現。內核(或用戶設計元素)可以直接連接可編程 I/O、任意其它內核、LUTRAM、block RAM 和UltraRAM、外部存儲器等。

圖 4 :All Programmable 數據路徑和任意到任意 I/O

賽靈思器件具有獨特的硬件可編程性,意味著它們不存在特定局限性,例如 SIMT 或固定數據路徑。無論是大規模并行、適度并行、流水線連續或者混合形式,都能獲得賽靈思器件的計算能力和效率。此外,如果底層算法改變(例如機器學習網絡的發展),則平臺也能相應調整。

很多系統和工作負載中都能看到賽靈思器件發揮靈活性優勢。其中一種工作負載就是機器學習推斷。機器學習推斷的趨勢之一是向稀疏網絡過渡。賽靈思器件的用戶已經在利用這種趨勢。英偉達公司本身就是這些用戶中的一個。在最近與英偉達聯合編寫的關于語音辨識的一篇文章中,通過使用賽靈思FPGA,相對 CPU 實現了 43 倍速度提升和 40 倍效率提升,相對 NVidia GPU 實現了 3 倍速度提升和11.5 倍效率提升。可編程數據路徑還減少了賽靈思 FPGA 批處理需求。批處理是系統的時延 vs 實時性能的重要決定因素。

從大數據角度看,賽靈思器件的靈活性也展現出明顯優勢。賽靈思 FPGA 在處理 SQL 工作負載時非常高效和快速,包括具有復雜數據(例如可變長度字符串)的情況。百度利用基于賽靈思 Kintex?UltraScale ? KU115 器件的加速卡實現了 25 倍以上的提速。該加速卡的功耗僅 50W。百度該解決方案的效率比 GPU 方案快 4 倍。對于文本和圖案匹配工作負載,研究表明基于賽靈思的RegEx 方案比 CPU 方案快 14.5–18 倍,比 GPU 方案快了將近 3 倍。

基因組分析是另一個切實的實例。有人已經利用 GPU 來加速基因組分析,可相較于 Intel Xeon CPU 方案提速 6–10 倍。不過,賽靈思 FPGA 的提速效果要高得多,相較于同等 CPU 可提速 80倍 。

賽靈思器件的靈活性還使其成為云服務提供商的理想選擇,可作為計算平臺即服務的一部分。多種類型的軟件即服務都可以利用賽靈思器件的優勢。

最后,對于正在努力研發自動駕駛功能的汽車系統設計人員來說,賽靈思器件的靈活性能夠為他們提供可擴展的平臺,用以滿足完全自動駕駛道路上的各種美國汽車工程師學會 (SAE) 標準。如需了解關于SAE 標準的更多信息 , 敬請訪問 SAE 網站。賽靈思器件可以高效處理來自各種源頭的傳感器數據,例如雷達、照相機和超聲波,同時保持系統的實時 / 時延目標。

任意到任意 I/O 靈活性

除了器件計算資源的靈活性,賽靈思的任意到任意 I/O 靈活性能夠確保器件可無縫集成到現有的基礎架構,例如直接連接到網絡或存儲設備,無需使用主機 CPU。I/O 靈活性還允許平臺針對基礎架構的變化或更新進行調整。

如需了解關于賽靈思 UltraScale 架構器件的更多詳情,請參閱不斷擴大的賽靈思大型白皮書庫。

片上存儲器

如表 2 所示,賽靈思器件提供業界領先的靈活、高帶寬、低時延的 500Mb 片上存儲器。如此大的片上存儲器緩存意味著工作負載的很大一部分存儲器要求都能通過片上存儲器來滿足,從而減小外部存儲器訪問帶來的存儲器瓶頸問題,以及高存儲器帶寬解決方案(例如 HBM2)的功耗和成本問題。例如,針對大多數深度學習網絡技術(例如 GoogLeNet)的系數 / 特性圖都可存在片上存儲器中,以提高計算效率和降低成本。

表 2 :器件片上存儲器大小

封裝內的 HBM

針對需要高帶寬存儲器的情況,賽靈思在部分 Virtex UltraScale+ 器件中提供 HBM。除了封裝內 HBM堆棧的 460GB/s 存儲器帶寬,賽靈思 HBM 存儲器控制器還增加更大的靈活性,以便將工作負載高效映射到器件和可用存儲器帶寬,將效率和計算效率最大化。

功能安全性

賽靈思長期以來能夠滿足各種功能安全性,包括工業自動化以及最近的 ADAS。賽靈思工具和器件經過重新設計,以便支持功能安全性應用,并達到相應認證等級。

因此,多家汽車制造商在安全關鍵型 ADAS 應用中采用 Zynq?-7000 All Programmable SoC 量產器件。Zynq UltraScale+ MPSoC 還進一步擴大對功能安全應用的支持。

結論

系統設計人員在這個新的計算時代面對不同選擇。賽靈思 FPGA 和 SoC 為系統設計人員提供最低風險,幫助其滿足未來系統的核心要求與挑戰,同時提供足夠的靈活性以確保平臺在未來不會落伍。

在深度學習領域,UltraScale 架構中的 DSP 架構內在的并行性能夠針對具有可伸縮 INT8 向量點積性能的神經網絡加強卷積和矩陣乘法計算量。這能為深度學習推斷實現更低時延。快速 DSP 陣列、最高效的block RAM 存儲器層級以及 UltraRAM 存儲器陣列可實現最佳功率效率。

現在,利用開發套件,以及多種設計輸入工具,例如 HLS、SDSoC 和 SDAccel 工具,用戶可發揮賽靈思器件的諸多優勢。

-

賽靈思

+關注

關注

33文章

1795瀏覽量

132098 -

gpu

+關注

關注

28文章

4907瀏覽量

130610 -

機器學習

+關注

關注

66文章

8490瀏覽量

134019 -

英偉達

+關注

關注

22文章

3917瀏覽量

93068

原文標題:Xilinx全可編程器件:出色的計算密集型系統開發平臺

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

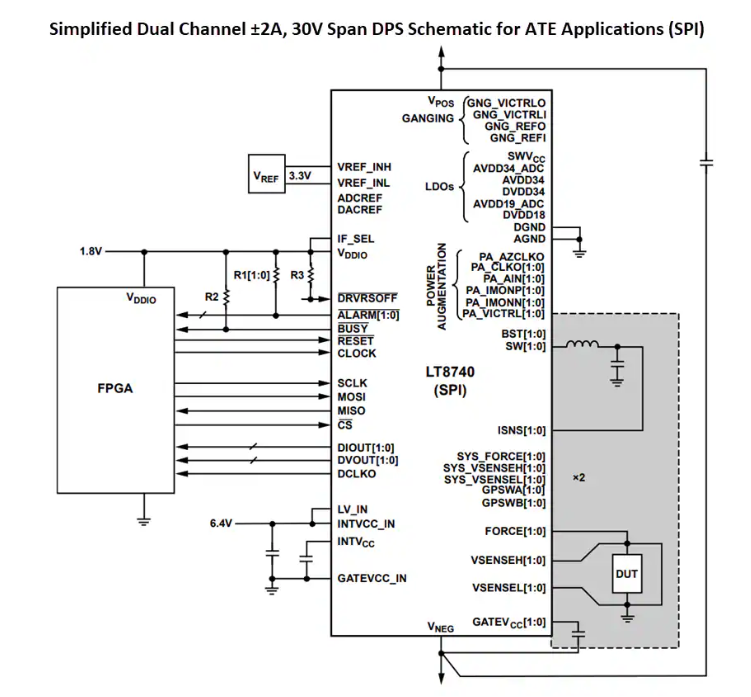

Analog Devices Inc. LT8740可編程器件電源(DPS)數據手冊

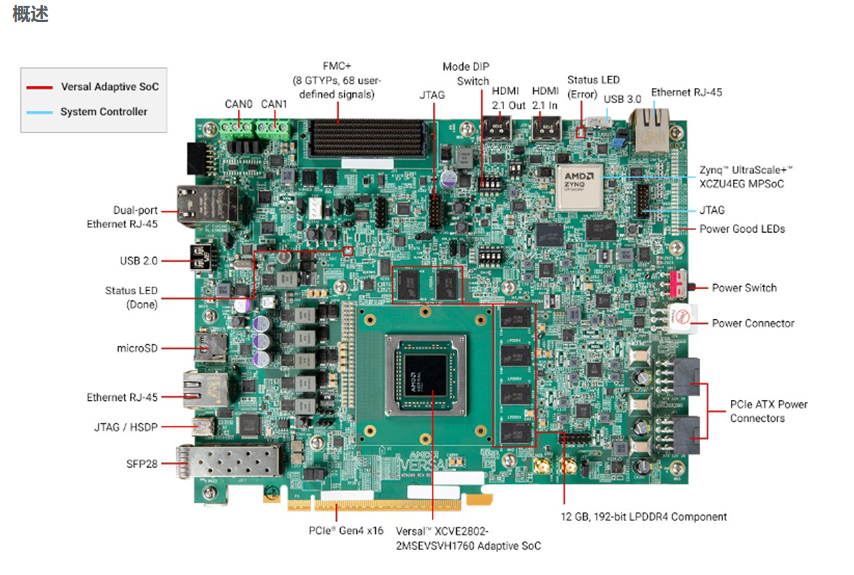

面向AI與機器學習應用的開發平臺 AMD/Xilinx Versal? AI Edge VEK280

可編程電子負載的原理及主要應用

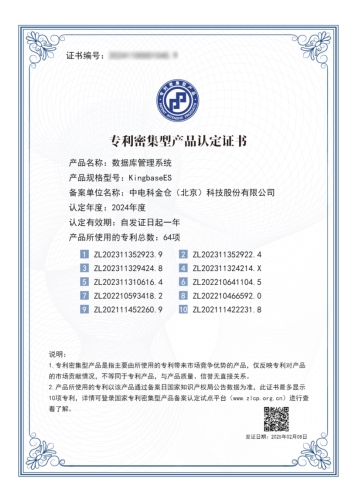

金倉數據庫入選《2024年度專利密集型產品名單》

可編程交流負載標準

人員定位系統對生產密集型企業的重要意義

廣和通端側AI解決方案驅動性能密集型場景商用型場景商用

解析全硅可編程 CMOS 振蕩器 SWPM101 系列(0.01 至 212.5 MHz)的卓越特性

可編程晶振都有什么頻率的呢?分享3個挑選可編程晶振的技巧

出色的計算密集型系統開發平臺-Xilinx全可編程器件

出色的計算密集型系統開發平臺-Xilinx全可編程器件

評論